作者:电子工程师小李

1)锁存器

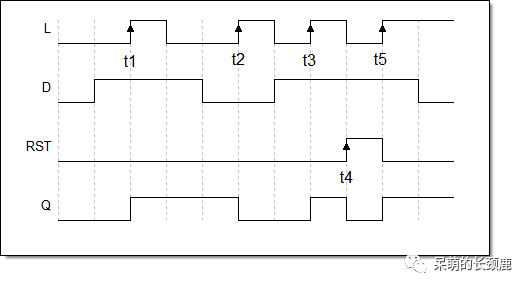

锁存器(latch)是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

简单地说,锁存器有两个输入,一个是有效信号EN,一个是输入数据信号DATA_IN,有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程。

2)触发器

触发器(Flip-Flop,简写为FF)也叫双稳态门,又称双稳态触发器,是一种可以在两种状态下运行的数字逻辑电路。触发器一直保持它们的状态,直到它们收到输入脉冲,又称为触发。当收到输入脉冲时,触发器输出就会根据规则改变状态,然后保持这种状态直到收到下一个触发。触发器对脉冲边沿敏感,其状态只在时钟脉冲的上升沿或下降沿的瞬间改变。

3)锁存器与触发器的区别

锁存器和触发器是具有记忆功能的二进制存储器件,是组成各种时序逻辑电路的基本器件之一。其区别在于,latch同其所有的输入信号相关,当输入信号变化时latch就变化,没有时钟端;flip-flop受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。当然,因为latch和flip-flop都是时序逻辑,所以输出不但同当前的输入相关还同上一时间的输出相关。

(1)latch由电平触发,非同步控制。在使能信号有效时latch相当于通路,在使能信号无效时latch保持输出状态。DFF由时钟沿触发,同步控制。

(2)latch对输入电平敏感,受布线延迟影响较大,很难保证输出没有毛刺产生,而DFF则不易产生毛刺。

(3)如果使用门电路来搭建latch和DFF,则latch消耗的门资源比DFF要少,这是latch比DFF优越的地方。所以,在ASIC中使用latch的集成度比DFF高,但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个LE才能实现。latch是电平触发,相当于有一个使能端,且在激活之后(在使能电平有效的时候)随输入而变化。在非使能状态下latch保持原来的信号,这就可以看出其和flip-flop的差别,其实很多时候latch是不能代替FF的。

(4)latch将静态时序分析变得极为复杂。

一般的设计规则是在绝大多数设计中避免产生latch。latch会让设计的时序混乱,并且它的隐蔽性很强,很难检查。latch最大的危害在于不能过滤毛刺,这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch。

有些地方没有时钟,也只能用latch了。比如现在将一个clk接到latch的使能端(假设是高电平使能),这样需要的setup时间,就是数据在时钟的下降沿之前需要的时间,但是如果是一个DFF,那么setup时间就是在时钟的上升沿需要的时间。这就说明如果数据晚于控制信号的情况下,只能用latch,这种情况就是,前面所提到的latch timing borrow。基本上相当于借了一个高电平时间。也就是说,latch借的时间也是有限的。

编辑:hfy

-

锁存器

+关注

关注

8文章

744浏览量

41034 -

触发器

+关注

关注

14文章

1677浏览量

60392

发布评论请先 登录

相关推荐

锁存器与触发器的区别

锁存器与触发器的区别

评论