PIPE 接口上的数据在 Gen3 的速度下被加密。当调试 PCIe 问题时,能在 PCIe 链接上查看各个包会很有帮助。

若要实现此目的,用户需拥有协议链接分析器。由于其成本较高,能接触到此等设备的用户不多。随协议链接分析器提供的包分析工具很广泛,可对链接流量进行深入分析。

赛灵思 UltraScale+ 器件的 PCIe® Express Gen3 IP 集成块有一个功能,可让您集成一个解扰器模块,以便解密在 PIPE 接口上被加密的数据。尽管它不能提供与协议链接分析器相同数量的分析数据,但它可以在识别潜在问题方面提供帮助,而且在大部分情况下可帮助追踪问题的根本原因。

本文将详细介绍如何通过识别来自链路并进入 PCIe IP 的不同类型的 PCIe 包来分析解扰器模块的输出数据。

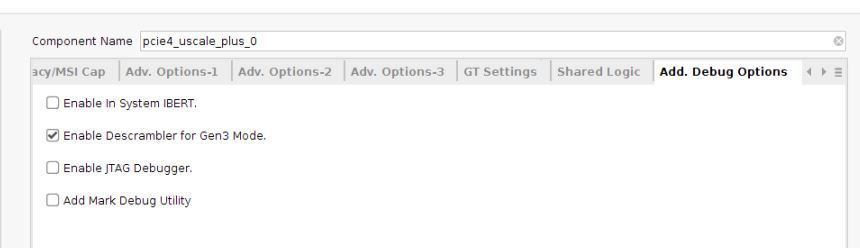

解扰器模块在 PCIe IP 配置 GUI 中被使能,具体如下:

解扰器模块只在 Gen3 模式中被支持。

如果复选框变成灰色,要确保配置 GUI 的“Basic”标签中的链接速度被设为 8.0 GT/s。如果该选项不可用,请将“Basic”标签中的“Mode”设为“Advanced”。

为了追踪 PIPE 接口上有效 PCIe 包的起始点,该接口提供了两种信号:*_sync_header 和 *_start_block。

为了确认 rx_data 上的数据是否为有效包,请检查以下各项:

- *_data_valid 已被有效

- *_start_block 已被有效

-

*_sync_header 为“1”或“2”。

- 如果该值是“1”,则表示是“Ordered Set”的起始点。

- 如果该值是“2”,则表示是 TLP 或 DLLP 包的起始点。

被解扰的数据分析也可在仿真中进行。

以下的波形图来自与 IP 一起生成的 Gen3 示例设计的仿真。

上文波形图中所示的 FF00FF00 就是 EIEOS。

被解扰信号上的第一个包将是 EIEOS。

如前文所述,*_start_block 必须有效,而且下文波形图中所示的 *_sync_header 信号应为“1”。

一旦所有均衡状态都已完成,在进入 L0 状态之前,您应该看到 555555E1。

这就是 SDS(数据流起始点)。一旦您看到了 SDS,则意味着有序集交互已完成。接口上的下一个包类型将是初始流量控制信用,即,我们应在接口上看到 DLLP 包。

在下文的波形图中,DLLP 包为 InitFC1-P。

DLLP 包格式共有四种:

- ACK 或 Nak DLLP 包格式

- 功耗管理 DLLP 包格式

- 流量控制 DLLP 包格式

- 供应商特定 DLLP 包格式

每一种 DLLP 包的长度都是 6 个符号。 有关解码 DLLP 包内容的信息,请参阅 PCI Express 规范。在下文的波形图中,“60”是 InitFC-Cpl(Cpl 代表 completion)。“50”是 InitFC-NP(NP 代表 Non-Posted)。

UpdateFC-P 以“80”开始。被解扰数据中的更新值为十六进制,因此需要将其转化为十进制,以便获得可用信用的准确数字。

有序集总是按通道来的。每条通道都有其自己的有序集。 DLLP 和 TLP 被跨通道分配;每条通道一个字节。

DLLP 只在 lane-0、lane-4 或 lane-8 中开始,即,F0 只能在 lane 0、4 或 8 上。TLP 可在任何通道上开始。

TXRATE 表示链路运行的速度。向 Gen3 速度的过渡在“Recovery.Speed”(0C)LTSSM 状态中发生,如以下波形图所示。

在 L0 状态之前以 Gen1/Gen2 速度运行的包未被加扰,它仅在 Gen3 速度下被加扰。在 PIPE 接口上以 Gen1/Gen2 速度运行的有序集可被直接读取。但是,所有速度的所有内容在 L0 状态中都会被扰码。下面的波形图显示了在 Gen1 速度时的捕获。

在这里,“4A”系指其 TS1 有序集。只有在速度如 TXRATE 所示变化至 Gen3 时才需要解扰器模块。

下列波形图中的 AAAAAAAA 表示一个 SKP 有序集。

E1 表示 SKP_END 符号的定义详见如下所示的 PCIe 规范。

下面的波形图显示了在 Gen3 链接上的一个 TS1 有序集。所示的“1E”表示在 Gen3 速度时的一个 TS1 有序集。

下面的波形图显示了每条通道中的一个 TS1 有序集。它不会跨越多条通道。它在所有通道上都相同,只是通道号不同。在下面的波形图中,通道号分别为 00 和 01。

这里的“0E”是 Symbol-4。Symbol-4 在规范中的定义如下:

0E= 0000_1110。当我们将这些位映射到规范中的 Symbol-4 描述上时,它表示 Gen3 速度得到了支持。

Symbol-6 在 LTSSM 所处的不同状态中具有不同含义。在如下所示的波形图中,LTSSM 为“28”,则意味着它位于 phase-0 中。

Symbol-6 为 20,即 001_0000。由于它在 phase-0 中,则位 1:0 被设为“00”。

下面的波形图显示了一个完整的 TS1 有序集。

下面的波形图显示了设置为 Gen3 速度的一个 TS2 有序集。“2D”表示它是一个 TS2 有序集

至此,我们已讨论了有关有序集和 DLLP 的内容,那么现在我们来看一下如何在 PIPE 接口上识别 TLP。

每个 TLP 都以 STP(TLP 包起始点)标识开始。因此,在解扰器中查找具有 *_start_block = 1 和 *_sync_header= 2 的任何“nF”。

每个 STP 标识都是 4 个符号并表示 TLP 的开始。

STP 字段的定义详见下图所示:

以下是 MemWr(存储器写入 TLP)的示例。请注意,这是一个 x4 链接,因此所有内容都被跨越分配。下面的波形图取自示例设计仿真。

该波形图显示了来自主机测试平台而通过 PCIe 硬块的 CQ 接口进入用户逻辑的存储器写入传输事务。该传输事务在 PIPE 接口上具体理解如下:

开始从 LSB 读取:

DW0 = ClkCycle0-Byte0 (Lane-0 to Lane-3) -> “6F-80-20-1D” -> STP token DW1 = Header starts here -> ClkCycle0-Byte1 (Lane-0 to Lane-3) -> “40-00-00-01” -> Indicates Fmt/Type = 0x40 which is a 3DW MemWr request, Length = 1 DW2 = ClkCycle0-Byte2 (Lane-0 to Lane-3) -> "00-00-00-0F” -> "0000- ReqID, Tag – 00, 1st DW Byte Enable = "F" DW3 = ClkCycle0-Byte3 (Lane-0 to Lane-3) -> “00-00-00-10” -> Address = 'h10 DW4 = ClkCycle1-Byte0 (Lane-0 to Lane-3) -> “04-03-02-01” -> Payload (Byte0 to Byte3, 01-> MSB, 04-> LSB)

编辑:hfy

-

存储器

+关注

关注

38文章

7116浏览量

161894 -

赛灵思

+关注

关注

32文章

1794浏览量

130489 -

PCIe

+关注

关注

13文章

1078浏览量

80694 -

GUI

+关注

关注

3文章

605浏览量

38754

发布评论请先 登录

相关推荐

【正运动】高速高精,超高实时性的PCIe EtherCAT实时运动控制卡 | PCIE464

AD采集卡设计原理图:630-基于PCIe的高速模拟AD采集卡

体验紫光PCIE之使用WinDriver驱动紫光PCIE

全爱科技Atlas200I A2 AI加速模块-FPGA PCIE接口验证平台

基于FPGA的PCIE I/O控制卡通信方案

项目承接案例:PCIE采集系统 前端图像或ADC数据采集,通过PCIE传输至PC。可实现PCIE 2.0 x#

什么是PCIe?

VIAVI Xgig® 1000 PCIe 分析仪功能强大的 PCIe 应用程序监控和分析系统

浅谈PCIe包分析解扰器模块的输出数据

浅谈PCIe包分析解扰器模块的输出数据

评论