作者:猫叔

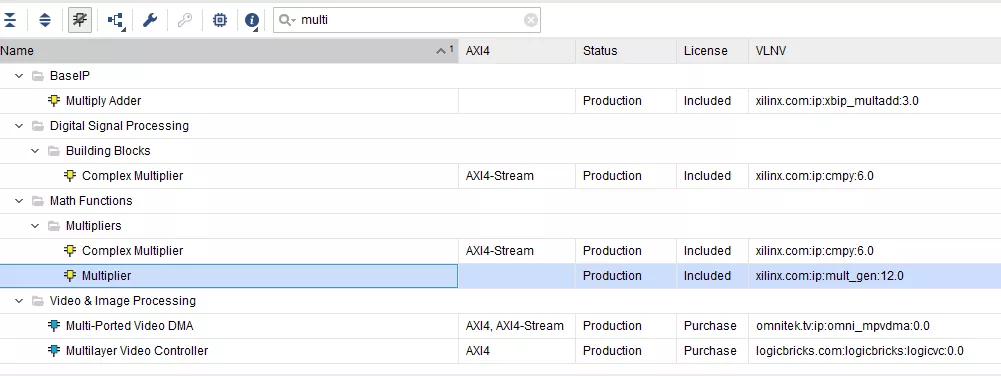

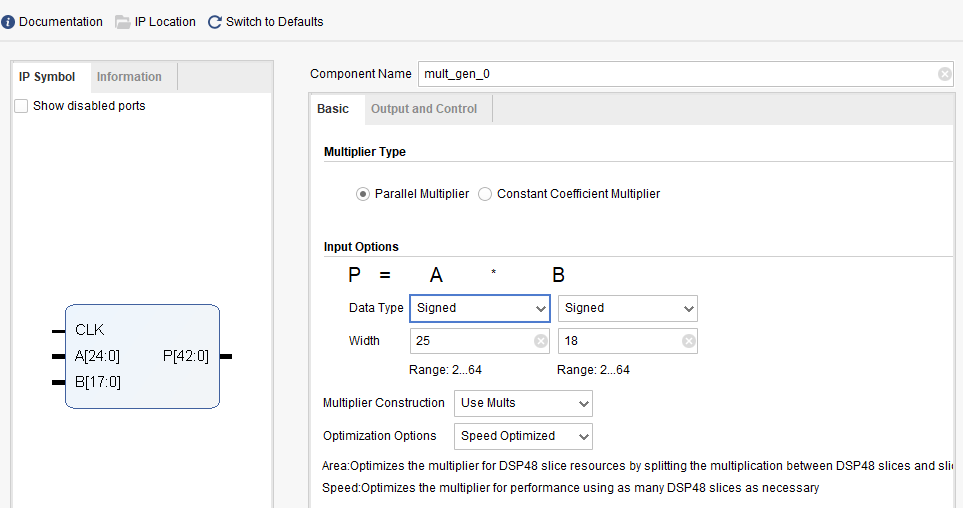

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

当然,我们也可以直接使用*符合来进行乘法,对于无符号的乘法

reg [7:0] ubyte_a; reg [7:0] ubyte_b; (* use_dsp48="yes" *) output reg[15:0] u_res; always @ ( posedge clk ) begin if(rst) u_res <= 'b0; else u_res <= ubyte_a * ubyte_b; end

有符号乘法可以在Verilog中使用signed来标注。

reg signed [7:0] byte_a;

reg signed [7:0] byte_b;

(* use_dsp48="yes" *)

reg signed [15:0] res;

always @ ( posedge clk ) begin

if(rst)

res <= 'b0;

else

res <= byte_a * byte_b;

end

当然我们也要理解有符号数乘法的原理,其实就是扩位乘法,把高位都补充为符号位。

有符号数乘法:

reg [7:0] ubyte_a;

reg [7:0] ubyte_b;

(* use_dsp48="yes" *)

reg [15:0] res_manul;

always @ ( posedge clk ) begin

if(rst)

res_manul <= 'b0;

else

res_manul <= {{8{byte_a[7]}},ubyte_a} * {{8{ubyte_b[7]}},ubyte_b};

end

关于乘法输出的位宽,我们知道,两个8bits的无符号数乘法,结果的位宽是16bits,但对于两个8bits有符号数的乘法,只要两个数不同时为-128,即二进制0b1000_0000,那么输出结果的高两位都是符号位,我们只需要取低15bits即可。因此,如果我们可以保证两个输入的乘数不会同时为有符号数所能表示的负数最小值,那么乘法结果的高两位都是符号位,只取其中一位即可。

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

544文章

7680浏览量

344319 -

FPGA

+关注

关注

1601文章

21294浏览量

593030 -

乘法器

+关注

关注

8文章

191浏览量

36580

发布评论请先 登录

相关推荐

Versal FPGA中的浮点计算单元DSPFP32介绍

Versal FPGA中最新的DSP原语DSP58,它在最新的DSP48版本上已经有了许多改进,主要是从27x18有符号乘法器和48位后加法器增加到了27x24和58位。

乘法器AD734上电后发热严重,数据漂移的原因?怎么解决?

乘法器AD734上电后发热比较严重,输入与地短接的情况下,输出数据不稳定,用数据卡采集可以看到明显的漂移,[size=13.3333px]采用的是芯片手册上的最基本的乘法电路,这种现象的原因是什么,是PCB设计的问题吗。

发表于 12-15 06:44

pipeline ADC的实现原理及基本结构(1)

假设单级的分辨率为n,它由S/H电路、n位的子ADC、n位的子DAC、减法器以及乘法器构成,一般也将n位的子DAC、减法器以及乘法器统称为MDAC(multiplying DAC)。

用AD835的Datasheet上的电路做了一个乘法器电路,出现两个直流偏置的原因?

我用AD835的Datasheet上的电路做了一个乘法器电路,但是测试的时候发现,当输入信号大于峰值大于600mV左右的时候,1和8两个引脚端就会突然出现两个直流偏置,约-1.5V,请问有人用该芯片出现过这种问题吗?求指教。。。。

发表于 11-27 06:43

求助,关于二象限乘法器AD539的一些疑问

各位,请教乘法器的一些问题:

1.二象限乘法器AD539中控制通道Vx只能输入正信号,但是否只能为直流电平(用做电压控制放大器)?

2.如果控制通道Vx输入交流信号,理论上是否应该做偏置,使之在

发表于 11-22 07:48

用AD835乘法器做的一个电路,当X和Y的频率相同时,输出的波形问题求解

请教大神,我用AD835乘法器做的一个电路,当X和Y的频率相同时,相乘时输出是正弦波,但是当频率不相同时输出波形就会变为这种波形,请问有人知道是什么问题??谢谢!附件里有一张图是同频率相乘,波形是对的,另一张是不同频率相乘的图!

发表于 11-22 06:54

集成电路中低功耗乘法器的实现与设计方案

限度的低功耗效果。本文紧跟市场发展动向,从以上应用角度出发,着力研究集成电路设计中小数乘法器的前端低功耗算法以及实现技术,并且改进了现有低功耗设计技术的一些不足之处。

发表于 09-19 07:42

FPGA中乘法器的原理分析

FPGA中乘法器的原理分析

评论