一.高速串行传输兼容设计的三个基础

作为与高速串行传输兼容的设计,可以抑制反射,减少传输损耗并抑制噪声,

电路板的设计遵循以下三个基本准则:

1.差分布线的阻抗控制;

2.最小化差分布线长度;

3.尽可能使差分对内的布线长度匹配。

关于反射的抑制,不仅可以通过优化设计规格来控制上述布线,而且可以控制通孔(通孔)的阻抗,并且在数字消费设备中变得越来越流行。必须考虑安装区域的影响来优化连接器,并充分了解电缆的实际特性。例如,如果连接器的安装区域的图案设计不正确,在许多情况下会存在额外的寄生电容,并且阻抗会下降和反射,这会恶化传输波形,因此必须对该区域进行优化。

此外,对于需要在高速串行传输中进行仿真的区域,我们认为它是5 Gbps或更高。这是因为5 Gbps PCI Express规范指出必须在模式设计阶段使用仿真进行确认,而且在许多情况下,还会听到实际问题。

二.高速串行传输的回波损耗标准

对于高速串行传输,可能会有一些标准,其中包含回波损耗和反射量的规范。

通用接口的典型示例是硬盘SSD串行ATA和广播,安全性和医学成像领域的SDI。

在这些情况下,半导体与外部I / O连接器之间的图案设计将决定通过/失败。这是需要PCB设计技术的领域。

例如,用于串行ATA的表面安装连接器趋于具有较大的寄生电容,这会降低阻抗并降低性能。

作为对策,通过部分地去除基板的表面层上的安装焊盘下方的实心平面以减小寄生电容,可以使配线的特性阻抗相同并且改善特性。积累专门知识对于这种优化很重要,但是为了满足广泛的需求,也可以使用可以从电路板设计信息中高精度提取特征的软件。

三.总结

为了支持高速串行传输,除了控制差分布线的阻抗,最小化差分布线长度并尽可能确保差分对内的布线长度的基本要素外,安装位置的通孔和局部阻抗控制很重要。这在存在回波损耗标准的SDI接口中尤为明显,并且使用仿真的电路板设计被认为是必不可少的。

-

电路板设计

+关注

关注

1文章

125浏览量

16308 -

PCB设计

+关注

关注

392文章

4572浏览量

83216 -

PCB布线

+关注

关注

19文章

459浏览量

41649 -

华秋DFM

+关注

关注

20文章

3483浏览量

3907

发布评论请先 登录

相关推荐

第三方兼容万兆单模光模块SFP-10G-LR:高速长距离数据传输性价比之选

关于高速串行信号隔直电容的PCB设计注意点

SerDes技术优势明显,解决车内高速传输难题

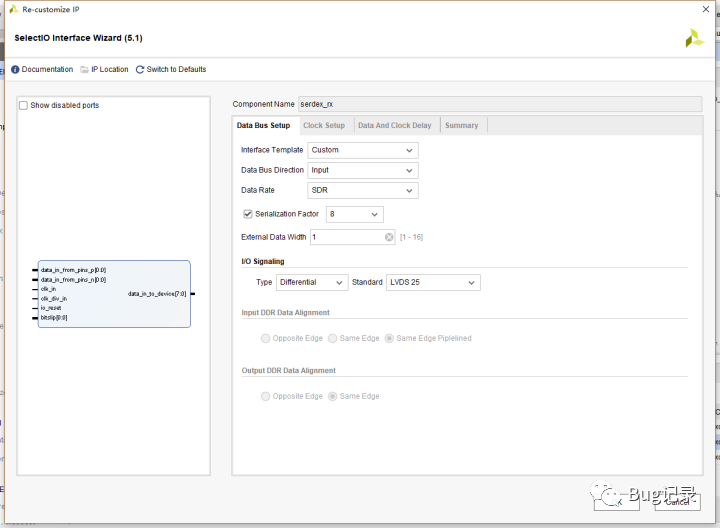

基于FPGA的高速串行传输系统设计

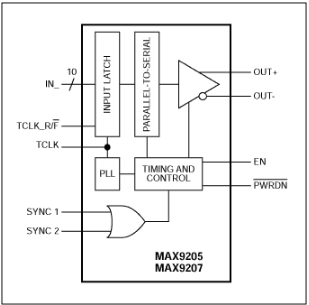

SC5103接口可pin对pin兼容TLK1501

使用高速微型的串行端口

LVDS串行器的信号完整性与传输速率和电缆长度的关系

高速串行传输兼容设计的设计准则

高速串行传输兼容设计的设计准则

评论