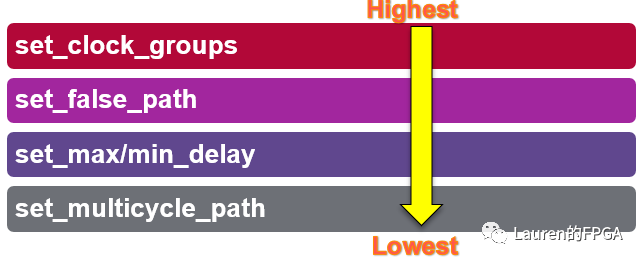

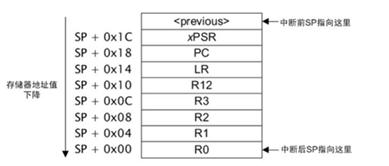

约束的优先级

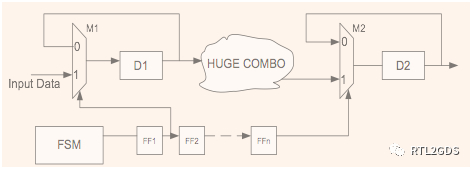

XDC描述的时序约束是有优先级的,尤其是涉及到时序例外的约束,如set_clock_groups、set_false_path、set_max_delay和set_multicycle_path。如果这些约束施加到同一条路径上,那么其优先级如下图所示。

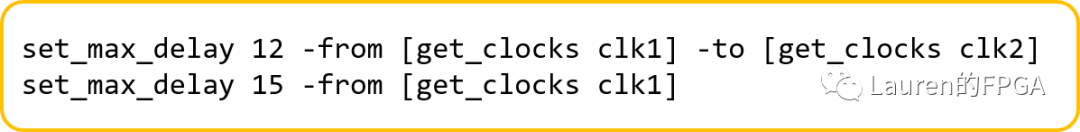

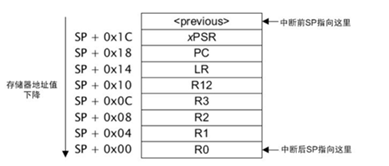

对于同类型的约束,遵循的原则则是越具体的优先级越高。如下图所示,都是set_max_delay约束,且都使用了-from和-to,显然第一条约束比第二条约束更具体,因此,第一条约束优先级高于第二条约束,第二条约束将被部分覆盖。这里部分覆盖的含义是凡是从clk1到clk2的路径,都遵守最大延迟为12ns的要求,但如果设计中存在从clk1到clk3的路径,则仍然按15ns进行约束。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Delay

+关注

关注

0文章

10浏览量

10759 -

xdc

+关注

关注

1文章

23浏览量

5869 -

华秋DFM

+关注

关注

20文章

3481浏览量

3896

原文标题:如何使set_max_delay不被覆盖

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

set_output_delay的本质是什么?浅谈set_ouput_delay时序

set_output_delay是对模块output信号在模块外部延迟的约束,本质上EDA工具会根据约束调整内部器件(UFF0)的类型,摆放位置以及组合逻辑(C1)以满足约束要求,即EDA工具保证模块DUA的UFF0的Tclk2q+Tc1延时能够满足约束要求。

介绍基本的sdc时序特例

今天我们要介绍的基本sdc是 **时序特例** ,也就是我们常说的Path exception。针对一些路径需要的一些特殊设定,常用的有set_false_path, set_multicycle_path, set_max_delay

PCBA加工焊点拉尖产生的原因及解决办法

一站式PCBA智造厂家今天为大家讲讲什么是PCBA加工焊点拉尖?PCBA加工焊点拉尖产生原因及解决办法。接下来为大家介绍PCBA加工焊点拉尖产生原因及解决办法。

set_max_delay被覆盖的解决办法

set_max_delay被覆盖的解决办法

评论