引言

随着嵌入式系统产品的发展,其功能趋向系统化、复杂化,不同场合和具体应用对产品的升级维护提出了更多的需求。厂商针对这一问题普遍采用。Bootloader引导应用程序结构的嵌入式软件,在产品升级和维护过程中只需提供升级程序包由Bootloader在升级模式下更新产品的应用程序,即可快捷地实现产品升级。

一直以来,嵌入式软件的安全和知识产权保护是厂商面对市场竞争着重关心的焦点。嵌入式系统处理器的有限硬件资源和高效率要求使得其难以应用复杂和大运算量的加密算法,对代码的保护更多依赖于硬件,这往往具有很多潜在的安全隐患。本文就.Bootloader引导应用程序结构的软件在STM32F103RB芯片上应用时,遭到篡改攻击后所面临的代码泄漏风险进行研究和验证,并提出了改进Bootloader的安全设计方案,加强代码的安全性。

1 篡改攻击风险研究

1.1 研究的意义

嵌入式系统产品的开发往往成本高、开发周期长,一旦产品中的嵌入式软件被抄袭或盗窃都将给厂商带来巨大的损失。随着嵌入式处理器设计技术的发展,对片内Flash中的代码保护也日渐完善。芯片在保护状态下,可以完全禁止通过调试接口或SRAM中运行的程序读取Flash内容,但产品阶段保存在 Flash中的代码运行时对自身的读取是允许的,如果非法使用者通过特殊手段篡改了Flash中的部分代码为非法读取程序,并使之在Flash中成功运行,将使产品代码发生部分泄漏,这就是产品面临的篡改攻击风险。针对这一风险的研究在实际应用中显得十分重要。

ST公司推出的STM32系列微处理器采用ARM新一代Cortex-M3内核,其中增强型的STM32F103RB具有72 MHz主频、20 KB片内SRAM、128 KB片内Flash以及丰富的接口资源,可以很好地满足广泛的嵌入式产品的应用需求。较低的芯片价格和简单的开发方式使之应用前景非常广阔,对该芯片上代码的安全研究也具有深远意义。

1.2 风险研究

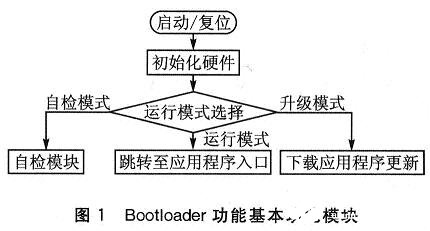

Bootloader引导应用程序结构的嵌入式软件可以满足产品功能升级和维护的需求,在实际应用中被厂商普遍采用。Bootloader程序是在系统上电复位后在Flash中首先执行的一小段代码,其基本功能模块如图1所示。

对于具有Bootloader引导应用程序结构的嵌入式软件,Bootloacler部分和应用程序是相对独立的。产品有了升级版本后,用户可以得到产品和升级程序包。在对产品的篡改攻击中,一旦Bootloader代码泄漏,非法使用者通过升级模式更新应用程序部分,将可以复制产品的全部软件代码,这就使得产品被抄袭的潜在风险急剧增大。在STM32F103RB上进行的实验也证明了抄袭的可能性。

2 基于STM32F103RB芯片的风险验证

STM32F103RB芯片对片内Flash的保护通过特殊位置的Option Bytes读写保护控制字实现。读、写保护有效时将禁止调试接口和SRAM中运行的程序对Flash读、写操作。芯片特殊设计为:去除读保护时,首先整片擦除片内Flash,从而销毁产品软件代码;写保护的去除并不影响Flash中代码的完整性;读保护有效时,Flash的前3片区写保护自动有效,防止中断向量表被非法修改。

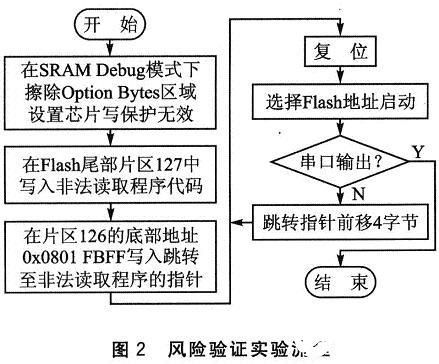

实验在STM32F103RB的开发板上进行,在前3片区写入Bootloader程序代码后,利用升级程序包将应用程序下载至应用程序片区。检验程序功能正常后置芯片读保护和所有片区写保护有效,从而得到产品阶段的芯片。对芯片的篡改攻击风险验证实验流程如图2所示。

用于篡改攻击的软件包括非法读取Flash内容并通过串口输出的程序和用于跳转到非法读取程序的指针。篡改攻击的实现原理是芯片的读、写保护只包括主Flash区域,对Option Bytes区域的擦除操作可以去除无自动写保护片区的写保护状态,而读保护仍然有效。在SRAM中运行的程序可以使芯片转变为代码完整而应用程序区域无写保护的状态。一般情况下,产品为了保持升级的空间,软件没有占据整个Flash空间且采取自顶向下的顺序摆放。为了最大程度保持原有应用程序,实验中将非法读取程序写入Flash的尾部片区,并将用于跳转至非法程序的指针自底向上遍历Flash地址尝试应用程序的入口地址。

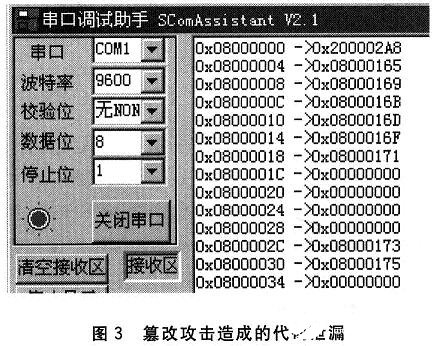

实验的结果通过PC端接收到非法读取程序输出的代码数据验证,读取的过程是芯片上电复位后自Flash起始地址启动执行口,Bootloader在运行模式下将跳转至应用程序入口地址执行。在非法跳转指针移动过程中,应用程序入口地址被跳转指针覆盖时,非法读取程序将得到执行机会。所进行的实验结果如图3所示。

通过实验,验证了当部分应用程序内容被修改时,Bootloader可以正常进入运行模式,在放置的跳转指针尝试至应用程序函数入口地址时,程序可以跳转至非法读取程序执行读取命令,得到Bootloader程序和被部分修改的应用程序代码。复制到新的芯片中后运行启动Bootloader升级模式,将升级程序下载升级程序包覆盖应用程序区域,就得到了完整的Bootloader程序和应用程序代码。

3 双重完整性检验安全方案设计与验证

实际应用中,Bootloader引导应用程序结构的软件在STM32F103RB芯片上使用时,厂商可以通过改进Boot-loader的设计,最大程度地避免这种篡改应用程序方式带来的代码被抄袭的风险。由于芯片读保护有效时,前3片区的自动写保护可以保证中断向量表不被篡改,从而Bootloader在Flash地址启动时首先执行。

在更新应用程序的过程中,除了升级程序包采用加密、方式由Bootloader在升级模式下将内容解密后写入应用程序区域外,Bootloader运行模式下确认Flash中的内容为完整的合法程序和阻止非法程序的运行是安全设计方案的出发点。下面介绍的是采用双重完整性检验的方案提高代码安全性的方法:

①由于STM32F103RB芯片的Falsh的写操作需要对片区擦除后进行,可以在各片区的特定地址内依次放置厂商设定的1~2字节伪随机码,组成密码序列。在非法读取程序或跳转指针写入时,对片区擦除过程将破坏伪随机码而不能重新写回,导致密码序列的破坏。

②CRC检验是较为常见的一种数据传输检错方式,随着技术的发展,已经出现了能够适用于嵌入式系统有限资源的快速算法。将应用程序代码区域的CRC检验值在升级程序时保存在Flash中的约定位置。对应用程序代码的非法修改将使CRC检验值改变。

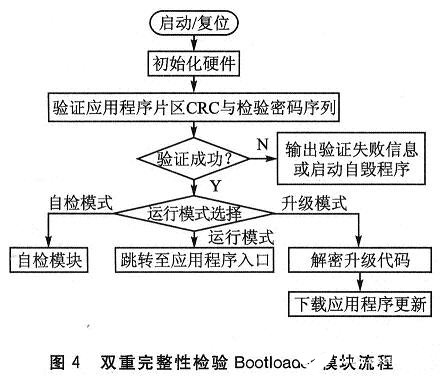

加入了双重完整性检验方案的Bootloader功能模块流程如图4所示。

方案的设计可以使芯片上电复位后,自Flash起始地址运行的Bootloader及时发现篡改攻击造成的改变,并防止非法代码得到执行机会。在安全设计方案验证实验中,设计Bootloader在运行模式下验证密码序列的完整性,并将应用程序区域的CRC检验值与保存在约定位置中初始检验值比较,从而验证Flash内容未被篡改。在验证失败时,输出验证失败信息和当前的CRC检验值后进入死循环,而不再启动应用程序。

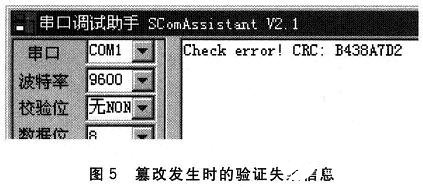

对方案的验证实验采用在应用程序片区的末尾写入伪随机码序列和32位CRC检验算法,依次对Flash的4~128 片区单独进行擦除后写入非法代码进行验证,均得到图5所示的验证失败信息。

实际测试中,对不同片区的篡改操作得到不同的CRC检验值与合法应用程序CRC检验值互不相同。双重完整性检验方案在STM32F103RB芯片上运行带来的时间开销约为80ms,也能够被产品启动过程所接受。在厂商进行产品开发时,可以进一步设计Bootloader验证失败时进入自毁程序,通过修改读保护状态使芯片被整片擦除,从而销毁所有代码,提高代码的安全性。

结语

嵌入式系统是硬件与软件高度结合的技术应用,通过对STM32F103RB芯片上进行Bootloader引导应用程序结构软件开发时的篡改攻击风险验证,可以看到嵌入式产品被抄袭风险的严峻性。在实际应用中,嵌入式系统设计应当结合软件结构的特点和硬件提供的保护特性,灵活使用不同的保护方式,有效地提高程序的安全性,达到最大程度地对厂商代码和知识产权的保护。

-

ARM

+关注

关注

134文章

8647浏览量

361733 -

内核

+关注

关注

3文章

1309浏览量

39839 -

微处理器

+关注

关注

11文章

2128浏览量

81391

发布评论请先 登录

相关推荐

采用ARM新一代Cortex-M3内核实现改进Bootloader的安全设计方案

采用ARM新一代Cortex-M3内核实现改进Bootloader的安全设计方案

评论