笔者在技术支持过程中,常常遇到工程师质疑放大器的增益带宽积参数“掺水”啦!!!设计中明明预留很大余量,但是电路的输出波形依然出现失真的情况。其实,在交流信号调理电路的带宽评估中,应该区分对待输入信号是小信号,还是大信号。如果输入信号是小信号使用增益带宽积参数是合理的,而当输入信号为大信号时,还使用增益带宽积参数进行评将会导致设计缺陷。本篇将通过一个实例分析,压摆率与大信号带宽(满功率带宽)的关系,以及一种快捷仿真满功率带宽的方式。

压摆率定义

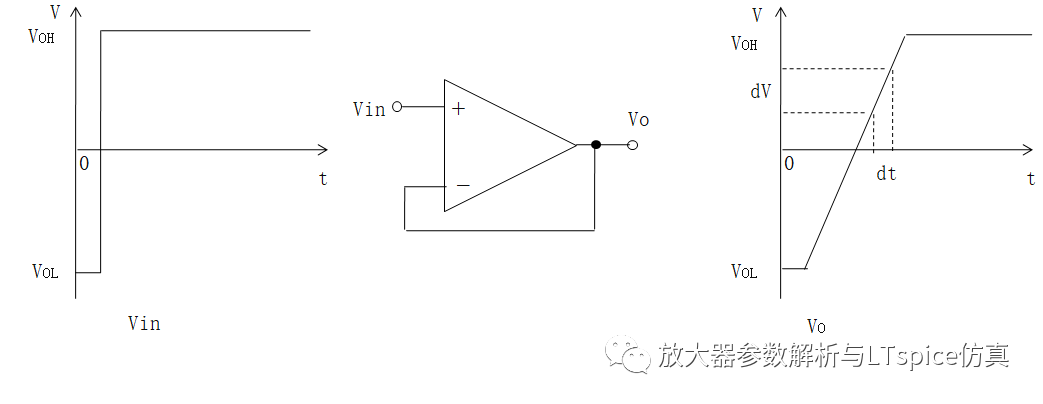

压摆率(Slew Rate,SR)定义为由输入大信号阶跃变化引起的输出电压变化率,常用单位是V/μs。如图2.125,在缓冲器电路的输入端提供一个由最低输入信号到最高输入信号的阶跃变化Vin,放大器受到压摆率参数的影响,输出信号Vo对于大信号的响应以最快的变化速率(dV/dt)上升,直到输出信号达到与输入信号等幅值。

图2.125 压摆率参数工作示意图

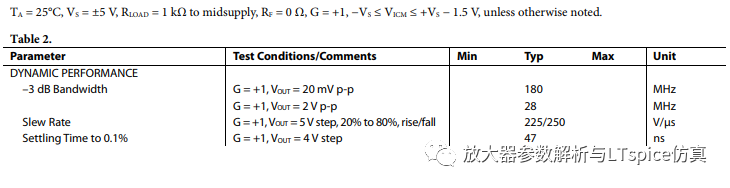

应当注意放大器上升、下降过程中的压摆率可能不同,以及压摆率参数的测试条件。如图2.126,在±5V电源供电,增益为1倍的电路中,ADA4807输出5V阶跃信号。在信号的上升沿,从峰值的20%提高到80%时,压摆率(SR+)为225V/μs。在信号的下降沿,从峰值的80%下降到20%时,压摆率(SR-)为250V/μs。

图2.126 ADA4807动态性能参数

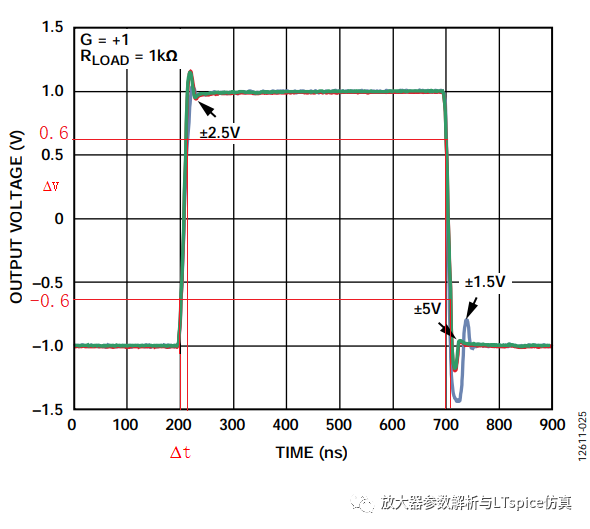

在数据手册中,没有明确提供压摆率参数的放大器,可以使用大信号瞬态响应图。如图2.127,估读Δt、ΔV,按照压摆率定义估算压摆率的范围。

图2.127 ADA4807大信号瞬态响应

压摆率与满功率带宽的关系

虽然在数据手册中可以获得压摆率参数,但是在工程师设计中最终需要的是大信号带宽,即满功率带宽(Full Power Bandwidth,FPBW)。它是指放大器在指定闭环增益与指定负载的条件下,输入正弦波时,输出为指定最大幅度,在此状态下增大输入信号的频率直到输出信号因为压摆率限制导致失真的频率点。

满功率带宽的计算过程如下:

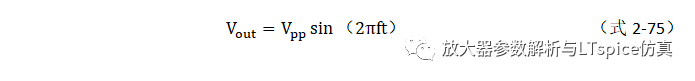

输入信号是峰峰值为Vpp,频率为f的正弦波,通过单位增益电路的输出电压为式2-75。

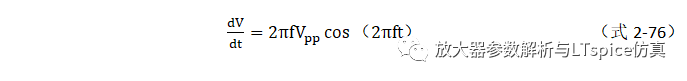

输出电压对时间求导,得到式2-76。

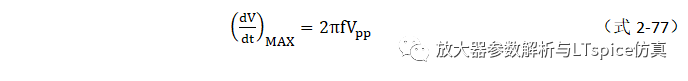

当dv/dt 达到最大时,函数式为2-77。

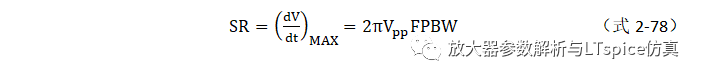

式中MAX表示在函数cos等于1的时候取得最大值。即在Sin信号 t =0 时的压摆率值。此时,对应的信号频率就是满功率带宽,式2-77变换为式2-78。

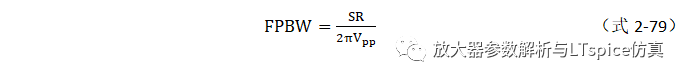

由式2-78,调整为满功率带宽的函数式,如式2-79。

可见,满功率带宽由压摆率和信号峰峰值决定。当压摆率为常数时,信号峰峰值越大,满功率带宽越小。如图2.126,ADA4807的上升压摆率为225V/μs,当输入信号峰峰值为2V时,其满功率带宽为17.9MHz。当信号峰峰值为4V时,其满功率带宽仅为8.95MHz。所以在大信号作输入激励的ADA4807应用电路中,仍然使用增益带宽积(-3dB带宽为180MHz)进行设计,必然会导致电路输出信号失真。

压摆率与满功率带宽实例分析

去年4月中旬,笔者接触到一位刚刚成立工作室的工程师,在首款产品研发中,将AD8065设计为电路第二级的缓冲器,调试中发现输出信号产生失真。

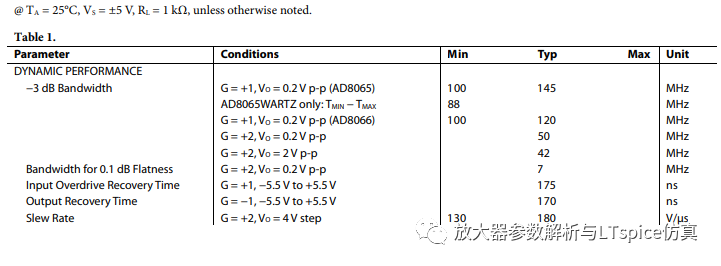

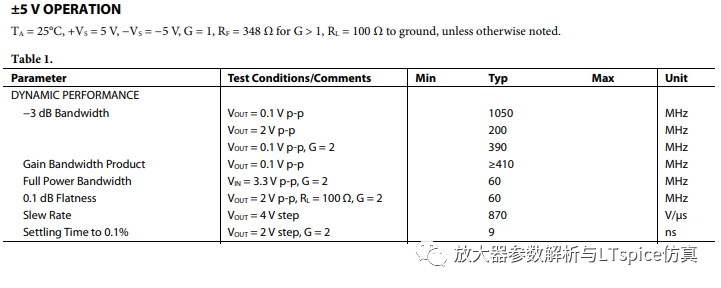

电路如图2.136,输入信号是幅值为±0.1~±1V ,频率为10~30MHz的正弦波,工程师反馈在输入信号为±1V,信号频率超过20MHz时,AD8065的输出信号会产生失真。如图1,工程师对比过AD8065的-3dB 信号带宽为145MHz没有发现异议。

图1 AD8065动态性能参数

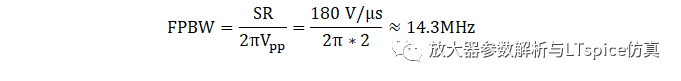

笔者向工程师解释问题在于±0.1~±1V的信号属于大信号范围,应该使用压摆率计算全功率带宽的方法进行评估。AD8065在±5V供电,输入信号峰峰值为2V,满功率带宽为:

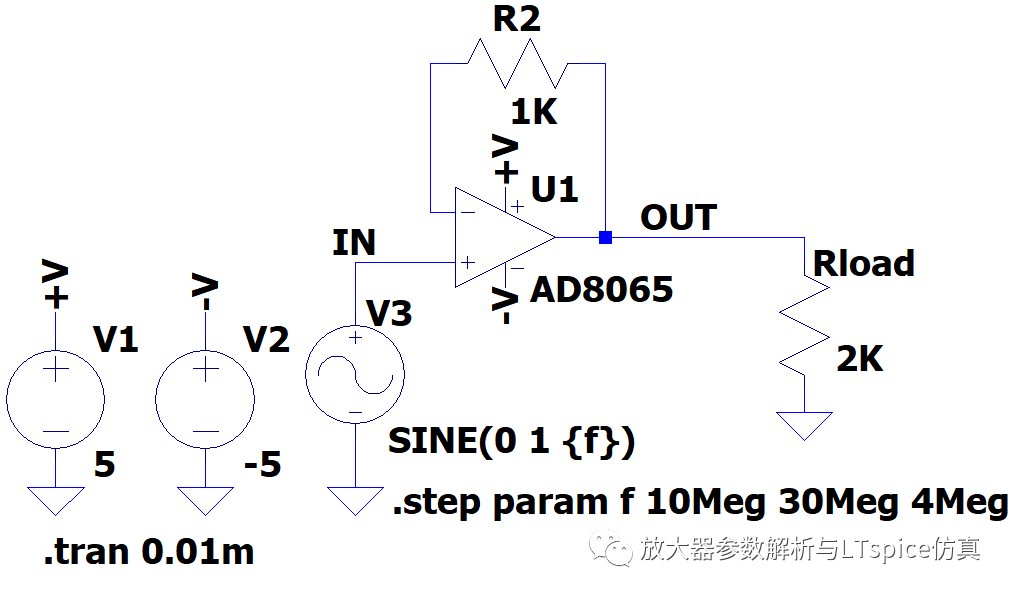

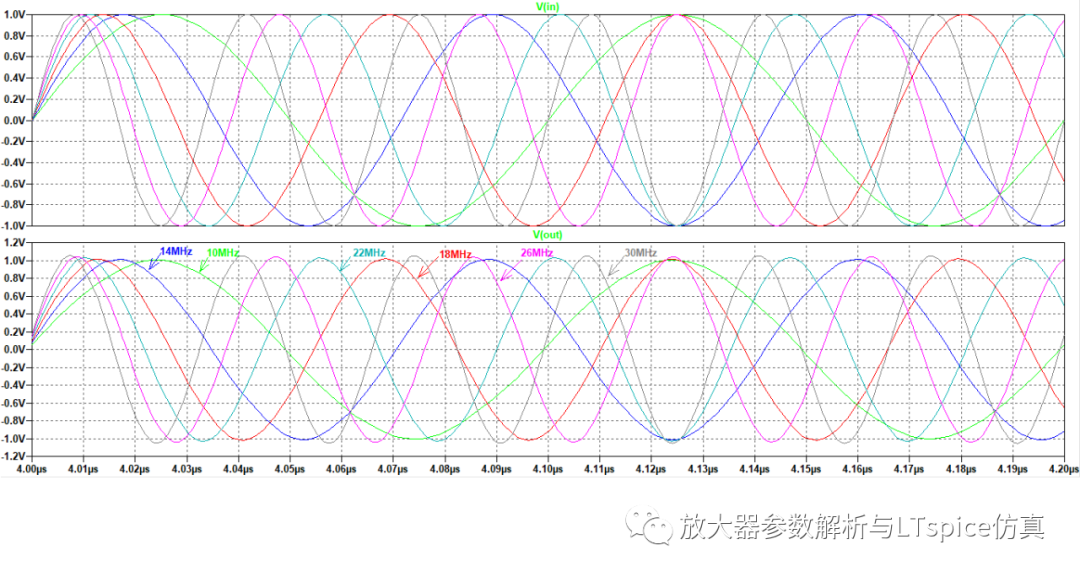

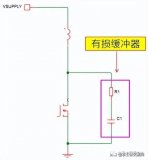

该问题如果工程师在方案选型阶段使用LTspice进行仿真完全可以暴露设计漏洞,规避压摆率限制问题,高效优质地完成硬件设计工作。如图2.136,将信号源V3设置为正弦波,峰峰值为2V,频率设置可变参量f,变化范围是10~30MHz,以4MHz为步长。

图2.136 AD8065缓冲电路

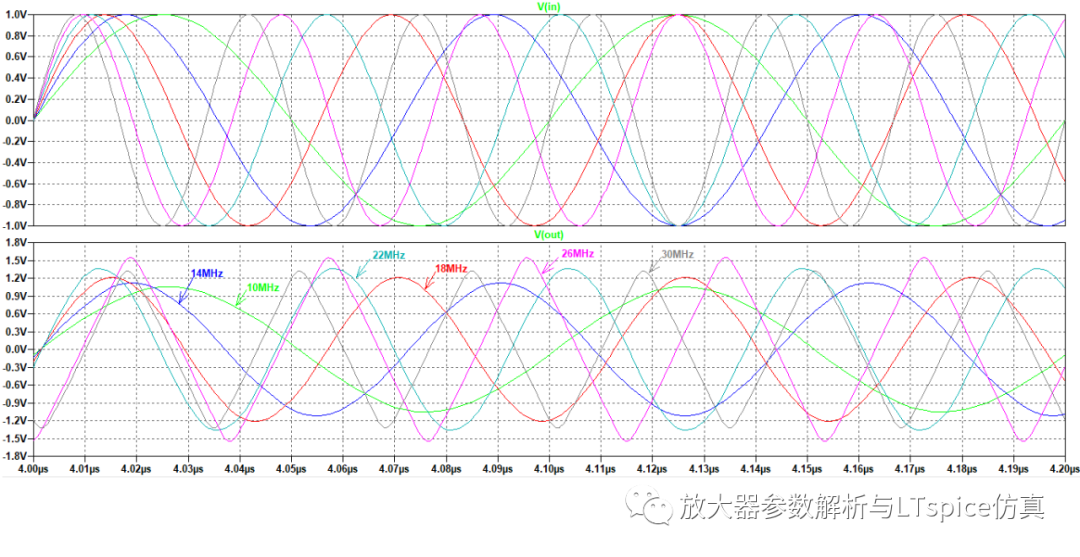

AD8065的输出信号对比输入信号的仿真结果,如图2.137。当输入信号频率为10MHz、14MHz时,输出完全跟随输入;当信号频率为18MHz时,其输出稍有失真;当信号频率为22MHz时,其输出明显失真;当信号频率为26MHz、30MHz时,其输出受压摆率限制完全失真成为三角波,斜率为压摆率。

图2.137 AD8065缓冲电路的满功率带宽仿真结果

将电路中AD8065替换为笔者推荐的ADA4817,再次进行仿真。如图2,数据手册中,提供了ADA4817在±5V供电,4V阶跃的条件下,压摆率典型值为870V/μs,以及输入信号为3.3V,电路增益为2倍时满功率带宽典型值为60MHz。

图2 ADA4817动态性能参数

结果如图2.138,输入正弦信号峰值为±1V,在频率为10~30MHz范围内,输出信号V(out)完全跟随与输入信号V(in)变化而变化,没有再发生失真现象。

图2.138 ADA4817缓冲电路的满功率带宽仿真结果

通过这个实例可以让大家更直观感受到,在大信号带宽的设计中,需要使用的参数是压摆率。以及在电路选型评估中,使用LTspice的参数扫描指令,实现电路大信号带宽的高效验证。这也是为什么最近一年多的时间里,在笔者所支持的工程师群体中,LTspice已经成为不可或缺的仿真评估软件的原因。

责任编辑:pj

-

电路

+关注

关注

170文章

5478浏览量

169398 -

带宽

+关注

关注

3文章

818浏览量

40060 -

频率

+关注

关注

4文章

1272浏览量

58458

发布评论请先 登录

相关推荐

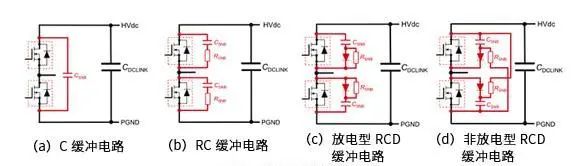

SiC MOSFET非放电型RCD缓冲电路的设计

关于AD8065缓冲电路的满功率带宽仿真结果

关于AD8065缓冲电路的满功率带宽仿真结果

评论