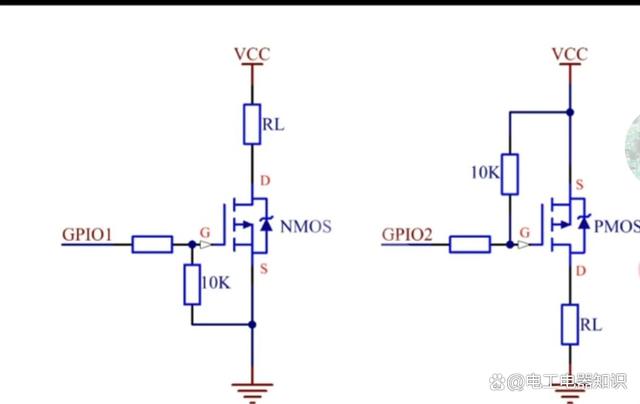

如下是一个 NMOS 的开关电路,阶跃信号 VG1 设置 DC 电平 2V,方波(振幅 2V,频率 50Hz),T2 的开启电压 2V,所以 MOS 管 T2 会以周期 T=20ms 进行开启和截止状态的切换。

首先仿真 Vgs 和 Vds 的波形,会看到 Vgs=2V 的时候有一个小平台,有人会好奇为什么 Vgs 在上升时会有一个小平台?

MOS 管 Vgs 小平台

带着这个疑问,我们尝试将电阻 R1 由 5K 改为 1K,再次仿真,发现这个平台变得很小,几乎没有了,这又是为什么呢?

MOS 管 Vgs 小平台有改善

为了理解这种现象,需要理论知识的支撑。

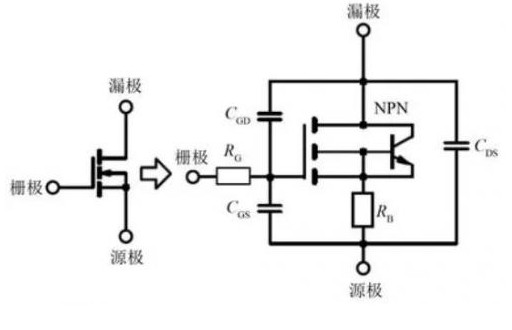

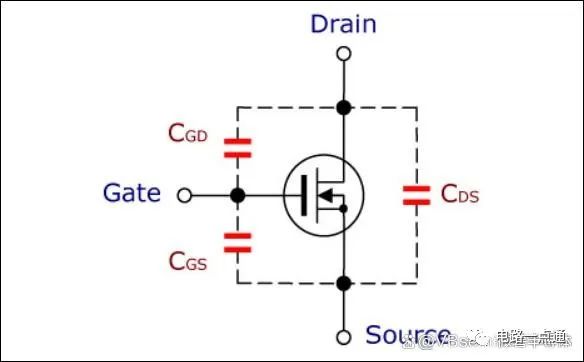

MOS 管的等效模型

我们通常看到的 MOS 管图形是左边这种,右边的称为 MOS 管的等效模型。

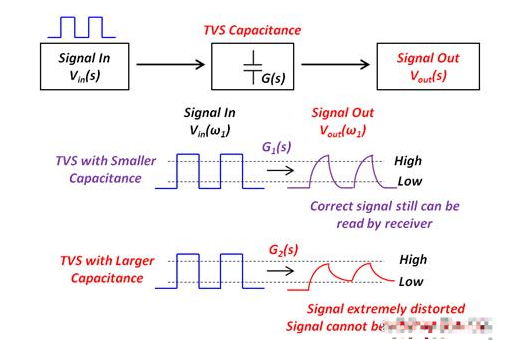

其中:Cgs 称为 GS 寄生电容,Cgd 称为 GD 寄生电容,输入电容 Ciss=Cgs+Cgd,输出电容 Coss=Cgd+Cds,反向传输电容 Crss=Cgd,也叫米勒电容。

如果你不了解 MOS 管输入输出电容概念,请点击:带你读懂 MOS 管参数「热阻、输入输出电容及开关时间」

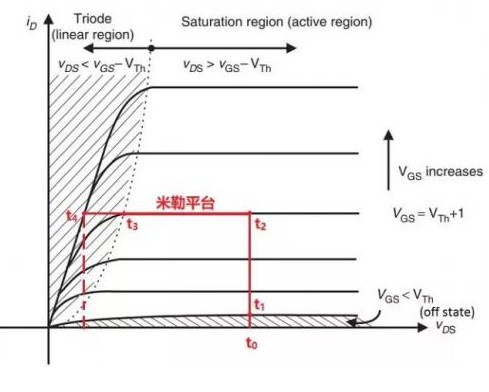

米勒效应的罪魁祸首就是米勒电容,米勒效应指其输入输出之间的分布电容 Cgd 在反相放大的作用下,使得等效输入电容值放大的效应,米勒效应会形成米勒平台。

首先我们需要知道的一个点是:因为 MOS 管制造工艺,必定产生 Cgd,也就是米勒电容必定存在,所以米勒效应不可避免。

那米勒效应的缺点是什么呢?

MOS 管的开启是一个从无到有的过程,MOS 管 D 极和 S 极重叠时间越长,MOS 管的导通损耗越大。因为有了米勒电容,有了米勒平台,MOS 管的开启时间变长,MOS 管的导通损耗必定会增大。

仿真时我们将 G 极电阻 R1 变小之后,发现米勒平台有改善?原因我们应该都知道了。

MOS 管的开启可以看做是输入电压通过栅极电阻 R1 对寄生电容 Cgs 的充电过程,R1 越小,Cgs 充电越快,MOS 管开启就越快,这是减小栅极电阻,米勒平台有改善的原因。

那在米勒平台究竟发生了一些什么?

以 NMOS 管来说,在 MOS 管开启之前,D 极电压是大于 G 极电压的,随着输入电压的增大,Vgs 在增大,Cgd 存储的电荷同时需要和输入电压进行中和,因为 MOS 管完全导通时,G 极电压是大于 D 极电压的。

所以在米勒平台,是 Cgd 充电的过程,这时候 Vgs 变化则很小,当 Cgd 和 Cgs 处在同等水平时,Vgs 才开始继续上升。

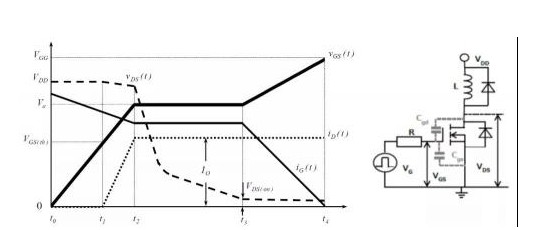

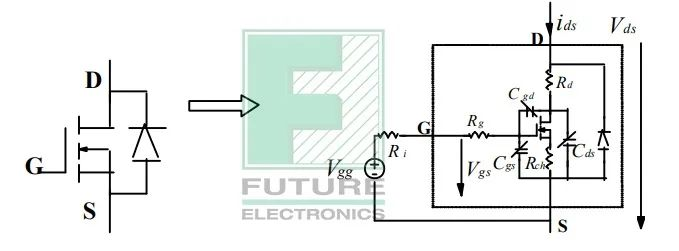

我们以下右图来分析米勒效应,这个电路图是一个什么情况?

MOS 管 D 极负载是电感加续流二极管,工作模式和 DC-DC BUCK 一样,MOS 管导通时,VDD 对电感 L 进行充电,因为 MOS 管导通时间极短,可以近似电感为一个恒流源,在 MOS 管关闭时,续流二极管给电感 L 提供一个泄放路径,形成续流。

MOS 管的开启可以分为 4 个阶段。

t0~t1 阶段

从 t0 开始,G 极给电容 Cgs 充电,Vgs 从 0V 上升到 Vgs(th)时,MOS 管都处于截止状态,Vds 保持不变,Id 为零。

t1~t2 阶段

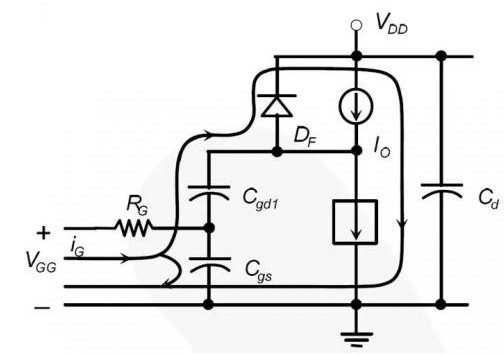

从 t1 后,Vgs 大于 MOS 管开启电压 Vgs(th),MOS 管开始导通,Id 电流上升,此时的等效电路图如下所示,在 IDS 电流没有达到电感电流时,一部分电流会流过二极管,二极管 DF 仍是导通状态,二极管的两端处于一个钳位状态,这个时候 Vds 电压几乎不变,只有一个很小的下降(杂散电感的影响)。

t1~t2 阶段等效电路

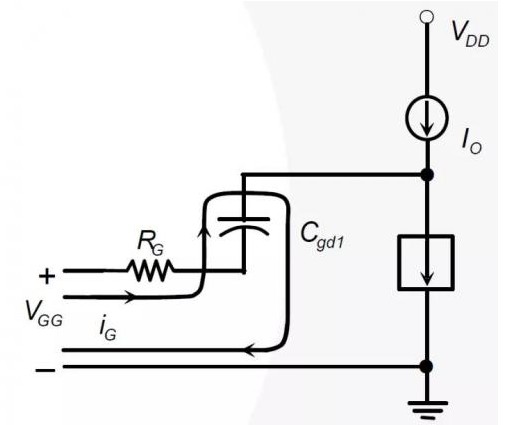

t2~t3 阶段

随着 Vgs 电压的上升,IDS 电流和电感电流一样时,MOS 管 D 极电压不再被二极管 DF 钳位,DF 处于反向截止状态,所以 Vds 开始下降,这时候 G 极的驱动电流转移给 Cgd 充电,Vgs 出现了米勒平台,Vgs 电压维持不变,Vds 逐渐下降至导通压降 VF。

t2~t3 阶段等效电路

t3~t4 阶段

当米勒电容 Cgd 充满电时,Vgs 电压继续上升,直至 MOS 管完全导通。

结合 MOS 管输出曲线,总结一下 MOS 管的导通过程

t0~t1,MOS 管处于截止区;t1 后,Vgs 超过 MOS 管开启电压,随着 Vgs 的增大,ID 增大,当 ID 上升到和电感电流一样时,续流二极管反向截止,t2~t3 时间段,Vgs 进入米勒平台期,这个时候 D 极电压不再被续流二极管钳位,MOS 的夹断区变小,t3 后进入线性电阻区,Vgs 则继续上升,Vds 逐渐减小,直至 MOS 管完全导通。

MOS 管输出曲线

责任编辑:pj

-

二极管

+关注

关注

144文章

8988浏览量

161242 -

电阻

+关注

关注

85文章

5026浏览量

169552 -

MOS管

+关注

关注

106文章

2203浏览量

64325

发布评论请先 登录

相关推荐

PCB寄生电容的影响 PCB寄生电容计算 PCB寄生电容怎么消除

LTC6268-10为了使寄生电容降到最低,对电路板的材料类型和厚度有什么要求吗?

什么是寄生电容?寄生电容对压敏电阻产生的影响

开关电源中MOS管栅极上拉电阻和下拉电阻的作用

寄生电容对MOS管快速关断的影响

如何减轻米勒电容所引起的寄生导通效应?

pcb连线寄生电容一般多少

PCB寄生电容的影响、计算公式和消除措施

AMAZINGIC晶焱科技考虑寄生电容的高速接口中的TVS选择以及方案应用

射频频率上电感、电阻、电容都有变化?

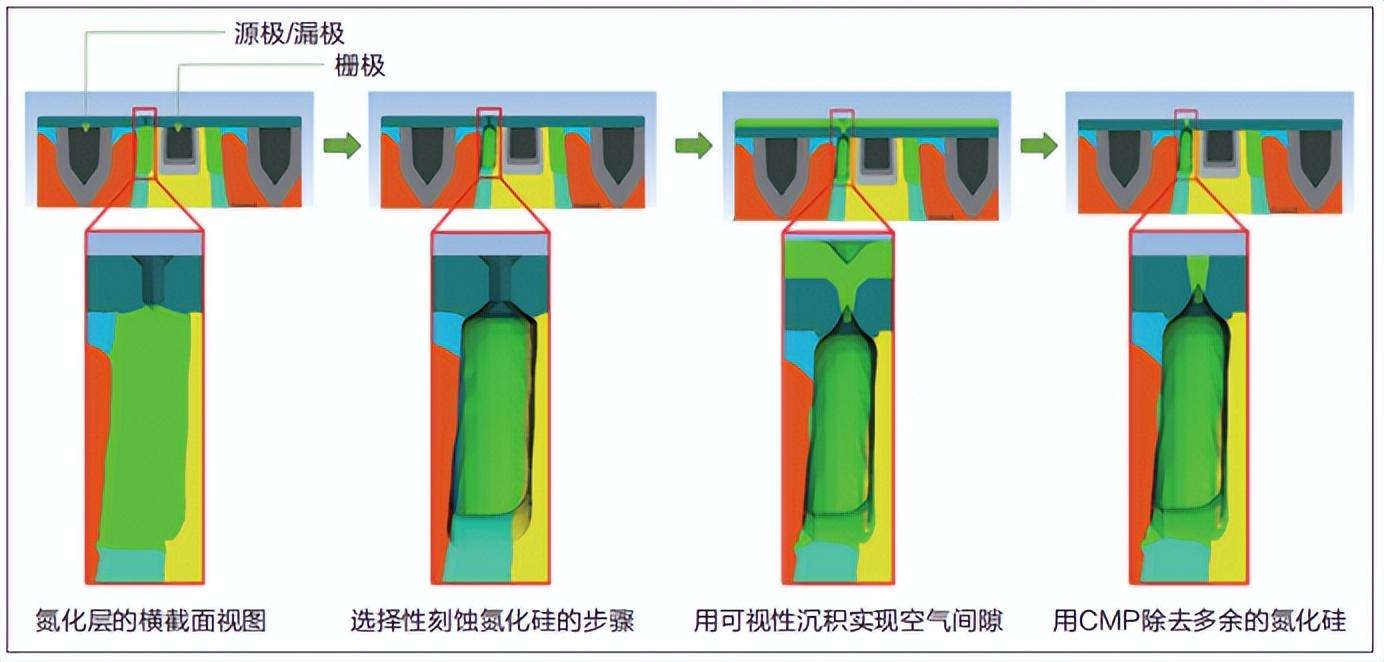

引入空气间隙以减少前道工序中的寄生电容

GS 寄生电容的缺点是什么?

GS 寄生电容的缺点是什么?

评论