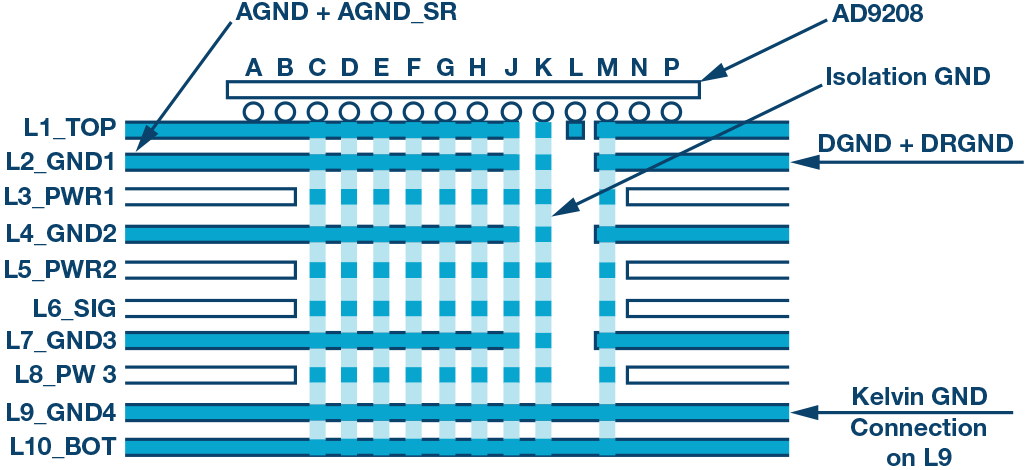

在采样速率和可用带宽方面,当今的射频模数转换器(RF ADC)已有长足的发展。其中还纳入了大量数字处理功能,电源方面的复杂性也有提高。那么,当今的RF ADC为什么有如此多不同的电源轨和电源域?

|

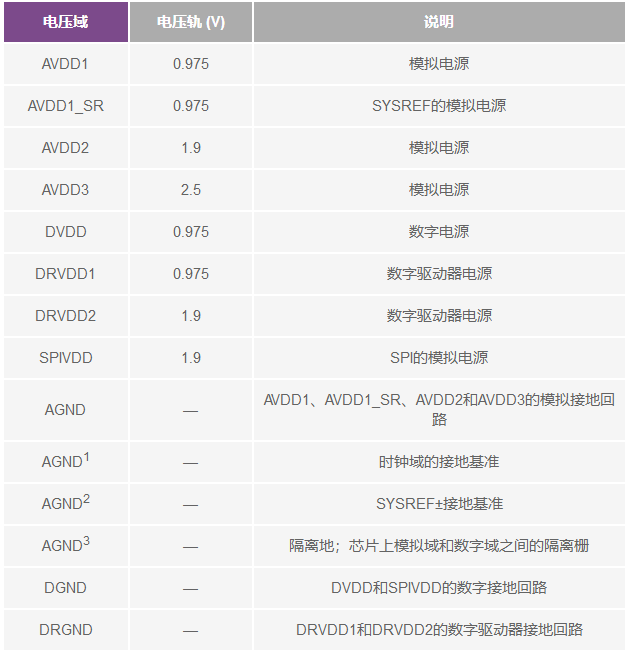

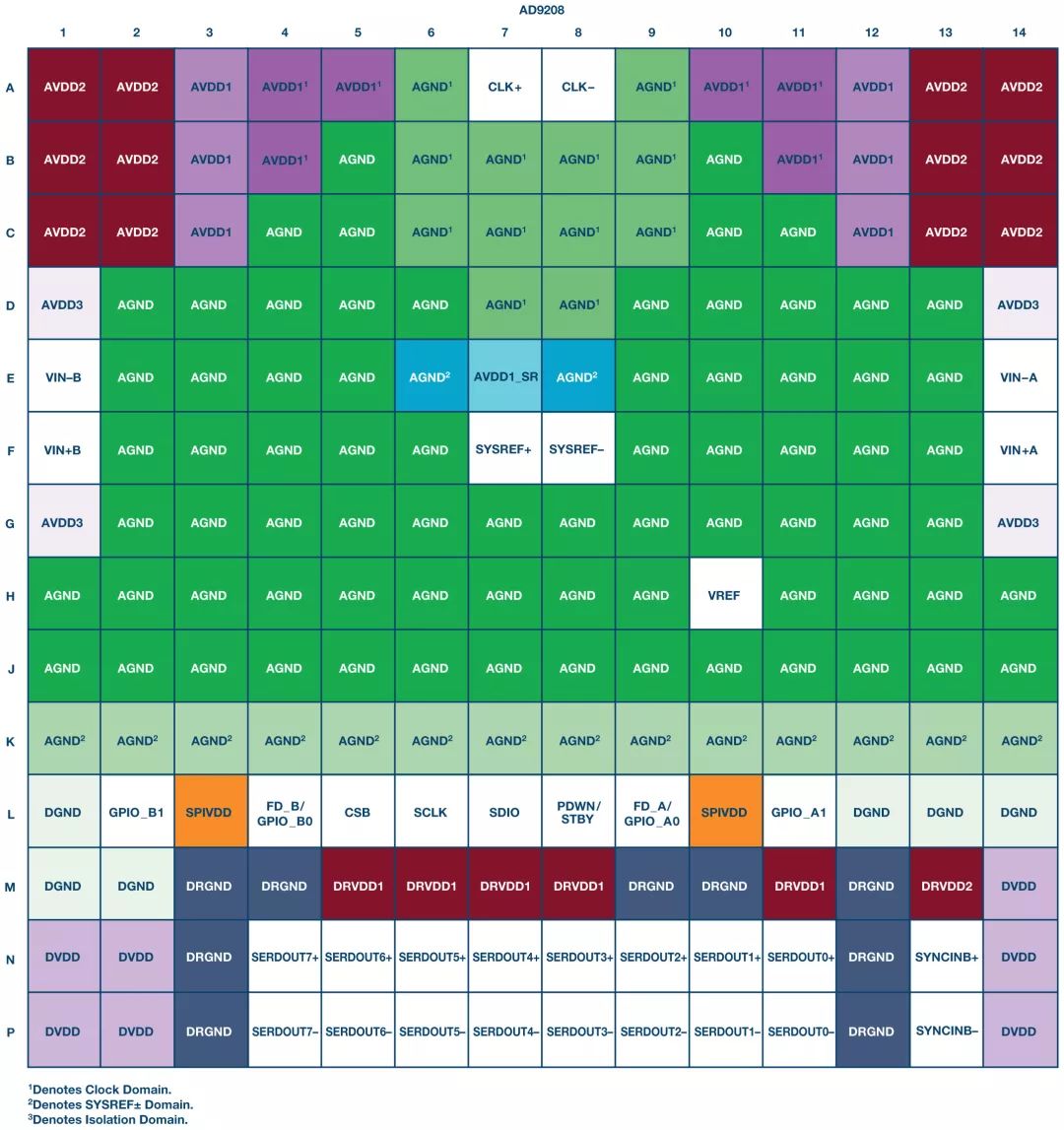

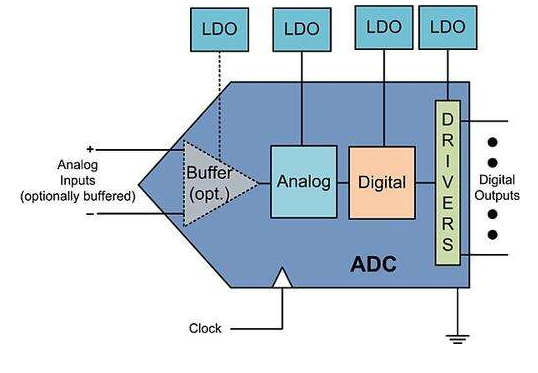

绝对不是。仅仅因为AD9208数据手册显示了所有这些域,并不意味着它们在系统板上必须全部分离。了解系统性能目标和ADC目标性能对优化ADC的PDN起着重要作用。在电路板上使用智能分区以减少不必要的接地回路,是将各个域之间的串扰降到最低的关键。适当地共享电源域,同时满足隔离要求,将能简化PDN和BOM。

-

支持每线高达 16 Gbps 的线速

-

SFDR = 70 dBFS -

SNR = 57.2 dBFS

-

SFDR = 78 dBFS -

SNR = 59.5 dBFS

-

48 位 NCO -

4 个级联半带滤波器

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

adc

+关注

关注

95文章

5644浏览量

539381

原文标题:高速 ADC 咋有这么多不同的电源轨和电源域呢?

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

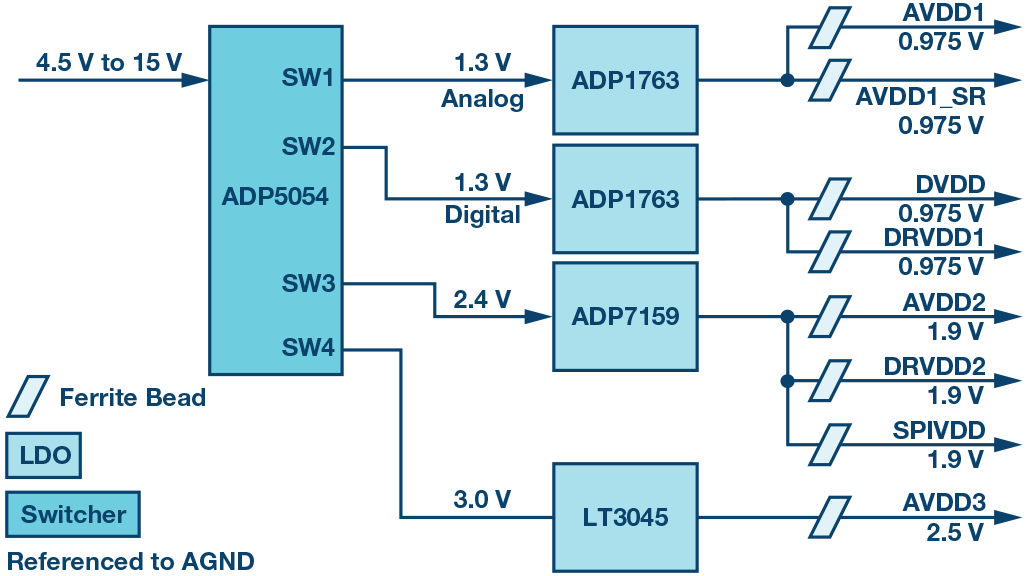

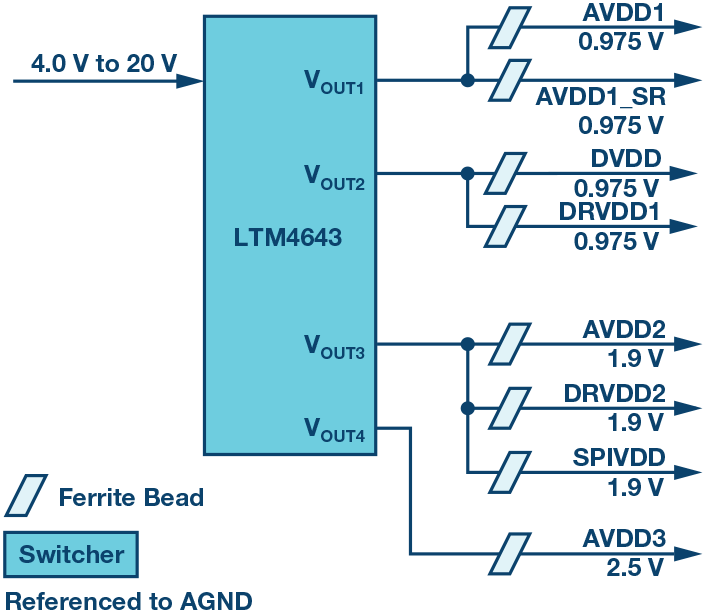

高速ADC的电源拓扑结构设计方案

当供电轨上有噪声时,决定ADC性能的因素主要有三个,它们是PSRR-dc、PSRR-ac和PSMR。PSRR-dc指电源电压的变化与由此产生的ADC增益或失调误差的变化之比值,它可以用最低有效

发表于 03-22 10:29

•107次阅读

电源电压的波动对ADC的转换性能有多大的影响?

电源出6V 5V两个电源轨,首先采用DC-DC开关芯片将8V降压到6.3V左右

然后用LDO稳压到6V,后经过LDO稳压输出5V。

现在的问题是:

1、在选择LDO时除了输出电压与电流,我应该更关注哪些参数?

2、

发表于 01-08 07:45

在AD9787里面,哪些管脚是属于DVDD33的电源域,哪些是属于DVDD18的电源域?

在AD9787里面,数字电压有两个一个是DVDD33,一个是DVDD18,想问的是,哪些管脚是属于DVDD33的电源域,哪些是属于DVDD18的电源域?

发表于 12-01 06:33

AD8226输出不能轨对轨是什么原因?

近期做了一款AD8226仪表放大(轨对轨的),如图5V单电源供电。我差分1mv输入,频率1khz,放大1000倍,波形是正常的。当我逐渐增大输入电压后,芯片最大输出只能到2.8V这样就失真了,不论

发表于 11-20 07:38

AD8666轨到轨运放饱和电压误差大的原因?

我用的是AD8666轨到轨芯片,电源供电10.6V,该电源是由MC33063出来的电压供电的。当调整Vin的输入时,Vout最大只能到9.2V,与电

发表于 11-20 06:26

与ADC接口:电源,第4部分

到目前为止,我们已经研究了ADC的不同类型的电源输入,然后介绍了几种驱动它们的方法。我们主要专注于使用LDO,但我们已经看到这可能并不总是最好的方法。根据系统约束和性能规格,其他拓扑可能更好。在这方面,我们来看看使用DC/DC转换器(有时称为开关稳压器)和LDO来驱动

ADC接口:电源,第5部分

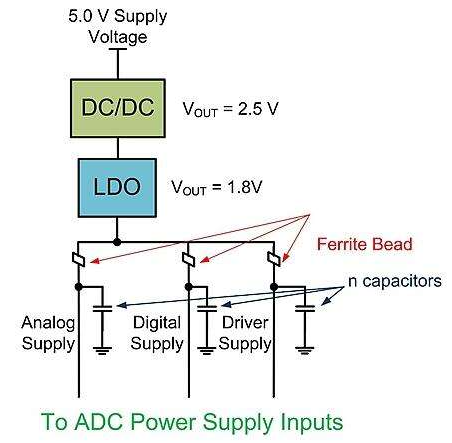

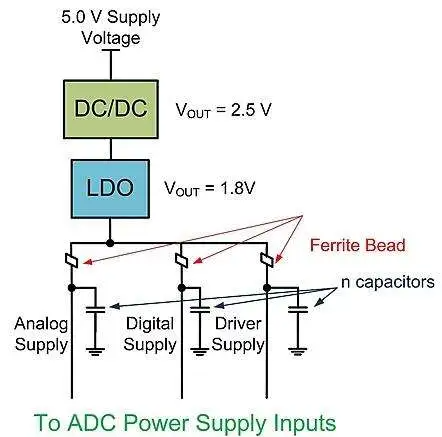

我们发现,使用DC/DC转换器降低LDO的输入电压是驱动ADC电源输入的一种更有效的方法。提醒一下,下面的图 1 给出了此拓扑。输入电源电压为5.0 V,降压至2.5 V,然后输入至LDO,A

与ADC接口:电源,第6部分

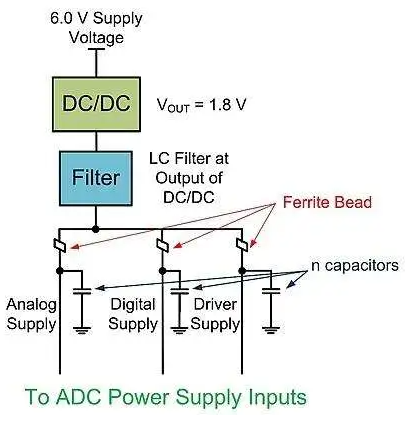

我们在本博客系列中看到,这种方法比仅使用 LDO 更有效。在本博客中,我们将更进一步,介绍如何直接从DC/DC转换器驱动ADC电源(如图1所示)。输入电源电压为6.0 V,对于ADC

高速ADC的单事件效应(SEE):单事件闩锁(SEL)

今天我们将专门研究高速 ADC 以及可以观察到的单事件效应。我计划在接下来的几篇博客中深入探讨这些单一事件效应。在本期文章中,我们将着眼于高速 ADC 的单事件闩锁 (SEL)。SEL

高速 ADC 咋有这么多不同的电源轨和电源域呢?

高速 ADC 咋有这么多不同的电源轨和电源域呢?

评论