据悉,台积电3纳米将继续采取目前的FinFET晶体管技术。

这意味着台积电确认了3纳米工艺并非FinFET技术的瓶颈,甚至还非常有自信能够在相同的FinFET技术下,在3纳米制程里取得水准以上的良率。这也代表着台积电的微缩技术远超过其他的芯片制造商。

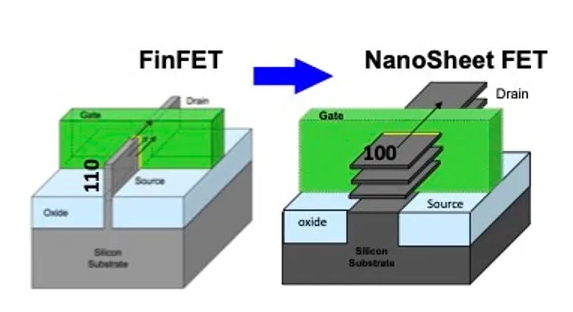

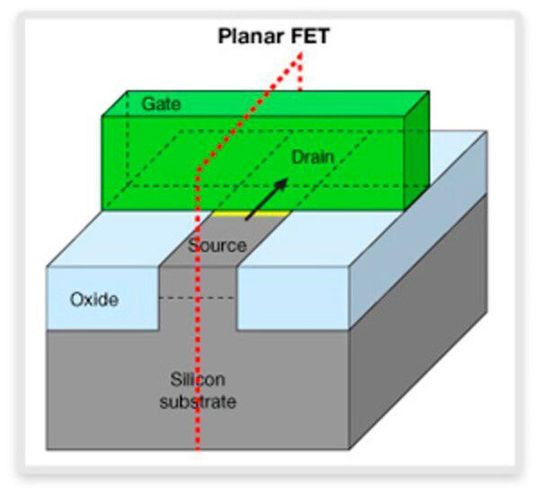

当制程下探,电路无可避免的会遭遇到控制的困难,产生如漏电、电压不稳定等的短通道效应(Short-channel Effects)。而为了有效抑制短通道效应,尽可能的增加电路的面积,提高电子流动的稳定性,就是半导体制造业者重要的考量,而鳍式晶体管(FinFET)架构就因此而生。

FinFET运用立体的结构,增加了电路闸极的接触面积,进而让电路更加稳定,同时也达成了半导体制程持续微缩的目标。但这个立体结构的微缩也非无极限,一但走到了更低的制程之后,必定要转采其他的技术,否则摩尔定律就会就此打住。

也因此,三星电子(Samsung)在2019年就宣布,将在3纳米制程世代,改采闸极全环(Gate-All-Around,GAA)的技术,作为他们FinFET之后的接班制程;无独有偶,目前的半导体龙头英特尔(Intel),也在不久前宣布,将投入GAA技术的开发,并预计在2023年推出采用GAA制程技术的5纳米芯片。

由于世界前两大的半导体厂都相继宣布投入GAA的怀抱,因此更让人笃定,也许3纳米将会是GAA的时代了,因为至3纳米制程,FinFET晶体管就可能面临瓶颈,必须被迫进入下个世代。

唯独台积电,仍将在3纳米世代延续FinFET晶体管的技术。进入3纳米世代,也因此他们不用变动太多的生产工具,也能有较具优势的成本结构。而对客户来说,也将不用有太多的设计变更,也有助于客户降低生产的成本。若最终的产品性能还能与竞争对手平起平坐,那台积电可能又将在3纳米产品世代再胜一筹。

尤其是对客户来说,在先进制程的开发里变更设计,无论是改变设计工具或者是验证和测试的流程,都会是庞大的成本,时间和金钱都是。因此若能维持当前的设计体系,对台积电和客户来说,都会是个双赢局面。

-

台积电

+关注

关注

43文章

5257浏览量

164767 -

FinFET

+关注

关注

10文章

247浏览量

89681 -

LED微缩技术

+关注

关注

0文章

2浏览量

4988

发布评论请先 登录

相关推荐

晶体管掺杂和导电离子问题原因分析

晶体管Ⅴbe扩散现象是什么?

在特殊类型晶体管的时候如何分析?

晶体管基极和集电极之间并联电容有什么作用?

晶体管和场效应管的本质问题理解

不同类型的晶体管及其功能

台积电将继续采用FinFET晶体管技术,有信心保持良好水平

台积电将继续采用FinFET晶体管技术,有信心保持良好水平

评论