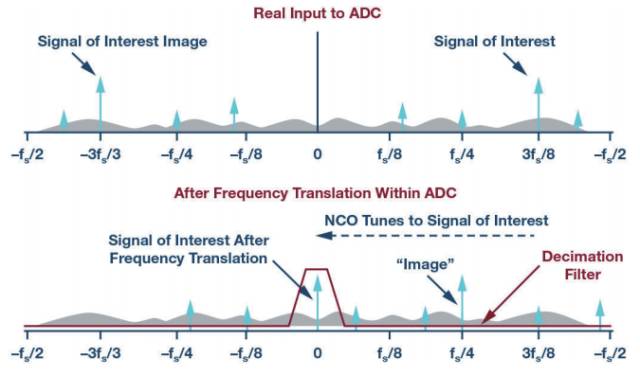

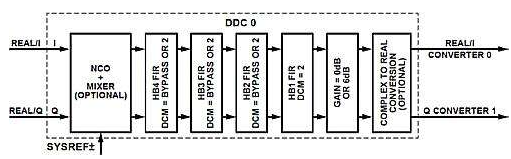

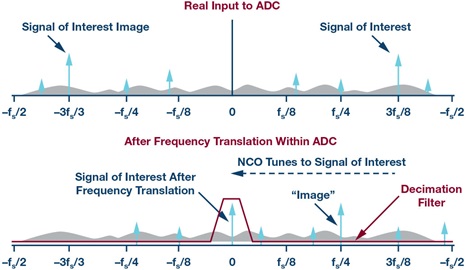

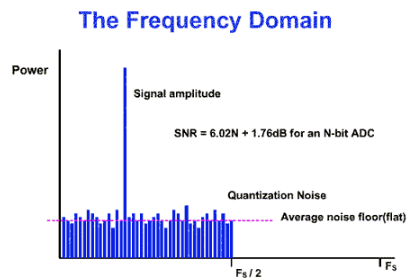

宽带GSPS模数转换器(ADC)使高速采集系统具备很多性能优势。这类ADC提供宽频谱的可见性。然而,虽然有些应用需要宽带前端,但也有一些应用要求能够滤波并调谐到更窄的频谱。 当需要窄带时,ADC采样、处理并消耗功率传输宽带频谱的效率很低。没有必要在后期处理中使用大量FPGA收发器来抽取和过滤宽带数据。高性能GSPS ADC让数字下变频(DDC)进驻到ADC内部。减少JESD204B ADC输出通道数可以最大限度地降低数据速率和系统布局的复杂度。 抽取是一种仅观察ADC采样样本的周期性部分,而忽略其余部分的方法。抽取的结果是降低ADC的采样速率。例如,1/4抽取模式意味着(总样本数)/4,有效地抛弃所有其他样本。 ADC还必须包含数控振荡器(NCO)和一个滤波和混频元件(用作抽取功能的配对器件)。数字滤波有效地消除了由抽取率设定的狭义带宽的带外噪声。作为本振的NCO的数字调谐字提供采样速率的小数分频,通过分辨率位数提供精确定位。调谐字具有范围和分辨率,可以将滤波器按频谱放置在需要的地方。 滤波器的通带应与抽取后的转换器的有效频谱宽度相匹配。使用DDC的显著优势是能够定位基本信号的谐波,使其落在目标频段以外。 DDC滤波器的数字滤波可滤除较窄带宽之外的噪声。理想ADC的SNR计算必须考虑过滤噪声的处理增益。使用一个完美的数字滤波器,带宽每减少2次幂,因过滤噪声而产生的处理增益就会增加3dB。 理想的SNR(包括处理增益)=6.02 × N + 1.76 dB + 10log10(fs/(2 × BW))

图1. 使用低通滤波器和NCO执行频率转换,实现一个带通滤波器。频率规划确保无用谐波和杂散落在带宽之外。 AD9694

通道速率最高达15 Gbps

各模数转换器(ADC)通道:415 mW

1.44p-p至2.16 V p-p(标称值1.80 V p-p)

48位NCO,最多4个级联半带滤波器

JESD204B(子类1)编码串行数字输出

总功耗:1.66 W (500 MSPS)

SFDR:82 dBFS(305 MHz,1.80 V p-p输入范围)

SNR:66.8 dBFS(305 MHz,1.80 V p-p输入范围)

噪声密度:−151.5 dBFS/Hz(1.80 V p-p输入范围)

直流电源:0.975 V、1.8 V和2.5 V

无失码

ADC内部基准电压源

模拟输入缓冲

片内扰动,可改善小信号线性度

灵活的差分输入范围

模拟输入全功率带宽:1.4 GHz

幅度检测位支持实现高效AGC

集成4个宽带数字处理器

差分时钟输入

整数时钟分频值:1、2、4或8

片内温度二极管

灵活的JESD204B通道配置

-

adc

+关注

关注

95文章

5643浏览量

539299 -

模数转换器

+关注

关注

25文章

2296浏览量

125912

原文标题:【世说设计】模拟提示—— ADC 的抽取

文章出处:【微信号:Excelpoint_CN,微信公众号:Excelpoint_CN】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

揭秘∑-Δ ADC的工作原理

ADI 2017年12月最新中文资料

模拟提示之ADC的抽取

浅析ADC的抽取

怎么样使用FPGA设计ADC数字抽取滤波器

模拟提示:ADC抽取

模数转换器抽取技巧

模拟提示— ADC的抽取

ADC实现抽取的技巧详细概述

如何实现ADC的抽取

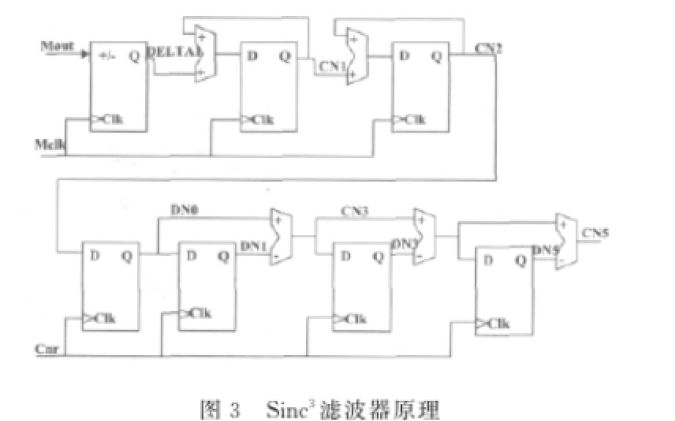

基于FPGA的_ADC数字抽取滤波器Sinc_3设计

ADC数字下变频器:抽取滤波器和ADC混叠,第1部分

模拟提示—— ADC的抽取

模拟提示—— ADC的抽取

评论