SoC 设计与应用技术领导厂商Socionext Inc.(以下“公司”)近日宣布成功开发了基于FPGA和ASIC电路的时间敏感网络(Time Sensitive Network, TSN)IP。该IP符合下一代以太网TSN(通信标准IEEE 802.1 Subset)及其评估环境,旨在为工业应用提供具有确定性的以太网。

TSN IP 评估板

Socionext在高速网络SoC及IP的设计开发方面拥有30多年的经验,期望通过提供最新的工业以太网解决方案助力推进工业物联网。公司最新开发的高性能TSN IP展现出了卓越的性能,其主要包括支持适用于工业设备之间通信的双口菊花链拓扑、1 Gbps高速操作、400 ns以下低延迟,及0.1微秒(μs)以下低抖动。

除了支持TSN外,该IP技术还可支持需要快速响应控制的运动控制器,以及应用于网络通信中确保带宽和低延迟的远程I / O等,满足各类工业设备要求。TSN支持在信息技术(IT)和操作技术(OT)之间进行无缝连接互操作,提升工厂整体效率和产能,推进实现智慧工厂。

在产品交付方面,Socionext将提供用于IP测试的FPGA评估板、启动手册和Linux开源驱动程序,帮助用户快速评估和开发。Socionext在工业ASIC开发领域拥有丰厚的设计开发经验,公司期望通过提供IP组合,助力客户开发设计属于他们自己的ASIC芯片。

产品特色:

Ethernet: 2ch

Link Speed: 1Gbps

Port Transfer Delay: ~ 400ns (cut through latency)

Low Jitter: +/- 0.1us

Queuing Priority: 8 Level

AMBA: Internal Data & Control

Linux Open Source Driver

交付产品:

IP Core Libraries

Linux Kernel Driver

Comprehensive Documentation

Evaluation Board and Reference Design based on XILINX Kintex-7 XC7K325T FPGA

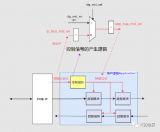

TSN IP Block Diagram

关于索喜科技有限公司

富士通电子旗下代理品牌 Socionext Inc. (索喜科技),是一家创新型企业,为全球客户设计、开发和提供片上系统(System-on-chip)产品。Socionext 整合了富士通(Fujitsu Limited)与松下(Panasonic Corporation)的片上系统半导体事业,专注于图像、网络、电脑运算与其他尖端技术之发展及应用。Socionext 集世界一流的专业知识、经验和丰富的IP 产品组合于一身,致力于提供高效益的解决方案与更佳的客户体验。

-

FPGA

+关注

关注

1602文章

21309浏览量

593122 -

以太网

+关注

关注

40文章

5075浏览量

166212 -

soc

+关注

关注

38文章

3743浏览量

215655

原文标题:助力智慧工厂加速上线,索喜科技最新时间敏感网络IP了解一下

文章出处:【微信号:Fujitsu_Semi,微信公众号:加贺富仪艾电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

读《FPGA入门教程》

fpga和asic的区别

FPGA实现基于Vivado的BRAM IP核的使用

为你的AI芯片从FPGA走向ASIC?

基于IP核的FPGA设计方法是什么?

基于FPGA和ASIC电路的时间敏感网IP

基于FPGA和ASIC电路的时间敏感网IP

评论