根据分频器设计时都是按恒阻抗法计算的原理,采用了先用标准电阻代替扬声器对分频网络进行调试,使之符合其标准衰减斜率,然后去掉电阻,接上扬声器并加上阻抗校正网络再重新进行调试的方法获得成功,实际试听感觉不错。

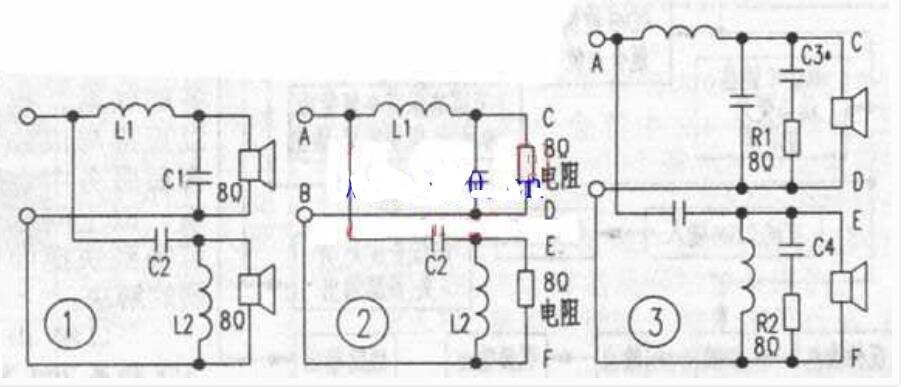

例如,我们要自制一个如图1所示的分频器,先用图表法绕好线圈L1和L2,可多绕几圈以便调节。按图2连接,从AB端输入分频点频率的功放信号电压,调节L1、C1、L2、C2,用万用表测量C、D端和E、F端电压使之符合分频点的衰减特性。然后按图3所示加入阻抗校正网络和接入扬声器进行调试,调节R1、C3及R2、C4使之符合分频点的衰减特性即可。对三分频而言也采用此方法调试,只是高频段可不加校正网络。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

分频器

+关注

关注

43文章

432浏览量

49310

发布评论请先 登录

相关推荐

分频器的作用 分频器的功率是不是越大越好

分频器是一种电子设备,用于将输入信号分成不同频率的输出信号。其主要作用是将原始输入信号分离成多个频率范围内的信号,以供不同的电路进行处理。分频器广泛应用于通信、测量和音频系统中。 分频器

CAN时钟分频器在CANbus模块上不执行任何操作的原因?

我一直在使用 dsPIC33CH128MP506 进行一些 CANbus 通信。

它能够进行CAN-FD,并且有两个独立的波特率分频器,用于标称波特率和数据波特率。它们是:C1NBT

发表于 01-22 06:36

Sigma-Delta小数分频PLL中的分频器该怎么做?

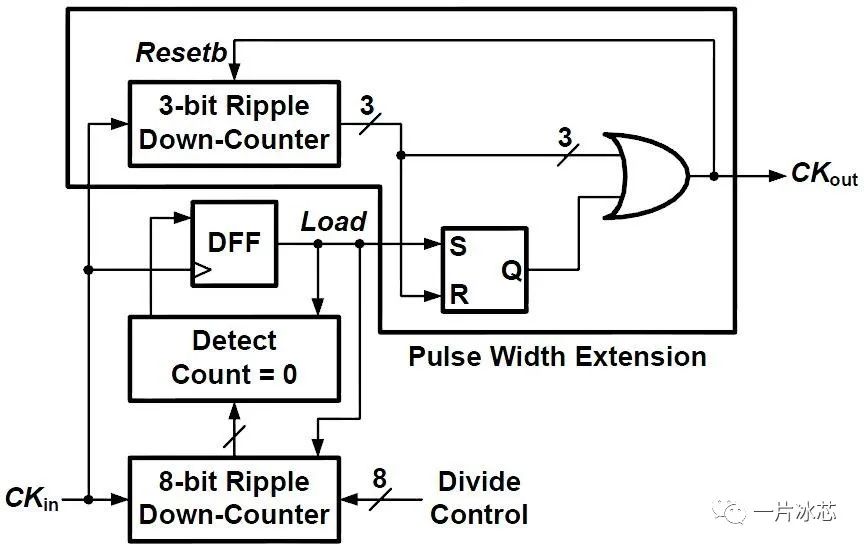

文献给出的分频器结构如图1所示。该分频器最高输入频率(f~in~)为16.3GHz,也就是一个周期只有(T~in~,T ~in~ = 1/ f~in~)61.3ps。

分频器的常见用途

分频器是一种电子设备,其主要作用是将输入信号的频率降低到较低的频率。它通过将输入信号分为若干个等分的周期,每个周期输出一个脉冲或波形,从而实现对输入信号频率的降低。

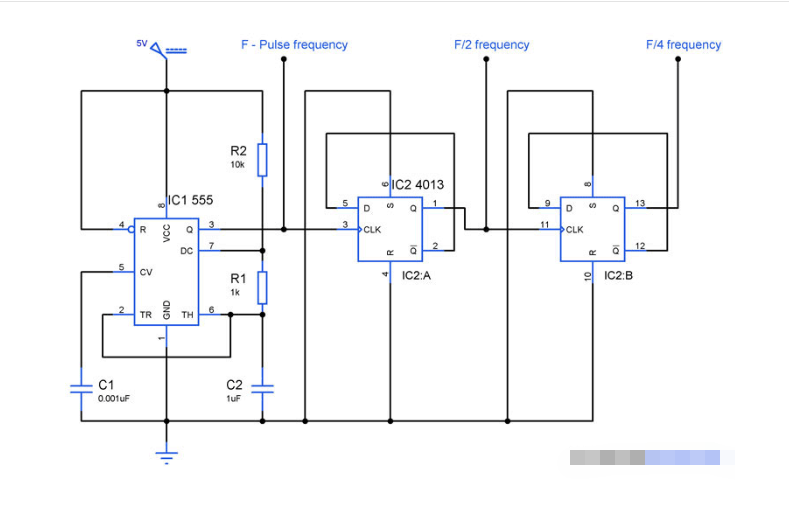

使用IC555和IC4013构建的分频器电路

曾经遇到过这样一种情况,即您只有一个特定频率的信号源,需要获取多个频率的信号。如果是,这种电路可能是您需要在设计中使用的电路。上述电路是一个分频器,能够通过一定的因素对输入时钟频率进行

自制一个简易的音箱分频器电路

自制一个简易的音箱分频器电路

评论