混合信号设计结合了模拟与数字电路的强大功能和优点。常用的混合信号架构是其中每个模块通过数字逻辑电路来控制。这种设计利用数字逻辑电路的可靠性和运算能力控制传统模拟电路。

由于便于在整个设计过程中修改,数字逻辑电路特别适合保持数字逻辑控制环路的“智能”功能。模拟电路应该尽可能简单和直接。可能的情况下,解码、延迟及其它功能应采用数字方式实施。

与模拟电路不一样,数字逻辑电路不受偏差或工艺变量的影响,更便于控制或完全避免抖动等现象。某些功能在逻辑电路中配置非常容易,如保持特定不确定值的控制环路。这种电路基板占用面积小、抗噪声并易于部署。

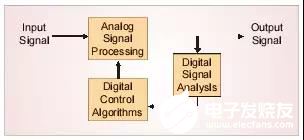

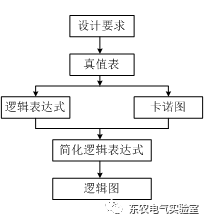

图1,混合信号反馈环路框图。

典型控制策略如图1所示。输入信号进入某种类形的模拟信号处理电路。数字逻辑电路对输出信号进行分析,数字控制运算电路更新模拟电路的行为。增益、偏置、钳位电流及滤波器中心频率是这种方式控制的典型量。

举例

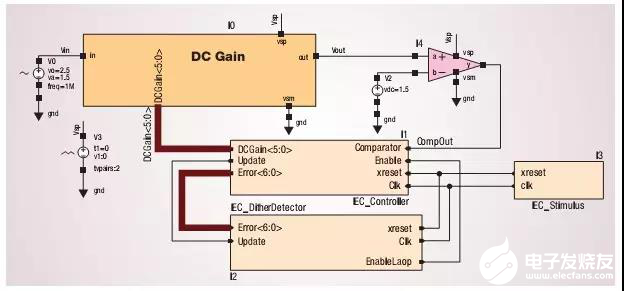

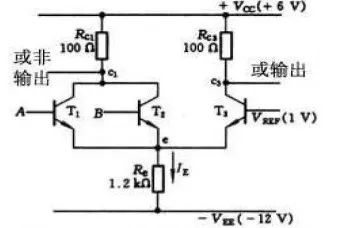

我们以图2所示自动增益控制电路为例加以说明。输入信号假定为简单的正弦波,经模拟信号处理电路进行振幅调整。(DC)增益块执行本例整个模拟信号处理过程。它接收六位代码,按 ±6dB调整信号(DC)增益。

图2,自动增益控制:DC块执行全部模拟信号处理。

比较器是“数字信号分析仪”最简单的例子,输出信号与1.5V参考电压进行比较。信号振幅调整到其最小值刚好开始启动比较器。标有IEC_Controller的模块含有数字控制运算电路。这个控制器的基本概念很简单:

1.测量时钟周期中比较器输出结果低的部分。

2.定期比较这部分周期与预期目标值。

3.如果计数过高,下调DC增益。如果过低,上调DC增益。

这个电路的另一部分是“抖动检测器”,嵌入IEC_DitherDetector模块中,用来确定DC增益值是否处于稳定状态。稳定后,锁定控制环路的输出。这样可以避免电路在代码之间随机漂移。

数字环路考虑因素

任何控制环路必须有一个目标(预期值或条件),这个AGC电路的目标是每256个周期1个比较器高计数,或占空周期约为0.4%。

选择这个值是因为产生的误差(0.4%)可以接受。不过,每种应用情况不同,必须认真选择误差信号的动态范围。

称作ComparatorCounter的计数器用来统计比较器输出结果高的时钟周期数。控制环路生成误差信号,称为Error(误差),即实际计数减去目标值所得结果。

环路输出限制为不上溢或下溢。此外,每次更新事件清零ComparatorCounter,从而开始另一个256时钟周期测量。

多个反馈环路考虑因素

系统仅有一个控制环路时,它的漂移误差并不重要,但是如果系统有多个环路,漂移误差会明显放大。

控制理论指出:当系统有多个环路时,系统调整误差所需的时间呈几何级增长,其阶数与环路数量一致。

数字控制环路的时间常数很容易改变。如果环路输出宽度为N位,误差积分器可宽出几位,如N+2。然后考虑预留一部分最小有效位不用,有效延缓环路关闭。利用一个很小的附加逻辑,时间常数还可以成为动态的,根据其它环路的状态变化。

抖动与稳定

抖动一词描述控制环路在两个(或多个)离散输出代码之间来回摆动的情况。这是这类控制环路的常见现象,某些应用中这种现象无所谓。

在不允许抖动的应用中,可采用一个小的附加逻辑电路消除抖动。检测抖动最简便的方法是观察误差信号。当误差信号小时,环路接近其预期目标。适当时间长度内保持很小误差时,环路误差积分器停用,防止进一步更新。

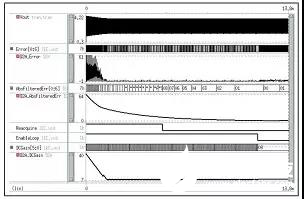

图3,选取和锁定的波形输出。

确定误差信号在“适当时间”内保持很小状态需要采用低通滤波。单极IIR(无限冲激响应)滤波器可能是最简单的低通滤波器。这种滤波器易于配置在数字逻辑电路中。

可采用另一(选装)计数器延长环路完全稳定时间,即使其过滤的误差信号小到可以接受之后。本例中,这个计数器称为SettleCounter,每当过滤误差信号过大时,这个计数器清零。当过滤的误差信号小到可接受的程度时,计数器开始累计,每个更新事件一次。当达到最大值时,控制环路误差积分器停止工作,环路输出不再变化。

环路本身不间断持续运行(其误差信号必须连续跟踪输入信号的变化),但输出值锁定,从而不能抖动。当输入信号显著变化时,过滤的误差信号增加,环路解锁并开始重新选取信号。

结果

示例电路的动作如图3所示。输出信号Vout最初过大。DCGain值下移,每256个时钟周期下降一个单位,直到误差信号接近零为止。AbsFilteredError信号滞后于误差信号,最终低于重新选取阈值。这时,重新选取(Reacquire)下降。当SettleCounter达到其最大值后LoopEnable下降,环路输出锁定。

与传统全模拟控制环路相比,混合信号控制环路具有许多优点。它们便于实施并可保证稳定性,特别是与专门设计的抖动检测器配合使用时。数字逻辑电路具有独特的控制环路“锁定”能力,这是一种具有极大实用价值的功能。

误差积分器和环路误差滤波器策略使这种构件方法适用于解决大量不同的问题。可行的情况下,可结合数字和模拟设计方法各自的优势开发小型、可靠、易于实施的新型控制结构。

-

混合信号

+关注

关注

0文章

339浏览量

64804

发布评论请先 登录

相关推荐

混合信号常用设计 是通过每个模块数字逻辑电路来控制的

混合信号常用设计 是通过每个模块数字逻辑电路来控制的

评论