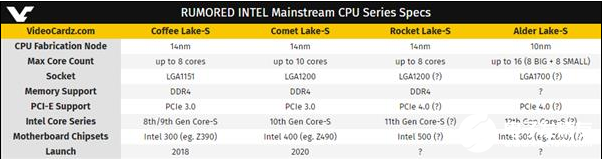

根据Intel的路线图,2022年的时候会有十二代酷睿,代号Alder Lake,制程工艺应该是10nm了。最新的爆料显示这一代终于能上16核了,还支持PCIe 4.0,更神奇的是架构跟AMR学了一招。

VC网站得到的最新资料显示,下下下代的Alder Lake处理器(惯例来说是十二代酷睿)终于能做到16核架构了,但是这个架构有点奇特,不是常见的16个同一核心,而是分为两组——大核心8个、小核心8个。

这很容易让人联想到ARM公司在Cortex-A系处理器使用的big.LITTLE大小核架构,简单来说就是将高性能核心与低功耗核心搭配使用,最大好处就是可以降低能效。

Intel这边对大小核技术其实也有实际尝试了,那就是3D封装的Lakefield,就是4小核+1大核的架构,大核是Sunny Cove,小河是Atom产品线采用的Tremont核心,主要用于低功耗便携本等产品。

如果Alder Lake用上8+8架构来做16核,那说明Intel对大小核的掌握已经很到火候了,可以在主流CPU市场上推进了。

当然,严格来说Alder Lake处理器还有另外的核——GT1核显,不知道为何核显规模反而在Alder Lake弱化了,目前至少都是GT2核显级别的配置。

除了CPU核心的配置之外,Alder Lake处理器的TDP功耗也会增加,普通版会提升到80W,高端的会是125W,这跟10核的Comet Lake-S是一样的。

不过爆料显示Intel还在研究扩展TDP的方法,尝试做到150W TDP,这时候TDP越高意味着CPU频率、性能会越高,是好事。

除了大小核的16核架构之外,Alder Lake处理器还有一些全新的升级,PCIe 4.0是没跑了,这是Intel首个正式支持PCIe 4.0的桌面处理器。

至于DDR5,现在还没法确认,不过考虑到2022年的时间点,上DDR5应该不意外。

最关键的一点就是,Intel又要换插槽了,这次会升级到LGA1700插槽,之前也有过爆料了,所以不用太介意。

这也意味着即将发布的LGA1200插槽寿命不会太长,主要用于14nm Comet Lake及14nm Rocket Lake,也就是十代酷睿、十一代酷睿桌面版,回到之前2代升级一次的节奏。

-

cpu

+关注

关注

68文章

10437浏览量

206527 -

intel

+关注

关注

19文章

3451浏览量

184770

发布评论请先 登录

相关推荐

Intel 10nm酷睿上16核 大小双8核+PCIe 4.0

Intel 10nm酷睿上16核 大小双8核+PCIe 4.0

评论