作为摩尔定律最忠实的追随者与推动者,台积电、三星已经挑起3nm的战局。据悉,三星已经完成了首个3nm制程的开发,计划2022年规模生产3nm芯片,此前台积电也计划2022年量产3nm。如无意外,3nm芯片将在后年到来,对半导体产业链提出新的挑战。

双雄剑指3nm

《韩国经济》杂志称,三星已成功研发出首个基于GAAFET的3nm制程,预计2022年开启量产。与7nm工艺相比,3nm工艺可将核心面积减少45%,功耗降低50%,性能提升35%。

按照三星的研发路线图,在6nm LPP之后,还有5nm LPE、4nm LPE两个节点,随后进入3nm节点,分为GAE(GAA Early)以及GAP(GAA Plus)两代。去年5月,三星的3nm GAE设计套件0.1版本已经就绪,以帮助客户尽早启动3nm设计。三星预计该技术将在下一代手机、网络、自动驾驶、人工智能及物联网等设备中使用。

以2022年量产为目标的台积电,也在按计划推进3nm研发。台积电首席执行官CC Wei曾表示,台积电在3nm节点技术开发进展顺利,已经与早期客户进行接触。台积电投资6000亿新台币的3nm宝山厂也于去年通过了用地申请,预计2020年动工,2022年量产。

台积电在7nm节点取得了绝对优势,在5nm也进展顺利,获得了苹果A14等订单。但三星并没有放松追赶的脚步,计划到2030年前在半导体业务投资1160亿美元,以增强在非内存芯片市场的实力。台积电创始人张忠谋日前对媒体表示,台积电与三星的战争还没有结束,台积电只是赢得了一两场战役,可整个战争还没有赢,目前台积电暂时占优。

制程如何走下去

众所周知,制程越小,晶体管栅极越窄,功耗越低,而集成难度和研发成本也将成倍提高。3nm是一个逼近物理极限的节点,半导体业内专家莫大康向《中国电子报》记者表示,3nm是一个焦点,不能仅靠台积电、三星的推进,还要看制造商和设备商等产业链各个环节的努力,例如环栅结构(GAA)的导入,EUV的高数值孔径镜头等。

3nm首先对芯片设计和验证仿真提出了新的挑战。集邦咨询分析师徐绍甫向记者表示,制程微缩至3nm以下,除了芯片面积缩得更小,芯片内部信号如何有效传递是一大关键。设计完成后,如何确保验证和仿真流程的时间成本不会大幅增加,也是芯片设计的一大挑战,需要EDA从业者的共同努力。此外,在做出更小的线宽线距之后,量产和良率拉抬是非常困难的事,需要制程技术的不断优化。

为了更快实现制程迭代和产能拉升,三星研发了专利版本GAA,即MBCFET(多桥道FET)。据三星介绍,GAA基于纳米线架构,由于沟道更窄,需要更多的堆栈。三星的MBCFET则采用纳米片架构,由于沟道比纳米线宽,可以实现每堆栈更大的电流,让元件集成更加简单。通过可控的纳米片宽度,MBCFET可提供更加灵活的设计。而且MBCFET兼容FinFet,与FinFet使用同样的制作技术和设备,有利于降低制程迁移的难度,更快形成产能。

3nm也对光刻机的分辨率及套刻能力提出了更高要求。针对3nm节点,ASML将在NXE 3400C的下一代机型导入0.55高数值孔径,实现小于1.7nm的套刻误差,产能也将提升至每小时185片晶圆以上,量产时间在2022—2023年。徐绍甫表示,3nm对于光刻机曝光稳定度与光阻剂洁净度的要求更加严苛。加上3nm需要多重曝光工艺,增加了制程数目,也就意味缺陷产生机率会提高,光刻机参数调校必须缩小误差,降低容错率。另外,清洗洁净度、原子层蚀刻机与原子层成膜机等设备的精度也要提高。

针对5nm及以下节点的封装,台积电完成了对3D IC工艺的开发,预计2021年导入3D封装。3D IC能在单次封装堆叠更多的芯片,提升晶体管容量,并通过芯片之间的互联提升通信效率。赛迪智库集成电路研究所高级分析师王珺、冯童向记者表示,台积电的中道工艺主要是通过制造和封装的紧密结合提高晶体管密度,会是发展路径之一,可进行模块化组装的小芯片(Chiplet)也是比较热门的发展路径。

何为增长驱动力

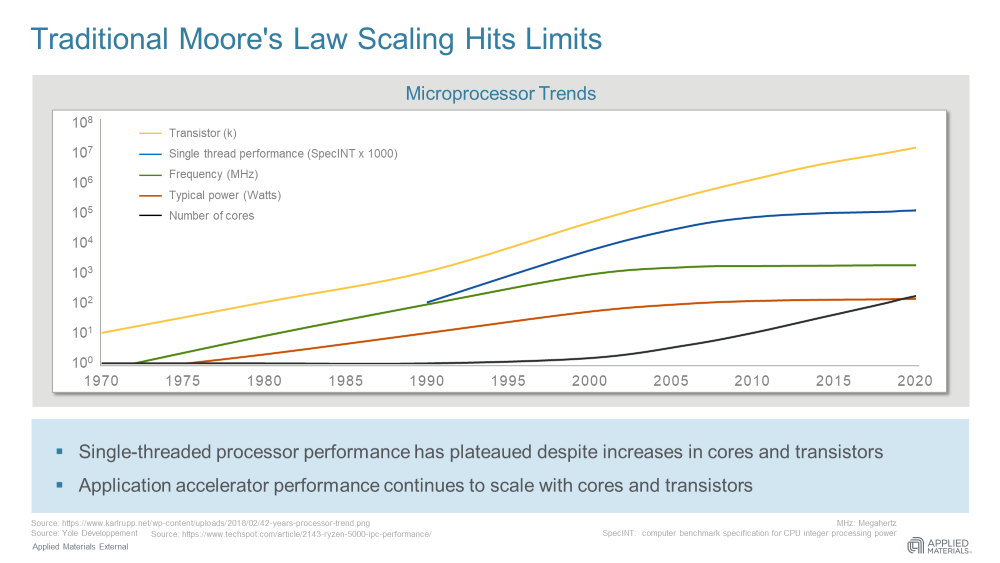

2014—2019年,手机和高性能运算推动着先进制程按照一年一节点的节奏,从14nm走向5nm。中芯国际联合CEO赵海军表示,成功的研发方法,不变的FinFet架构、设备和材料的配合,是推动14nm向5nm发展的重要因素。

目前来看,手机和高性能计算依旧是推动摩尔定律前进的重要动力。徐绍甫指出,在应用层面上,智能手机是3nm制程的重要战场,手机芯片从业者能负担高昂的研发经费,庞大的市场总量也能够分担其研发费用。另外,HPC应用,如CPU与GPU等,需要3nm制程来提升性能表现。芯谋研究总监王笑龙表示,3nm将主要面向对高速数据处理和传输有需求的产品,如CPU、网络交换机、移动通信、FPGA和矿机等。

3nm不是先进制程的终点,台积电对2nm已经有所规划,将以2024年量产为目标进行研发。比利时微电子研究中心(IMEC)在2019年10月召开的技术论坛上曾展示迈向1nm工艺节点的技术路线图。王珺、冯童表示,伴随高数值孔径EUV光刻机、选择性化学蚀刻剂、原子层精确沉积技术等的应用,未来10年,摩尔定律将继续延续。

制程要走下去,需要工艺路径的探索,也需要找到相应的商业场景。王笑龙向记者表示,对于资金密集型工艺,如果无法在消费市场得到应用,就难以收回成本,也不具备经济价值。徐绍甫表示,2nm之后的应用性与必要性还难以定义,从实验室走向量产具有相当的难度,必须具备获利能力才具有开发意义,在材料选择、制程技术、后段晶圆封装上势必要持续优化。

责任编辑:wv

-

三星电子

+关注

关注

34文章

15601浏览量

180102 -

台积电

+关注

关注

43文章

5262浏览量

164772 -

摩尔定律

+关注

关注

4文章

622浏览量

78516

发布评论请先 登录

相关推荐

2024年全球与中国7nm智能座舱芯片行业总体规模、主要企业国内外市场占有率及排名

英特尔CEO基辛格:摩尔定律仍具生命力,且仍在推动创新

后摩尔定律时代,Chiplet落地进展和重点企业布局

摩尔定律不会死去!这项技术将成为摩尔定律的拐点

超越摩尔定律,下一代芯片如何创新?

半导体行业产生深远影响的定律:摩尔定律!

什么是摩尔定律?

台积电在7nm节点取得绝对优势 摩尔定律将继续延续

台积电在7nm节点取得绝对优势 摩尔定律将继续延续

评论