我们经常听到身边的硬件工程师们提到关于信号完整性的话题。 那么信号完整性具体是指什么呢?

信号完整性(Signal Integrity:简称SI),指信号线上的信号质量,是信号在电路中能以正确时序和电压做出响应的能力。

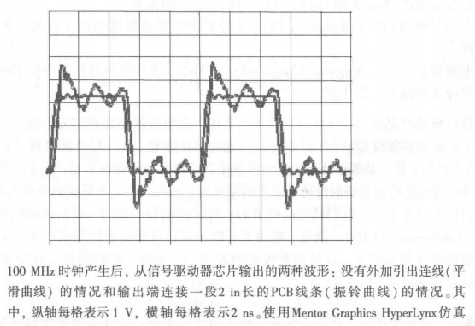

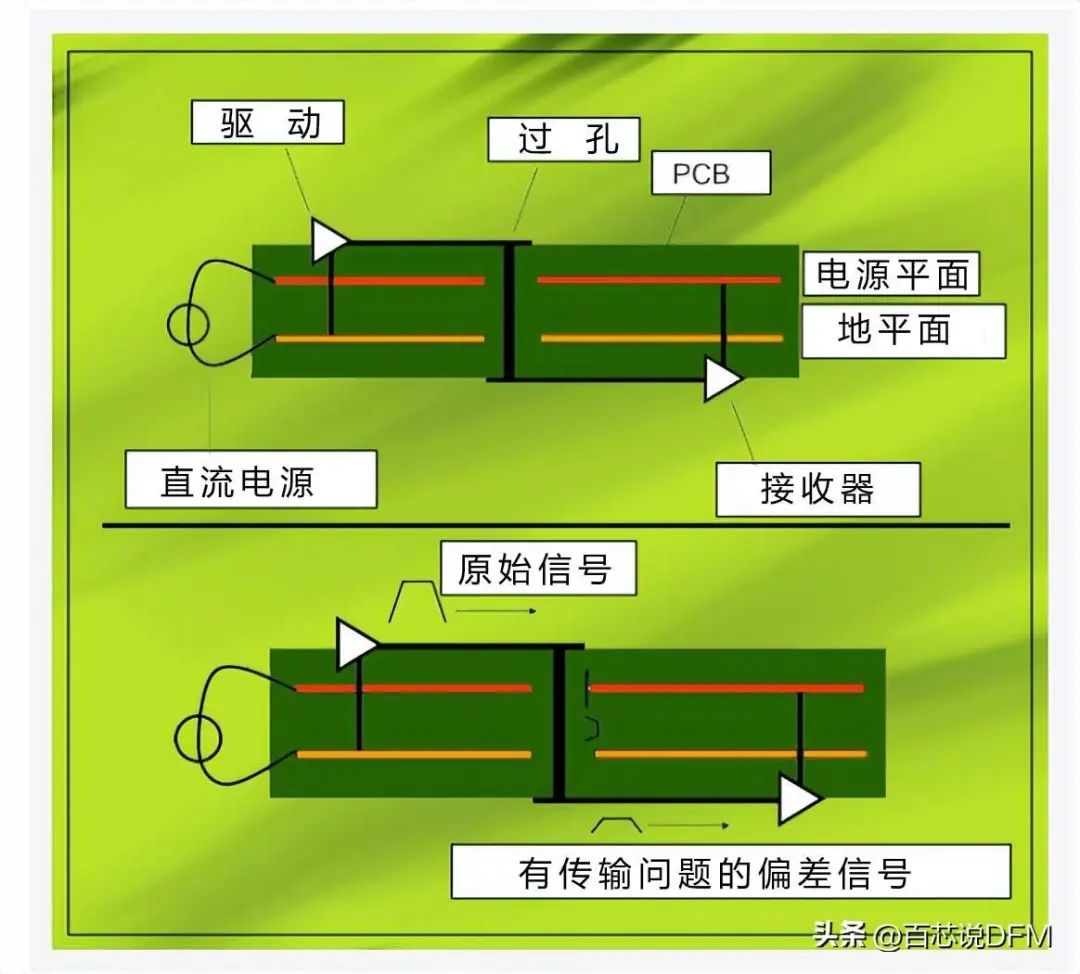

当电路中信号能以要求的时序、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性。信号完整性问题包括误触发、阻尼振荡、过冲、欠冲等,会造成时钟间歇振荡和数据出错。

设计环节中,信号完整性是必不可少的考虑因素,当然,在信号测试和调试环节,我们也应对信号完整性问题引起重视,否则会引起测量结果误差,影响工程师判断,调试和改进电路的方向。

在基础的电子信号测量中,我们通常会选用示波器来对信号进行测量。因此,如何选择一款有利于信号完整性测量的示波器尤为重要。

接下来我们主要从几个大方向介绍了哪些因素会影响信号完整性的测量。(文中主要讨论的为数字示波器)。

No.1

带宽

带宽是我们对于示波器最直接认知的一个指标,他指的是当频率提高到某个值,输入信号幅值刚好被衰减3dB 时所对应的频率点。

对于信号完整性测量来说,带宽越高越好。这句话从某种意义上来讲是正确的。

我们知道,任何信号都可以分解成无数次谐波的叠加。理论上来说,带宽覆盖被测信号能量的99.9%,测量的误差可以小于3%。

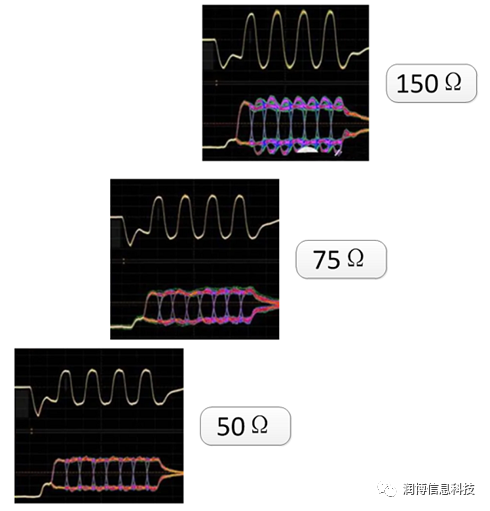

根据我们一贯的经验,带宽的要求是被测信号的5倍。但是有这样一种信号,他的基频很低,但是却有快速的上升时间,很有可能会引起振铃现象,这意味着高次谐波能量占的比重大。

这个时候,5倍法不再适用,并且我们无法得知,哪个频率点我们刚好能覆盖99.9%的能量。如果选择的带宽较低,则意味着这些高频分量会被漏掉,我们没法准确地在示波器上重建信号。

所以,我们在考虑如何选择示波器时,不仅要考虑带宽的影响,同时也需要考虑到上升时间的影响。这两者都是影响信号完整性的重要因素。

No.2

上升时间

事实上,上升时间并不仅仅指前文我们提到的信号的上升时间,对于示波器来讲,也是具有上升时间这个指标的。

我们为什么把上升时间拿到和带宽同等的高度来分析它?

试想,两个具备相同带宽性能的示波器却具有不同的上升时间。那么对于我们测量信号而言,选择哪一个才能更加准确地测量信号?

尤其是在测量一些快沿和高速串行信号等复杂信号时。

首先我们先明确示波器的上升时间指的是什么。

理论上来讲,他是示波器放大器的阶跃响应,反映的是示波器前置放大器的瞬态响应能力。基于RC模型的高斯响应我们可以推导出:

上升时间=0.35/带宽

事实上,实际示波器带宽和上升时间的关系可能是0.35-0.5。这取决于示波器频响曲线的形状,有些示波器使用的是高斯型,有些是四阶贝塞尔型,有些是升余弦型。

但在实际测量中,示波器配合探头测量信号,这样,示波器和探头就组成了一个系统,我们可以得到以下的结论:

Rise_Time Measure2

=Rise_Time scope2

+Rise_Time Probe2

+Rise_Time Signal2

示波器和探头的上升时间越小,越有利于真实地重建信号,对信号测量的误差影响越小。

这意味着就算是相同的带宽,示波器测量信号完整性的能力还可以通过示波器的上升时间来加以区分。

示波器真实的上升时间无法通过带宽来进行计算,最可靠的方法只能是通过一个理想的阶跃信号去测量。

No.3

频率响应

除了考虑上述带宽和上升时间以外,同时我们也应考虑在带宽内,是否具有平坦的响应。

不平坦的带内响应,很有可能会导致信号的失真。所以,我们在示波器具备相同带宽的同时,我们也可以要求示波器厂商提供示波器的频响图,以便考察。

如图为SDS3000X示波器的幅频特性曲线,可以看出,4个通道在带内的曲线都很一致且平滑。

图1 SDS3000X示波器幅频特性曲线

No.4

ADS

数字示波器的本质是将模拟信号采样为一个一个的离散点。

连续的模拟信号在转换为数字信号的离散化过程中,由于没有无限数量的离散化的数字电平来重组连续的模拟信号,实际的模拟电压值与对应的数字化电平值之间总会有偏差,这个偏差值叫量化误差。

而模数转化器(ADC)的位数则决定了示波器的最小量化电平,也确定了数字示波器的分辨率。

ADC的位数越高,则分辨率越高。8位的ADC代表了28=256个量化级别;10位的ADC则代表了210=1024个量化级别;12位的ADC代表了212=4096个量化级别。

ADC的位数越高,则意味着量化误差则越小,越有利于信号完整性测量。

除此之外,在我们只能选择既定的ADC位数的示波器之后。要想获得最佳的分辨率,要尽量让波形占满栅格,才能充分利用ADC的范围。如果只让波形占1/2栅格,则测量精度会下降到7-bit。因此合理地选择选择垂直缩放的设置,能获得更加精确的测量结果。

如下图所示为分别让信号占据满栅格,1/2栅格,1/4栅格….的情况,可以看到,测量的结果出入很大。

图2不同情况下的测量结果

No.5

ENOB

ENOB(Effective number of bits)是衡量示波器动态性能的一个指标。

一些示波器厂商会给出ADC的ENOB值,从某种程度上来讲,8位的ADC的确能够提供8位的精度和分辨率,这只是针对DC信号或者一些低速信号而言。

随着信号速度的提高,动态数字化性能会显著下降。当达到某一特定临界值,8位的ADC可能降到6位或者4位或者更低的有效位数。

数字转化器性能的下降主要表现为信号上的噪声水平增加。此处的噪声水平增加主要是指输入信号和数字化输出中叠加的随机误差。

我们可以用信噪比(SNR)来衡量此系统的好坏。

SNR=

ENOB=(SNR-1.76)/6.02

当然,对于示波器而言,单纯地讲ADC的ENOB是没有意义的,评估整个示波器系统的ENOB才具有实际意义。

例如一个ADC具有非常优秀的ENOB,但若是前端噪声较大,则会影响整个系统的ENOB.

在SDS2000X示波器中,提供了增强分辨率模式(ERES采集模式),通过数字滤波的方式降低噪声的带宽,能有效提高信噪比,最高可等效增强3 Bit ENOB,等效提高了示波器的垂直分辨率,且无须依赖于信号的周期性和触发点的稳定。这个模式有利于于信号完整性测量。

图3 SDS2000X增强分辨率模式

我们在判定整个系统的ENOB是否会影响信号的测量以及影响信号完整性时,一定要留意自己需要测量的是什么信号。

例如高速串行信号在一些频点上具有谐波,这些谐波可以通过示波器系统而不受ENOB降低的影响。

No.6

噪声

在示波器不外接任何信号的前提下,我们依然可以在示波器的显示屏上观察到噪声信号,我们称这个信号为示波器的底噪。

示波器的噪声可能有很多来源,包括示波器的模拟前端,模数转化器,探头甚至是连接测量电路的电缆。

有利于信号完整性测量的示波器应该具有较小的噪声。

我们在测试仪器噪声的时候,还要注意影响噪音测试结果的因素很多,比如带宽、采样率、通道垂直分辨率、水平时基和通道耦合方式等。

总体来说,业界对此的共识如下:

带宽越高,噪声越大,因为带宽越高采集到的信号谐波分量越丰富。

水平时基分辨率越低,噪声越大,即时基格度越粗,噪声显示越大。

对地耦合方式下噪音最小,因为外界信号和电磁环境干扰被隔离;如果要比较真实的仪器噪音,建议DC耦合,此时全带宽开启,所有示波器处于真实的测试环境中。

如果我们需要观察小信号或者一些微小变化,那么我们需要选用底噪更小的示波器。

如下我们比较了几款市场上较常见的示波器的底噪:

图4 SDS3000X底噪

图5 甲品牌底噪

图6 乙品牌底噪

-

示波器

+关注

关注

110文章

5644浏览量

181735 -

信号

+关注

关注

11文章

2633浏览量

75367 -

硬件工程师

+关注

关注

167文章

346浏览量

73776

发布评论请先 登录

相关推荐

从信号完整性角度谈选择示波器

从信号完整性角度谈选择示波器

评论