FPGA的应用越来越广泛,随着制造工艺水平的不断提升,越来越高的器件密度以及性能使得功耗因数在FPGA设计中越来越重要。器件中元件模块的种类和数量对FPGA设计中功耗的动态范围影响较大,对FPGA的电源功耗进行了分析,并介绍了如何利用Altera公司的PowerPlay Early Power Estimator这一工具在设计前期尽可能准确地估计功耗并通过估计功耗对硬件设计进行优化选择。

引 言

当前FPGA应用越来越广泛,在高性能FPGA设计中,越来越高的器件密度以及性能使得功耗因数更加重要。大规模器件在实现更多的系统功能,以更高的速度运行并完成更高级的功能的同时,功耗必然会更大。开发者在面对此类设计时会在功耗方面遇到很多挑战。对通过芯片重新编程就能够修改的FPGA设计,在设计过程中尽早完成电源供电和散热方案的设计有利于加速整个系统的实现。设计中系统组件应保持在一定的功耗预算范围内,如果超出预算则需要重新设计供电电源及散热方案,这会延长设计周期。同时较大的电源和散热硬件会增加成本,降低功耗也就降低了系统总成本。并且当设计中需要的风扇和散热硬件越多,系统故障的概率就越大,这将影响系统的可靠性。综上所述,做好早期功率估算具有重大意义。

1、 FPGA器件功耗分析

当前,随着FPGA器件的封装尺寸越来越小,密度越来越大,同时系统对器件的性能和可靠性要求不断提高,功耗预算对电源方案,散热方案及系统故障影响的问题已不容忽视。

1.1 功耗的组成

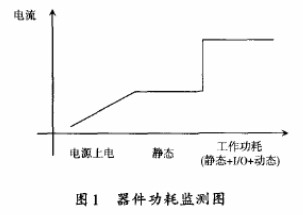

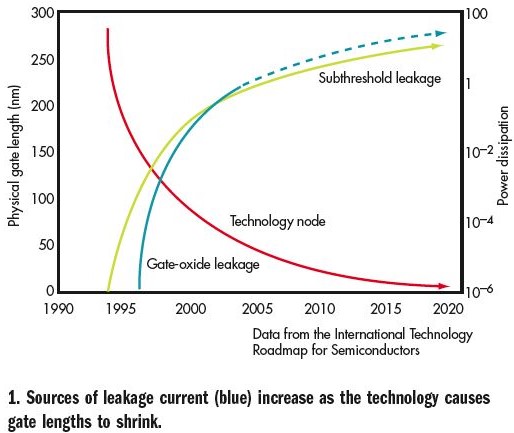

功耗一般由两部分组成:静态功耗和动态功耗。静态功耗也称为待机功耗,是指逻辑门没有开关活动时的功率消耗,主要是由晶体管的漏电流引起,由源极到漏极的漏电流以及栅极到衬底的漏电流组成,图1中静态部分显示了器件的静态功耗。图中最后阶段显示的是器件正常工作时的功耗,工作功耗同时包括静态功耗,I/O以及动态功耗。动态功耗是指逻辑门开关活动时的功率消耗,主要由电容充放电引起,其主要的影响参数是电压、节点电容、工作频率和资源使用情况,不同设计时期的动态功耗和相应的总功耗会有很大的差别。在传统器件中动态功耗占据主要地位,但在新的28 nm工艺的器件中,静态功耗的比重增长很大,基本和动态功耗处于同等地位。同时根据FPGA设计面向对象的不同,功耗的比重也会有差别。当设计面向算法时,动态功耗将占较多比重,当设计面向控制功能时,静态功耗将占较多的比重。

1.2 静态功耗

静态功耗的产生主要取决于所选的FPGA产品,一般不会随着设计资源的使用情况而变化,但是静态功耗也会受到器件所选择的工作模式、I/O的使用、工作温度以及所选器件电源的影响。使用逻辑单元较多的器件含有较多的晶体管,因此其静态功耗会高一些,所以设计者应查看所选器件的数据资料,详细了解其静态功耗。在不同温度环境中,静态功耗也会随着温度的升高而增大,此时高效的散热解决方案能有效地解决这一问题。因此在设计电源时,应针对选择的器件和工作环境,选择适合的静态功耗规范。

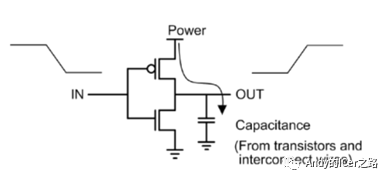

1.3 动态功耗

不同的设计有不同的动态功耗,当开发低功耗FPGA设计时,动态功耗是更可控的功耗分量,如下式:

影响动态功耗的因素包括:器件中晶体管电容充电,工作电压,晶体管开关的瞬间短路电流功耗,设计的工作频率,以及被称为电路活动的每一时钟周期触发器开关的次数。设计人员根据设计要求决定工作电压,工作频率以及信号活动。信号活动包括触发率和静态概率。信号触发率是精确估算动态功耗的关键因素,随着触发率的增加,动态功耗也线性增大。而静态概率主要影响静态功耗。

1.4 低功耗的优点

低功耗器件的优点主要有以下几项:首先可以选用低成本的电源系统,进而可以使用更少的元件和更小的PCB板面积,为设计节约了成本。其次低功耗器件引起的结温更小,因此可以防止热失控,可以少用或不用散热器,而且结温的降低可以提高系统的可靠性。最后低功耗可以延长器件的使用寿命,器件的工作温度每降低10 ℃,使用寿命延长1倍。因此,在FPGA设计中,降低功耗直接提高了整个系统的性能和质量并降低了成本,对系统的开发有积极作用。

通过对FPGA功耗的相关组成和影响功耗相关因素的分析,设计者通过优化设计,可以在FPGA设计中实现低功耗。通过一款具体的FPGA产品了解其低功耗的解决方式,可以为设计者提供指导。FPGA均可在相应的操作环境下进行仿真,从而了解功耗的具体使用情况,针对相应的情况进行修改。

2、 对功耗进行仿真建模

设计的早期,尽可能快地估算系统功耗使用情况,有助于开发人员加快产品设计进度,方便快捷精确的功耗估算工具是开发人员最好的助手。Altera公司推出了PowerPlay Early Power Estimator(EPE)这一小巧实用的工具,在基于表格的页面分析环境中对功耗分析进行仿真建模,用EPE报告的信息可以选择电源供电的设计,满足设计要求。

2.1 EPE的用户界面

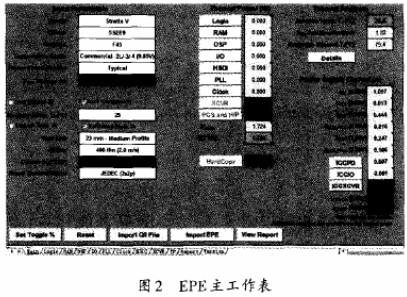

EPE的主工作表如图2所示,表中给出了当前设计的功耗概览,列举了器件基本信息、总功耗、热分析和电源大小等信息。同时底部显示了包括Logic标签、RAM标签、I/O标签、DSP标签、PLL标签、Report标签等。

2.2 EPE的使用方法

EPE的使用方法非常方便,设计人员在各个页面输入相应的器件的基本信息(包括器件型号、内核电压、环境温度、散热解决方案特性等)、资源利用率、触发率、时钟频率等信息。然后点击View Report或Report标签就可以查看功耗估算结果报告,报告会给出器件的散热分析,每一类器件资源的功耗使用情况,以及每一电源的功耗使用情况等,便于设计人员设计相应的电源模块。在主工作表底部选择相应的资源标签可以转到相应资源区域的详细信息,可以对设计中每一模块的资源使用情况进行统计分析。EPE估计功耗使用情况的准确性依赖于设计者提供的参数信息,例如准确的触发率、时钟频率、含有信号活动信息的仿真建模情况、逻辑单元数量等资源使用情况以及工作的环境情况等。提供的信息越精确,功耗估算的结果就越精确。

2.3 EPE中的重要参数——触发率

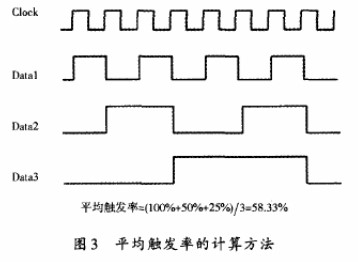

在使用EPE估计功耗时,一些关键的参数值对功耗估计的结果影响较大,特别是触发率的数值。要将功耗和触发率联系起来,可以认为在状态改变的时间间隔期间,信号的每一次转变需要一定数量的能量去改变内部电路的状态。触发率被定义为每秒钟信号转换的平均次数,以百分比表示。在触发器中,如果系统最大时钟频率为100 MHz,所有触发的触发器的平均输出频率为10 MHz,那么所有触发器的平均触发率为20%。由于这种类型的触发器都是在信号活动的时钟边沿(上升沿)触发,100%的触发率则表示一个触发器的翻转频率为50 MHz。设计者应模拟每个模块中的所有触发器输出的时钟,并计算触发器输出相对于时钟变化的概率。FPGA器件中不同模块的触发率数值不同,在数据路径逻辑中,触发率的范围从6%12%。随机逻辑中,如编解码的触发率大概在50%,而控制逻辑的触发率最高可接近100%。以上都是作为估计触发率数值的一般准则,而真实设计部分的触发率完全取决于设计和数据集。例如,重置信号是一个控制信号,它可能有一个非常低的触发率。在功能仿真中需要准确的计算所有模块的平均触发率。图3给出了计算平均触发率的一个例子。

图4的报告结果给出了三种平均触发率对功耗的影响结果,从左到右平均触发率的值依次为7%,12.5%,30%。随着触发率的提高,静态功耗基本没有变化而动态功耗以及相应的总功耗会线性提高。设计者可以根据自身设计需求(面向算法或是控制)和平均触发率的计算结果,合理设置触发率数值大小。

3 、结语

功耗的早期估计对于FPGA系统设计十分重要是基于两点考虑:系统电源的大小和散热。充分理解FPGA的工作功耗、静态功耗、动态功耗、内核与I/O资源情况将影响降低功耗的策略。如何使用简单易用的工具,针对设计中目标器件的类型和设计的特性,高效准确的完成早期功率估计将有助于设计者加速整个系统的设计实现。

责任编辑:gt

-

FPGA

+关注

关注

1599文章

21270浏览量

592788 -

仿真

+关注

关注

50文章

3871浏览量

132129 -

晶体管

+关注

关注

76文章

9024浏览量

135019

发布评论请先 登录

相关推荐

FPGA系统设计的静态功耗和动态功耗分析与进行仿真建模

FPGA系统设计的静态功耗和动态功耗分析与进行仿真建模

评论