本文主要分析一下在高速PCB设计中,高速信号与高速PCB设计存在一些理解误区。

误区一:GHz速率以上的信号才算高速信号?

提到“高速信号”,就需要先明确什么是“高速”,MHz速率级别的信号算高速、还是GHz速率级别的信号算高速?

传统的SI理论对于“高速信号”有经典的定义。

SI:Signal Integrity ,即信号完整性。

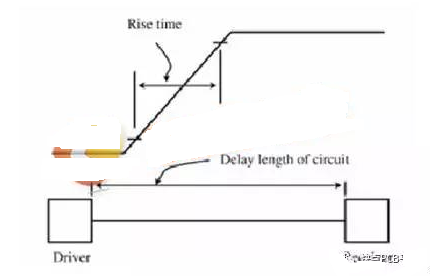

SI理论对于PCB互连线路的信号传输行为理解,信号边沿速率几乎完全决定了信号中的最大频率成分,通常当信号边沿时间小于4~6倍的互连传输延时的情况下,信号互连路径会被当做分布参数模型处理,需要考虑SI行为。

所谓“高速”,是指“信号边沿时间小于4~6倍的互连传输延时”,可以看出电路板传输的信号是否为“高速”,不只取决于信号的边沿速率,还取决于电路板线路的路径长度大小,当两者存在一定的比例关系时,该信号应该按照“高速信号”进行处理。

误区二:有了仿真软件平台就可以做好高速PCB设计?

EDA设计软件平台集成了高速信号仿真功能,这对于高速PCB设计的规则制定与执行,信号质量仿真与评估都有很大的帮助。

但是,在PCB实际设计过程中,有时会出现仿真结果显示信号质量良好,但是实际测试时信号质量很差,不满足信号测试标准,

实际上,仿真与测试是不可分的,拿IBIS模型为例,通常我们称之为“行为级模型”,此类仿真模型也是通过芯片不同工作条件下的V、I测试曲线建立的,这就存在一个问题,仿真时如果不关注选取哪种工作条件下的芯片模型,就会仿真不准,例如:Slow、Typical、Fast。

从上面的例子可以看出,“仿真模型库”对于仿真结果至关重要,必须通过实际产品项目的仿真测试实际对比、修正后的仿真模型才能算作“准确的仿真模型”。

有了好的仿真设计平台不能解决所有问题,还需要“准确的仿真模型”,另外也要考虑到实际产品项目的应用场景,仿真的某个信号网络,会受到电源噪声、其他信号串扰等因素影响,这同样会造成测试结果与仿真结果的差异。

误区三:仿真软件中的PCB走线“传输线模型”是非常准确的?

仿真软件中的PCB走线不管是微带线还是带状线,都可以通过仿真工具建立模型,这个模型基于层叠和实际走线的尺寸,通常情况下可以满足精度要求,但是如果说“非常准确”,那还有一些差距,这需要从以下几个方面分析:

(1)PCB铜皮的粗化/棕化处理加工工艺对信号质量有影响

PCB加工过程中,为了提高PCB铜皮层与介质层的结合强度,降低PCB分层风险,都会有粗化/棕化处理工艺,就是通过打磨或者腐蚀的方式使铜皮表面变得粗糙。

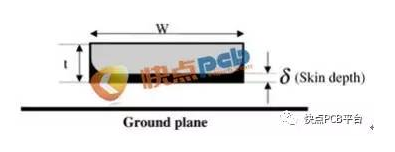

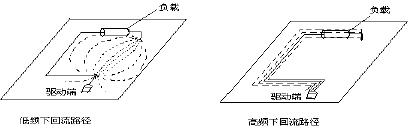

在高速信号在导体中的传输,存在“趋肤效应”,是指高频信号传输时,在导体中流动的电流将朝外围或者导体的“表皮”迁移。

PCB铜皮表面粗糙,一方面影响损耗、另一方面也会影响信号传输延时,这一点很好理解,就像汽车在崎岖不堪的山路行驶时一定会比在柏油马路上行驶更耗时。

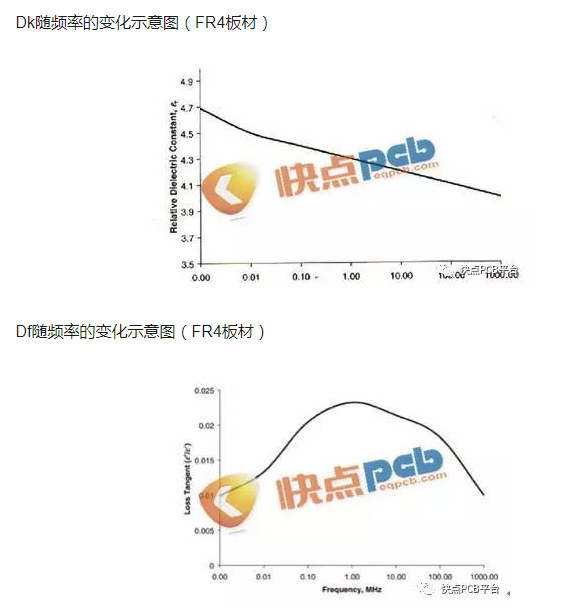

(2)PCB介质的介电常数Dk、正切损耗角Df是随着频率变化的

仿真工具中的PCB介质的Dk、Df通常为常数,但是从信号实际传输的角度,Dk/Df是随着频率变化的。

Dk/Df会随着传输信号的速率变化,那么如果仿真工具中把这两个参数作为常量处理,就会对传输线模型的仿真精度造成影响,信号传输速率越高这种影响就会越大。

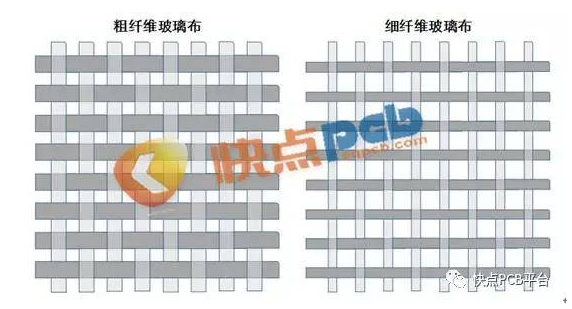

(3)PCB板材的“各向异性”影响

PCB板材通常是“环氧树脂+玻璃布”的编织结构,玻璃布的排列方向分为“经向”、“纬向”,同时根据玻璃纤维的粗细及间距,分成不同型号的PCB板材,如:1080、2116等。当PCB板材采用不同类型玻璃布时,玻璃布与树脂在板材中的成分比例是不同的。

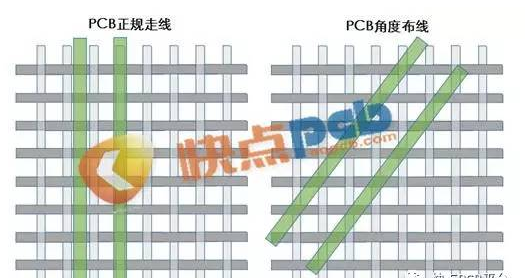

玻璃布与树脂材料的Dk/Df值相差比较大,当PCB正常走线与玻璃布的相对位置出现差异时,就会导致参考介质的Dk/Df值不同、信号的阻抗及损耗情况也会不同,如下图所示,这也是为什么有些项目要求整板PCB走线方向要采用10°的原因。

误区四:一种仿真软件平台可以搞定所有信号仿真问题

目前还没有一个统一的仿真软件平台可以适用于所有信号仿真场景。行为级信号质量仿真用Cadence SPB SigXplorer,晶体管级仿真用Synopsys HSPIe,三维电磁场建模用Ansoft HFSS,时域频域混合仿真用Ansoft ADS。目前还没有哪一款软件可以一统江湖.

-

PCB设计

+关注

关注

392文章

4566浏览量

83126 -

高速PCB

+关注

关注

4文章

83浏览量

24965 -

华强PCB

+关注

关注

8文章

1831浏览量

27455

发布评论请先 登录

相关推荐

高速PCB设计经验与体会

基于Cadence的高速PCB设计

Cadence高速PCB设计

高速PCB设计误区与对策

高速PCB设计中高速信号与高速PCB设计须知

高速PCB设计中高速信号与高速PCB设计须知

评论