第1步:规范

这些是我们要执行的 Cache Controller 的主要规范设计:

直接映射。

单银行阻止缓存。

“写入”匹配的直通策略。

在写未命中时不写分配或在周围写策略。

无写缓冲区或其他优化。

标记数组已合并。

此外,我们将设计一个缓存和一个主存储系统

高速缓存的默认(可配置)规格:

256字节单存储高速缓存。

16个缓存行,每个缓存行(块)= 16字节。

主内存的规格:

同步读/写内存。

多存储区交错存储-四个存储区。

每个存储区大小= 1 kB。因此,总大小= 4 kB。

具有10位地址总线的字(4字节)可寻址存储器。

更高的读取带宽。在一个时钟周期内读取数据宽度= 16字节。

写入数据宽度= 4字节。

注意:如果您正在寻找4路关联高速缓存控制器设计,请检查我的较新版本

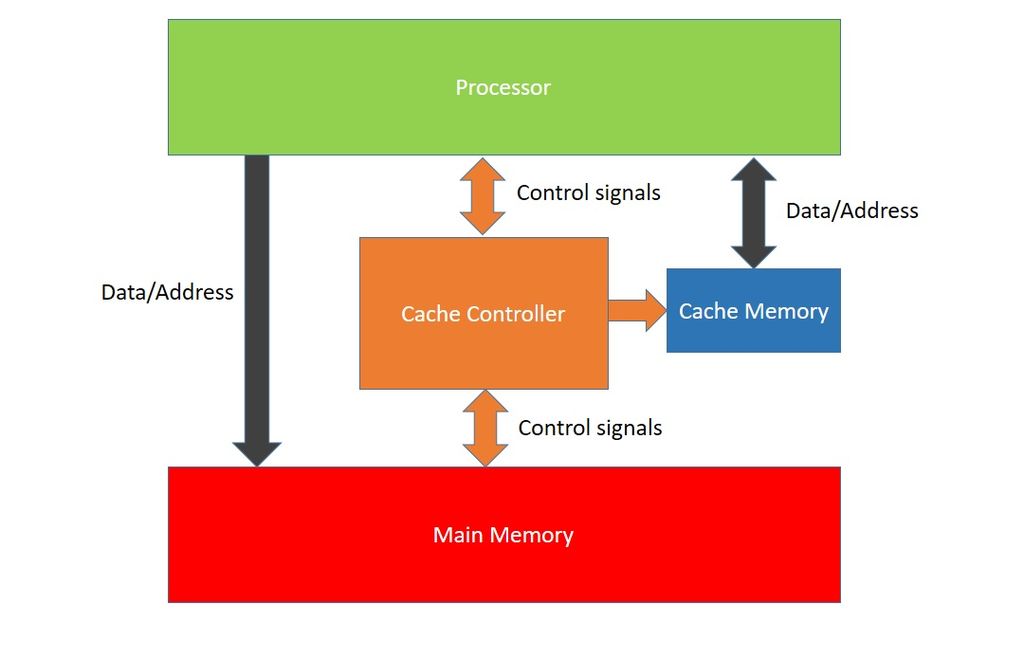

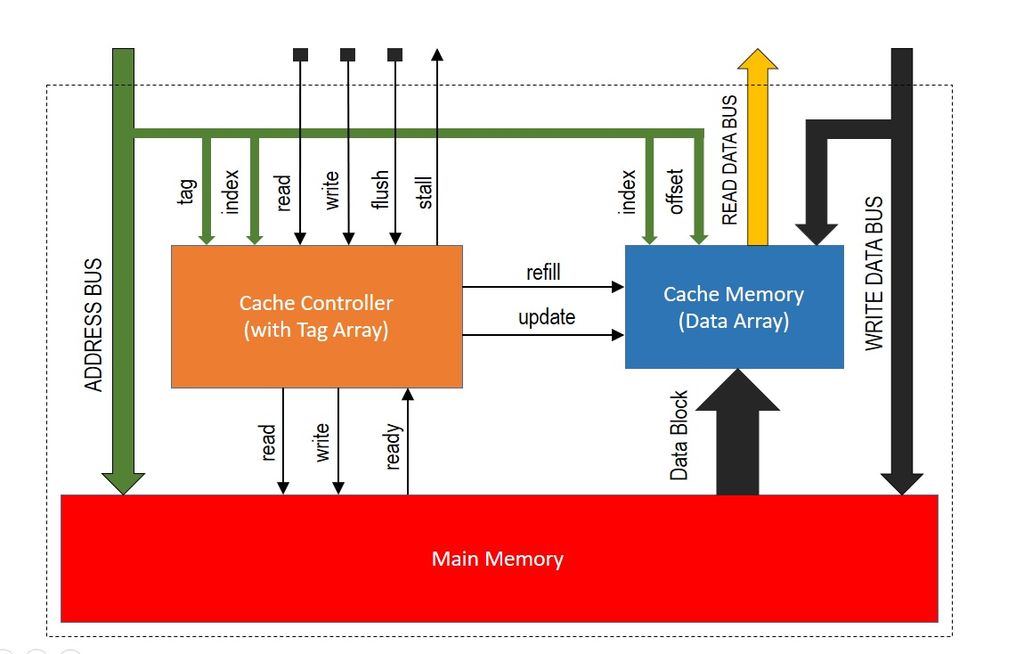

步骤2:整个系统的RTL视图

顶部模块的完整RTL表示形式如图所示(不包括处理器)。总线的默认规格为:

所有数据总线均为32位总线。

地址总线= 32位总线(但是内存在这里只能寻址10位)。

数据块= 128位(用于读取的宽带宽总线)。

所有组件均由同一时钟驱动。

步骤3:测试环境

顶部模块是使用测试台进行测试,该测试台仅对非流水线处理器进行建模(因为设计整个处理器绝非易事!)。测试台经常向存储器生成读/写数据请求。这模拟了处理器执行的所有程序中常见的典型“加载”和“存储”指令。测试结果成功验证了缓存控制器的功能。以下是观察到的测试统计信息:

所有读/写未命中和命中信号均正确生成。

所有读取/写入数据操作均成功。

未检测到数据不一致/不一致问题。

该设计已成功通过时序验证了Maxm。 Xilinx Virtex-4 ML-403板(整个系统)的工作时钟频率= 110 MHz,仅高速缓存控制器为195 MHz。

为主存储器推断出Block RAM。其他所有数组都在LUT上实现。

步骤4:附加文件

以下博客随此文件附在此处:

.VHD文件。

测试平台。

有关Cache Controller的文档。

注意:

通读该文档以全面了解此处介绍的缓存控制器的规格。

代码中的任何更改都依赖于其他模块。因此,应明智地进行更改。注意我给的所有评论和标题。

如果出于某种原因,无法为主内存推断出Block RAM,请减小内存的大小,然后更改文件中的地址总线宽度,依此类推。这样就可以在LUT或分布式RAM上实现相同的内存。这样可以节省路由时间和资源。或者,转到特定的FPGA文档,找到与Block RAM兼容的代码,并相应地编辑代码,并使用相同的地址总线宽度规范。

责任编辑:wv

-

控制器

+关注

关注

112文章

15145浏览量

170929

发布评论请先 登录

相关推荐

一种大电流无传感器BLDC电机控制器电路

ARM L220 2级缓存控制器(AC131)勘误表

如何使用DSP库中的PID控制器功能

基于STM32WL系列微控制器构建特定LoRa应用程序

Avago 12Gb/s SAS MegaRAID控制器的RAID缓存优势

一种简易缓存控制器的设计

一种简易缓存控制器的设计

评论