摘要:电子系统功能与复杂度的日益增加,对系统验证测试的效率提出了更高要求。传统卫星测试平台依据特定型号任务进行定制式设计,其设计开发周期长、综合成本高,难以适应当前任务需求。为此,提出了一种基于System Verilog语言开发的星载固态存储控制器通用仿真测试平台架构,其内部采用层次化模型,信号接口统一采用APB总线标准,可以通过配置测试平台数据源及格式及来适配不同容量、不同速率以及不同构型的星载固态存储控制器。实验表明,本文设计的测试平台具有一定的通用性,相比于传统测试平台可以有效地节省测试时间并提高测试覆盖率。

0 引言

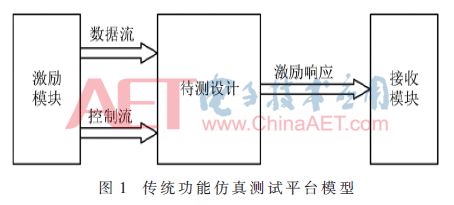

星载固态存储控制器是卫星的数据处理中心,负责卫星工程参数和有效载荷科学数据的接收、存储与传输。星载固态存储控制器使用现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)作为处理核心。FPGA是一种可编程的信息处理器件,可通过改变其配置信息实现不同功能,具有高集成度、高速、高可靠性等特点,在航天领域内得到了广泛应用。但是当FPGA中的程序存在隐性缺陷时,如因外部异常输入导致的内部功能模块状态机运行异常时,会导致FPGA输出错误信号,进而导致整个系统功能紊乱。因此需要对FPGA设计进行功能测试和时序测试。此外,由于航天任务对可靠性和安全性的特殊要求,还需要对其进行余量测试、安全性测试、恢复性测试以及边界测试等[1]。 图1所示为传统功能仿真测试平台模型。传统功能仿真测试平台由激励模块、待测设计和接收模块三部分组成。其特点是结构简单、功能单一,没有统一的架构和标准,且大都是基于特定的型号任务所开发的。这种“定制式”的测试平台存在很多弊端,如通用性和可移植性差、可读性差、不利于管理等。为解决上述问题,提出了一种基于System Verilog语言编写的星载固态存储控制器通用仿真测试平台架构,其内部设计采用层次化模型,内部接口与总线均采用由ARM公司提出的高级外设总线标准(Advanced Peripheral Bus,APB)。

1 标准化通用测试平台设计

1.1 测试平台概述

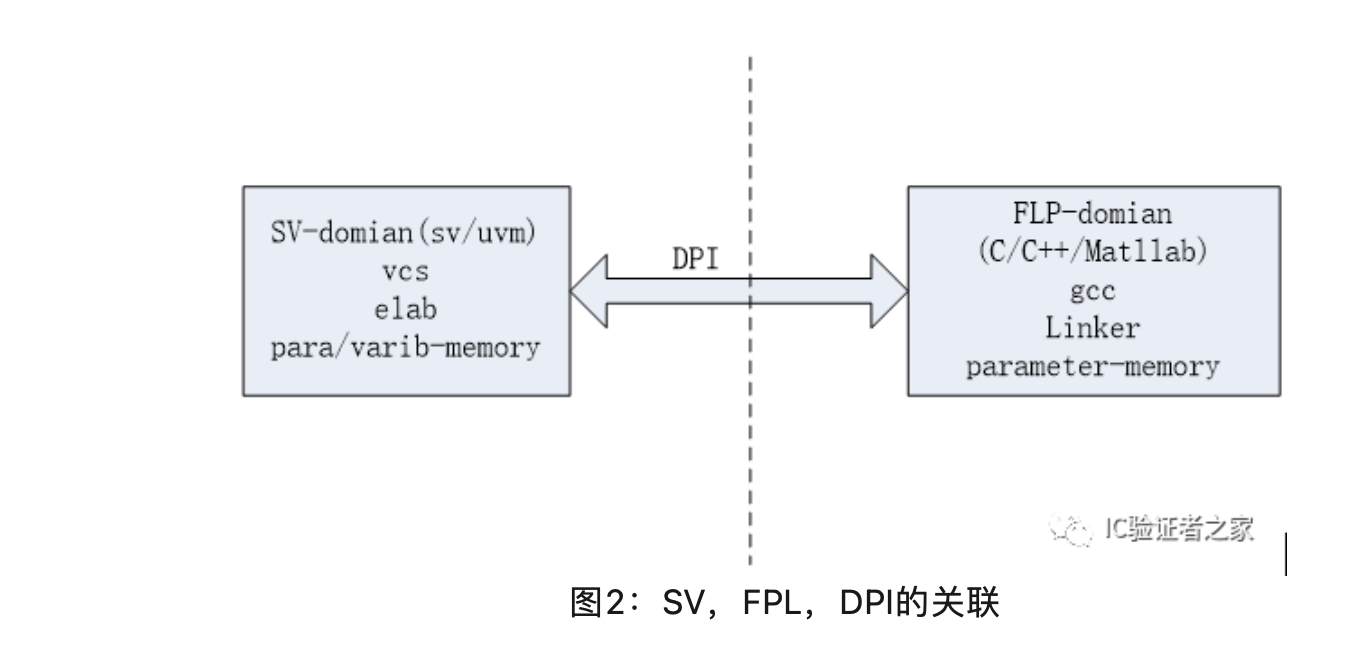

基于Verilog HDL和VHDL语言开发的测试平台存在重复利用率差、开发效率低等问题,而采用面向对象的专用验证语言System Verilog可以有效地解决这些问题。System Verilog充分吸收和借鉴了Verilog HDL、VHDL、System C和C++等语言的特性,使其可以在更高的抽象层级上对高度复杂的设计进行测试验证[2]。此外,测试平台架构应采用模块化和标准化设计,从而使测试平台具有更好的通用性,还应采用层次化结构设计,以有效增强测试平台的灵活性和稳定性。明确的层次设计可以有效地定义各层之间的接口,层与层之间的独立性也使得每一层可以采用其最合适的技术去实现而不影响其他层。

1.2 层次化结构设计

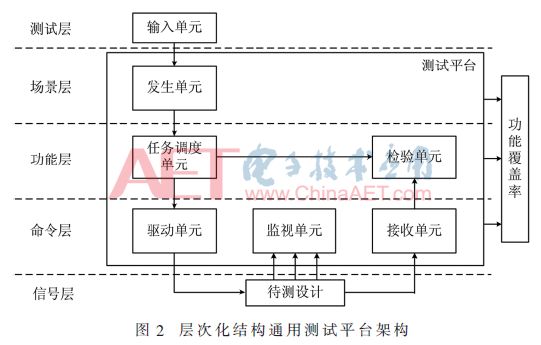

星载固态存储控制器设计的标准化通用仿真测试平台包含5个层次:测试层、场景层、功能层、命令层和信号层,层次化结构通用测试平台架构见图2。

最底层为信号层,负责将待测设计连接到测试平台,完成模块信号对接。信号层上层是命令层,驱动单元接收来自功能层的命令信息后将总线上的命令驱动到待测设计的输入上;接收单元负责收集待测设计的激励响应输出,并且按照命令进行分组;监视单元负责监视那些不受命令信号约束的独立信号,其可穿越整个命令的周期来搜寻这些信号的变化[3]。另外,如果当程序中 “不应发生”的事情的确发生的时候,监视单元将进行报警。因此,监视单元和接收单元的共同作用可以更加全面地监控测试过程中的状态变化,从而提高测试结果的可靠性。 功能层向下面对命令层。任务调度单元接收来自场景层的任务后,将任务分解成若干独立的命令。这些命令在被送往驱动单元的同时也会被送往检验单元。检验单元负责对比实际待测设计的激励响应与预测单元理想的响应结果。通过对检验单元中数据进行分析就可以判断当前任务下待测设计是否符合预期设计要求。 场景层根据来自测试层的激励约束,模拟实际任务中的各种场景。发生单元的组成部分根据不同的待测设计进行不同适应性更改,但基本模块均由信号源和数据源组成。信号源根据上层的约束信息产生相应激励信号,并控制数据源开始向待测设计发送数据。 测试层为整个测试平台的顶层,其中输入单元用来向测试平台发送创建激励的约束。功能覆盖率可以衡量所有测试在测试计划中的进展。

2 星载固态存储控制器通用测试平台实现

2.1 测试平台架构设计

基于层次化结构通用测试平台架构,结合工程型号任务需求,搭建星载固态存储控制器通用仿真测试平台,见图3。

通用测试平台中各模块接口均使用APB总线标准进行封装,并增加APB总线接口模块进行平台内各模块及测试平台与待测设计间通信。此外,增加参数配置模块,其可对发生单元中的数据源和激励源以及驱动单元中的时钟和复位模块进行配置。测试平台内嵌有参数可配置的Flash模型、SDRAM模型以及MRAM模型。通过参数配置模块可以对Flash模块等进行配置。其中,Flash模型设计采用分层结构,最底层由8 Gbit的基本单元组成,支持主存储区和空余区的读写,支持读、写和擦除等时间参数设置和初始坏块设置,以该基本单元为基础进行级联扩展,可实现不同存储容量、存储速率以及叠装构型的Flash器件的阵列模拟。 测试平台的各项参数配置需在测试开始前完成,即测试前向参数配置模块输入配置参数,完成对Flash阵列模型及其他模块的配置。对待测设计进行测试时,由测试输入模块向测试平台注入约束条件,发生单元根据收到的约束条件产生相应的激励源,激励信号经任务调度单元分别加载到检验单元和待测设计。同时数据源根据约束条件开始向任务调度单元发送数据。任务调度单元接收到待测任务信息后将待测任务信息下发到驱动单元。驱动单元生成驱动配置文件,调配各个模块向待测设计输入数据及相应的时钟复位信号。待测设计在接收到激励输入和数据后产生激励响应,接收单元对激励响应进行分类,随后将其送入到检验单元中的比较器。检验单元收到的激励输入被加载到参考模型中产生理想激励,随后比较器将理想激励与实际激励响应进行比较。通过对检验单元输出结果的分析就可以判断在当前约束条件下待测设计是否符合预期设计目标。功能覆盖率模块收集整个测试过程中的信息作为评价测试的充分性证据。

2.2 工程组织架构

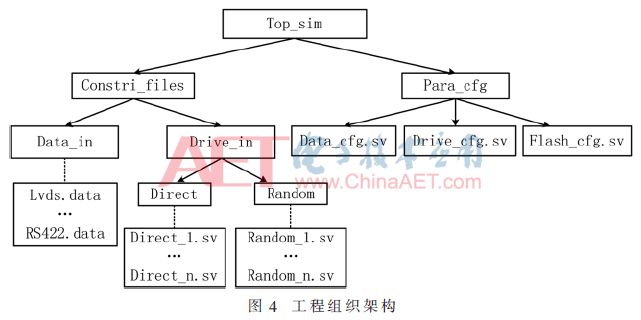

通用仿真测试平台运行在仿真工具QuestaSim10.4c上,使用System Verilog语言开发。测试平台采用层次化组织架构,工程组织架构见图4。

测试工程组织架构为树状结构,顶层文件名为“Top_sim”,其中包含两个主要的一级结构:约束文件(Constri_files)和参数配置文件(Para_cfg)。约束文件包含数据输入约束(Data_in)和激励输入约束(Drive_in)两个二级结构。激励输入约束下分为直接测试(Direct)和随机测试(Random)两个三级结构[4]。直接测试可以保证测试验证过程有一定的复现性,而随机测试可以对待测设计进行更为充分的验证。参数配置文件(Para_cfg)用于对测试平台中相关模块进行配置以满足待测设计的要求。测试平台的执行脚本文件是采用TCL语言编写的扩展名为.do的文件,用于在测试时对工程文件进行自动组织与控制。

3 实验与应用

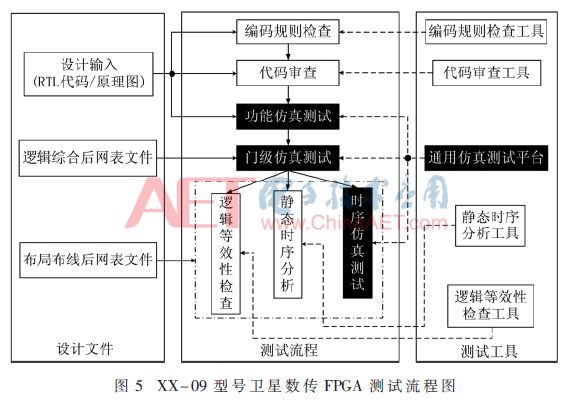

基于上述设计所开发的通用仿真测试平台已成功应用于XX-09型号卫星和XX-5A型号卫星数传FPGA的仿真测试。根据开发方提供的源程序以及《XX型号卫星数传FPGA需求规格说明》开展测试,测试流程图见图5。

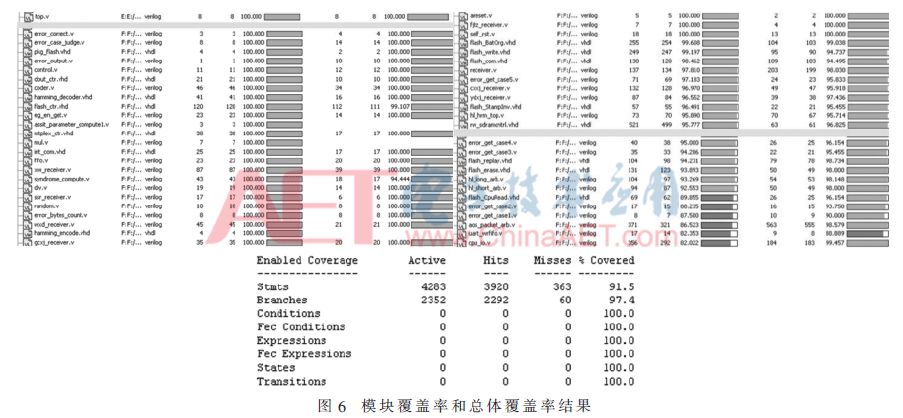

首先运用代码检查工具对RTL级代码进行编码规则检查和代码审查,随后使用测试平台分别对待测设计进行功能仿真测试、对逻辑综合后网表文件开展门级仿真测试以及对布局布线后网表文件开展时序仿真测试。最后,使用静态时序分析工具和逻辑等效性检查工具对待测设计进行静态时序分析和逻辑等效性检查[5]。其中,功能仿真测试和门级仿真测试均在本文的通用仿真测试平台上完成。 以XX-09型号卫星为例,存储单元为两个64 Gbit NAND Flash叠装芯片并联构成的128 Gbit NAND Flash存储阵列,每个64 Gbit NAND Flash由8片8 Gbit的存储基片组成[6]。根据XX-09型号卫星任务数传FPGA任务书与需求规格说明,对数传FPGA开展功能需求分析及接口需求分析,共整理出82个功能相关测试子项,设计了415个测试用例,覆盖了功能测试、性能测试、时序测试、接口测试、安全性测试、余量测试、恢复性测试、边界测试、等效性检查共9种测试类型。仿真测试模块覆盖率和总体覆盖率结果见图6。功能仿真中对语句覆盖率和分支覆盖率进行分析,语句覆盖率达到91.5%,分支覆盖率达到97.4%,未覆盖原因为case条件语句中default分支不可达,经确认测试后功能正常。

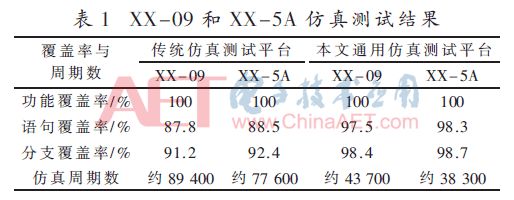

对XX-5A和XX-09型号卫星数传FPGA分别采用传统仿真测试平台与本文仿真测试平台进行仿真测试,统计覆盖率与仿真周期数,结果见表1。

由表1知,传统仿真测试平台与通用仿真测试平台均可完成100%功能覆盖率,但通用仿真测试平台的仿真周期数是传统仿真测试平台的48%左右,而且具有更好的语句覆盖率和分支覆盖率。综上,本文所设计的仿真测试平台覆盖率性能良好并具有一定的通用性,相较于传统仿真测试平台可以有效缩短测试时间,并可以有效提高测试覆盖率。

4 结论

为解决传统测试平台通用性和继承性差、难升级、难维护等问题[7],提出了一种基于层次化结构设计的仿真测试平台架构,并在此基础上结合APB总线标准开发了星载固态存储控制器的通用仿真测试平台。利用该平台对两个卫星型号任务的数传FPGA进行了仿真验证测试,结果表明测试平台可以有效支持对不同型号星载固态存储控制器的仿真测试,相比于传统测试平台优化了测试流程并提高测试效率,具有很好的工程应用价值。

参考文献

[1] 周珊,杨雅雯,王金波.航天高可靠FPGA测试技术研究[J].计算机技术与发展,2017,27(3):1-5,11.

[2] 高虎,封二强,赵刚.基于Testbench的FPGA实物自动化测试环境设计[J].电子技术应用,2018,44(4):48-51.

[3] FIERGOLSKI A.Simulation environment based on the universal verification methodology[J].Journal of Instrumentation,2017,12(1):C01001.

[4] 杨志勇,董振兴,朱岩,等.星载高速大容量存储器文件化坏块管理设计[J].电子技术应用,2017,43(6):11-14.

[5] BIRLA S,SHARMA S,SHUKLA N K.UVM-powered hardware/software co-verification[J].Journal of Information and Optimization Sciences,2017,38(6):945-952.

[6] 林天静,阮翔,刘春.基于Flash控制器的FPGA在线加载功能设计[J].电子技术应用,2019,45(1):88-91.

[7] 陈琳娜,孟建熠,林志涛.面向串行总线的层次化UVM验证平台设计[J].传感器与微系统,2018,37(9):84-86,89.

-

控制器

+关注

关注

112文章

15154浏览量

170946 -

固态存储

+关注

关注

1文章

42浏览量

12798 -

C++

+关注

关注

21文章

2066浏览量

72880

原文标题:【学术论文】星载固态存储控制器标准化通用仿真测试平台设计

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【分享】基于Easygo仿真平台的三电机实时仿真测试应用

UVVM(通用 VHDL 验证方法)

PrimeCell AHB SDR和SRAM/NOR存储器控制器(PL243)技术参考手册

PrimeCell静态存储器控制器(PL092)技术参考手册

AMBA DDR、LPDDR和SDR动态内存控制器DMC-40技术参考手册

PrimeCell AHB SRAM/NOR存储器控制器(PL241)技术参考手册

PrimeCell AHB SDR和NAND存储器控制器(PL242)技术参考手册

新能源汽车核心技术:VCU整车控制器、MCU电机控制器、BMS电池管理系统

一种基于System Verilog语言开发的星载固态存储控制器通用仿真测试平台架构

一种基于System Verilog语言开发的星载固态存储控制器通用仿真测试平台架构

评论