多层板的接地层可以显着提高电路的噪声性能。对于双面板,我们通常不能有地平面,我们希望有更多的噪音和排放。由于这个限制,我们更喜欢多层板,除非成本目标迫使我们使用双层板。

即使我们没有带有双层板的地平面,仍然是可用于改善电路性能的技术。本文介绍了接地网格技术,它允许我们为双面电路板实现高效的接地电路。

地平面如何降低电路板噪声?为了更好地理解“地网”技术的运行,它将帮助您首先了解PCB中地平面的功能。请查看我的文章,了解地面如何在需要之前减少电路板噪声。

什么是网格化地平面?

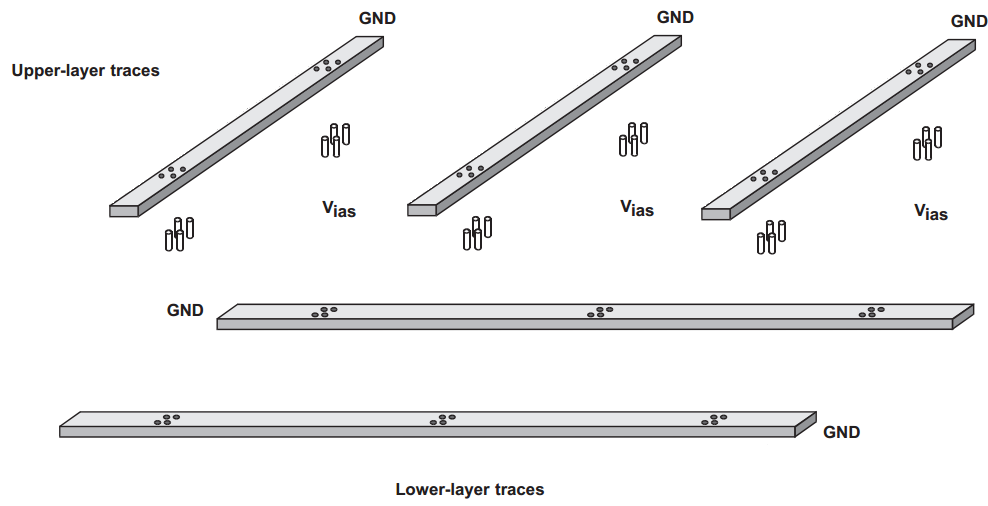

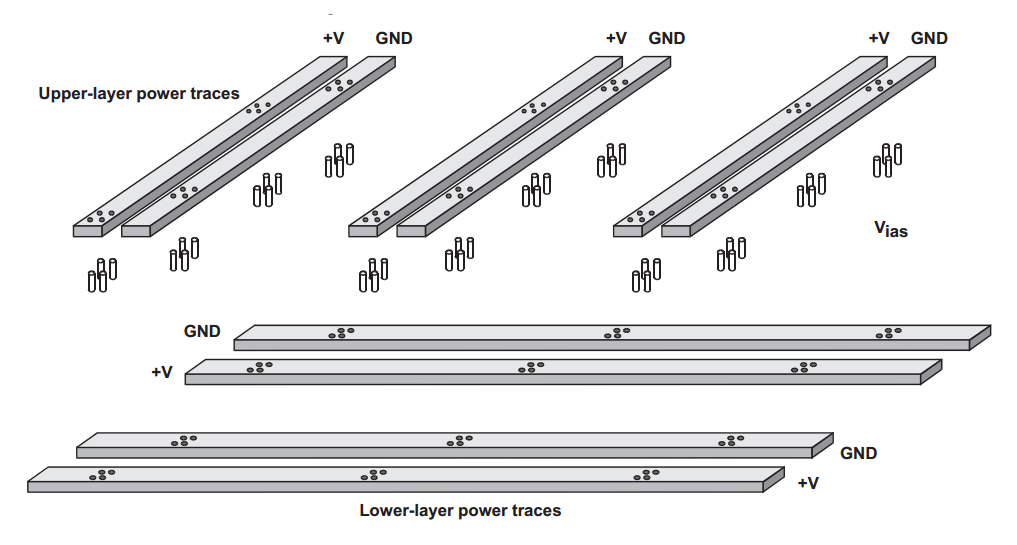

地面网格由PCB上的接地网络创建。例如,如图1所示,我们可以在电路板底层有一些水平接地走线,顶层有一些垂直接地走线。此外,在垂直和水平地面轨迹的交叉点处有过孔。

图1。图片由TI提供。

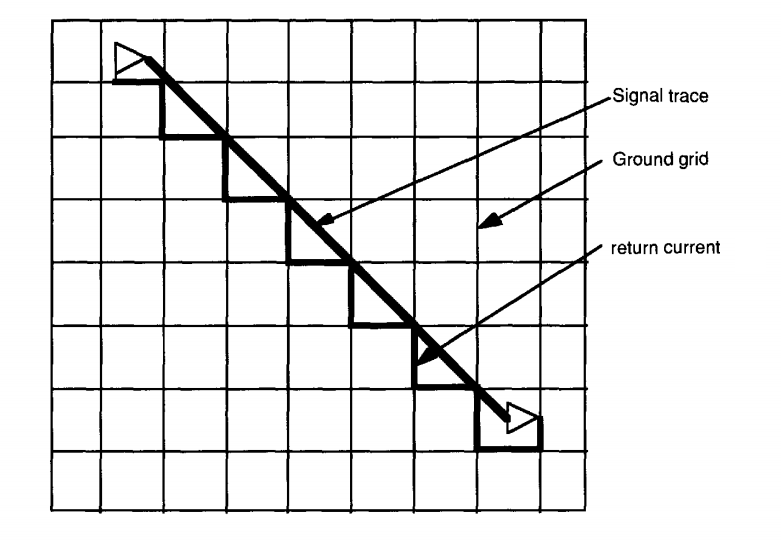

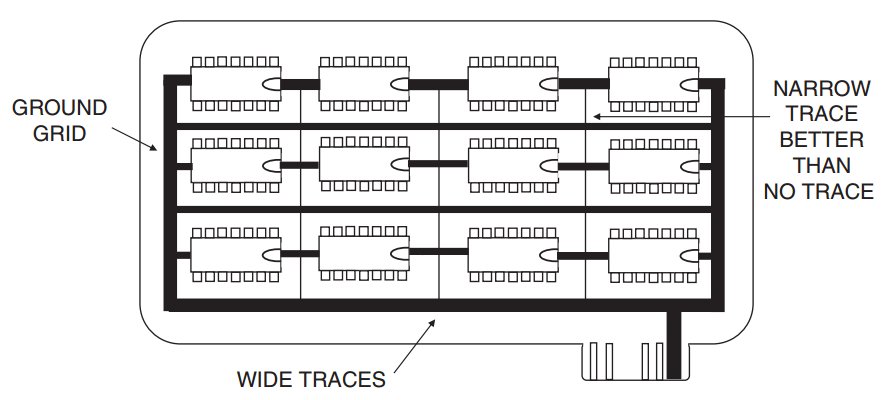

上述技术如何创建低电感地系统?图1中的网格相当粗糙。图2中显示了更精细的接地网格(不区分底部和顶部接地迹线)。信号走线将左上角的栅极输出连接到右下角的栅极输入。

图2。图片由EMC和印刷电路板提供。

如您所见,可以通过地面网格提供的许多替代返回路径关闭当前循环。虽然有许多并联的返回路径,但大部分电流将流过最靠近信号走线的路径,以最小化路径电感。图中显示了可能具有相对较小电感的可能返回路径。

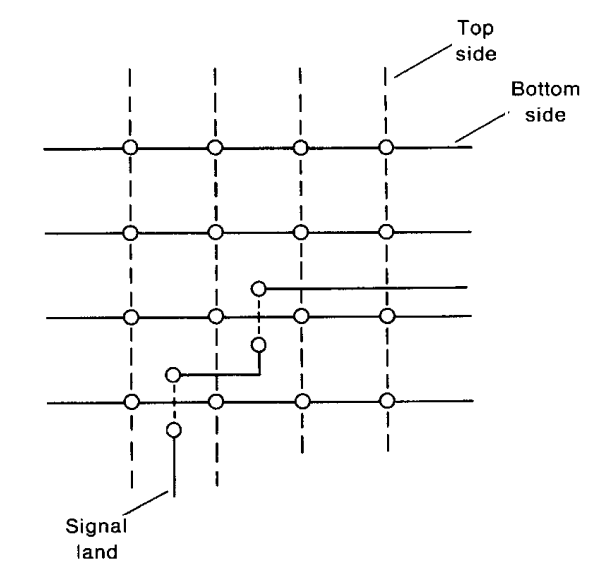

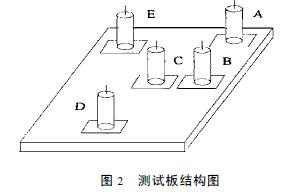

请注意,对于接地网格,您可能必须使用多个过孔来在PCB上布线信号走线。如图3所示(图2的概念图中没有显示)。

图3。图片由电磁兼容性介绍提供。

因此,它更好使大多数顶层迹线垂直运行,大部分底层迹线水平延伸,以便需要更少的过孔。

它的效率如何?

检查地面系统有效性的一种方法是测量电路板上各种IC之间的接地噪声电压。一项研究比较了使用接地网格的双层电路板的IC的接地引脚与采用单点接地的类似设计的接地引脚之间的电压差。该研究表明,接地网可以将IC的接地引脚之间的电压差从1000 mV降低到100 mV(这是各种IC组合之间的最佳改进)。根据这项研究,当应用地面网格技术时,电路板辐射减少了约7 dB。有关此研究的更多详细信息,请参阅Henry W. Ott的电磁兼容性工程的第10.5.3节。

为了显着降低接地电路电感,应使用0.5英寸或更小的接地网格间距。通常,随着工作频率的增加,我们可能需要使用更精细的网格来提供更多的并行路径并降低接地系统电感。接地网格技术与工作频率高达10 MHz的电路兼容;在这个频率之上应该使用地平面。

地面网格技术的其他版本

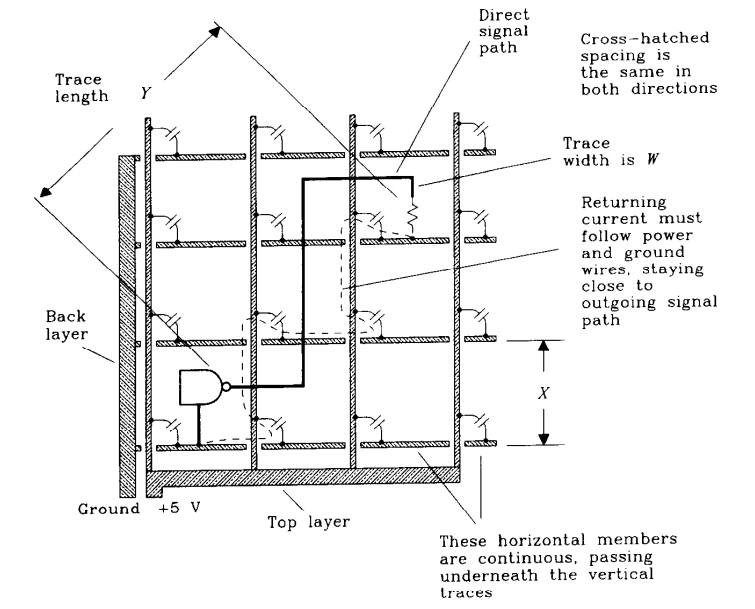

不同的书籍和应用笔记都提出了略有不同的版本地网技术。虽然图1的地面网格仅出现在地面轨迹上,但霍华德·约翰逊和马丁·格雷厄姆所着的“高速数字设计:黑魔法手册”一书建议如图4所示。

图4。图片由霍华德提供来自高速数字设计的Johnson和Martin Graham:黑魔法手册。

在这种情况下,顶层的垂直接地线被电源线替换。水平构件连接到地面。请注意,这些接地走线位于电路板的底部并且是连续的;它们不会被顶层的电源线断开。图4的接地网格将起作用,因为交流回流电流可以沿着接地走线或电源走线同样良好地流回其源极。由于过孔不能用于此方案,我们必须在垂直和水平走线的交叉点使用旁路电容。这些电容应具有高质量,以使电流容易流回其驱动栅极。

我们还可以在顶层和底层上都有接地和电源走线。如图5所示。

图5. 图片由TI提供。

这将占用更多的电路板空间,但我们预计它会表现出更低的电感,因为现在返回电流可以流过接地走线和电源走线。流过电源走线的返回电流部分将使用旁路电容到达附近的接地走线,通过它可以流回驱动门。

如果电路板空间有限,则不允许使用宽迹线,您可以使用窄迹线实现网格。如图6所示。

图6。图片由电磁兼容工程提供。

宽走线可以提供更低的电阻,这对于低频考虑非常重要;然而,即使是窄的迹线也可以为电网系统增加许多并行路径并降低接地电感(高频率)。

结论

接地路径电感可通过几种不同的机制增加电路板噪声。多层板允许我们拥有可以显着降低接地电感的坚固接地层。然而,对于双面板,我们必须采用其他技术,例如接地网,来实现低电感接地系统。一项研究表明,地面电网可以将发射减少约7 dB,地电压差异减少一个数量级。

-

pcb

+关注

关注

4220文章

22468浏览量

385667 -

电路板

+关注

关注

140文章

4614浏览量

92399

发布评论请先 登录

相关推荐

地面如何在需要之前减少电路板噪声

地面如何在需要之前减少电路板噪声

评论