了解异构和同构总线,特殊IC封装等等!

本文是关于创建逻辑示意图的特殊主题的集合。这些主题是我多年来一直在脑子里传播的主题。我希望你发现它们很有用。

本文假设了构建原理图符号和创建基本原理图的经验。

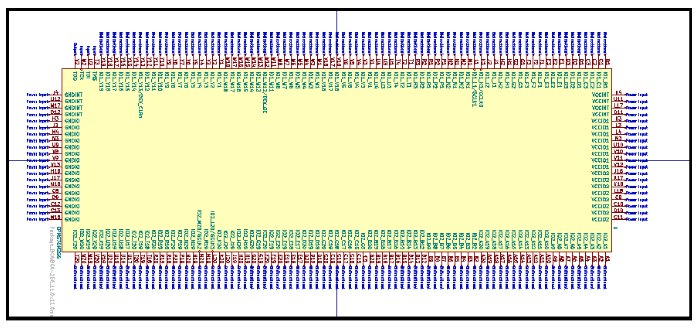

高引脚数部件

这是我通过快速搜索KiCAD库找到的最高引脚数符号。对我来说,这太密集,完全不切实际。应该有一个反对这种事情的规则!我回过头来看了一堆原理图,发现我的阈值大约是100针。超过100个引脚,我总是为每个部分创建多个单元。

我分手了通过将引脚分成功能组来实现高引脚数部分。例如,FPGA将为所有电源和接地引脚提供一个单元。另一个单元将具有与配置零件相关的所有引脚。然后,I/O引脚有多个单元。

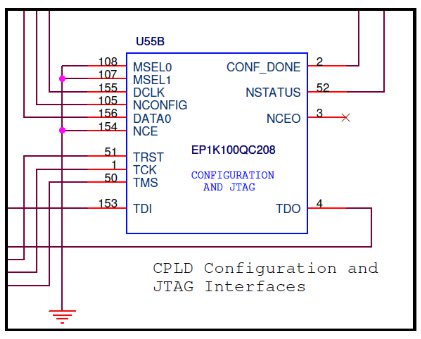

这是FPGA配置引脚的单元。

此符号可放置在原理图中任何有意义的位置。在这种情况下,配置存储器IC和JTAG连接器用于编程和调试。在表格上还有几个需要回家的杂项。

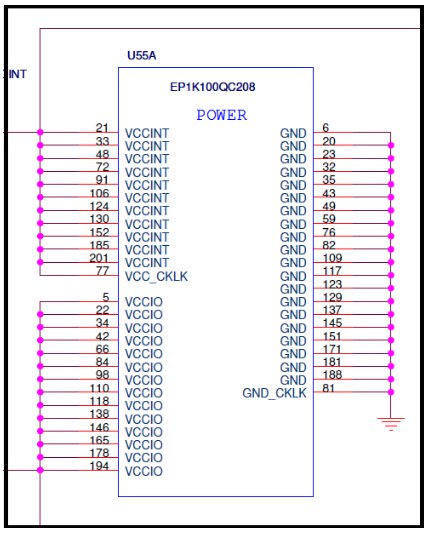

这是带电源和接地引脚的单元。

电源引脚结构不多。两种类型的电源引脚分为两组:一组内部电源和另一组I/O电源。其他设备具有更复杂的功率结构,并且需要更多组。该装置位于带有稳压器和电源监控电路的板上。

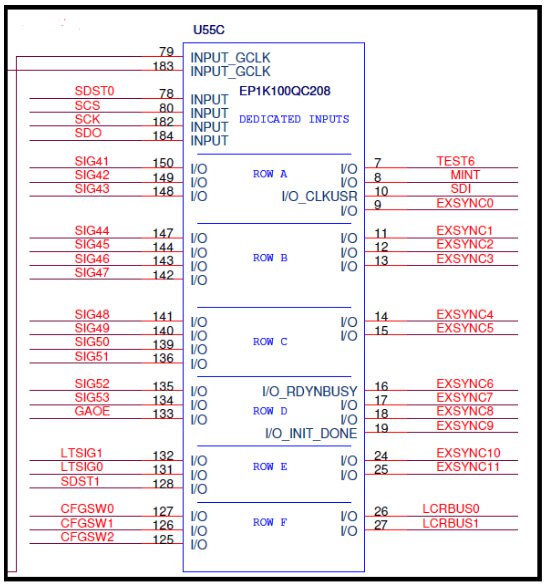

I/O引脚分为四个单元。这是一个显示大约25%的I/O的单位。

Altera(现在英特尔)部件通常具有内部互连,具有突出的行和列结构。在此部分中,连接到行互连的I/O的I/O速度更快,而连接到列的I/O的速度更慢。由于这是一个高速设计,我需要考虑哪些信号连接到行或列,我创建了一个符号,帮助我进行引脚分配。你可以看到这个单元都是“行”引脚。另外,行进一步分组在一起(行A,B,C等)。此布置指示器件内部的其他时序特性。

考虑将可编程器件中的I/O分组以反映特定设计中器件的功能。如果有助于设计和理解电路,自定义符号的额外工作是可以的。

层次结构

一般来说,原理图大于一张纸可以用两种方式组织,平面或使用层次结构。平面原理图直接使用片材之间的连接。信号通常偏离一张纸的侧面并出现在另一张纸的侧面。层次结构使用工作表中的“分层块”来表示另一个工作表。通过连接到块来完成与工作表的连接。工作表上可以有多个分层块。块和表的组织看起来很像计算机中的文件目录。通常有一个“根表”,它很像根目录。

层次结构用于两个主要目的。首先,它提供了原理图中的逻辑结构以及以与信号连接一致的方式在工作表之间导航的方式。其次,它允许在工作表上绘制一次电路,但通过使用引用同一工作表的多个分层块重复多次。

使用层次结构是组织设计的有效方式。对这种结构感到满意需要一些工作。然而,对我来说,它已成为必不可少的。我使用它太多了,我从来没有在平面设计中使用直接的片对板连接。工作表始终通过分层块连接。微妙的效果是原理图采用三维框图的外观。我喜欢这样记录设计的方式,并且可以快速方便地找到它。

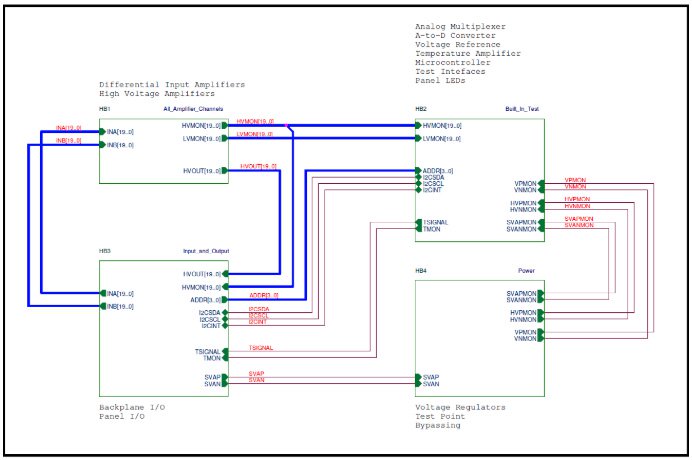

这是20通道高压放大器板的根表。当然,不可能看到细节。但是,也许你可以看到分层块看起来像一个方框图。

我提供了注释,列出每个块中的电路。单击一个块可以轻松找到某些内容。不是在这里,但在其他设计中,我在根表上包含了没有电路连接的块,但引用了带有注释和图表的表。使用这样的块就像带有链接的目录一样。

我注意到中间的I2C总线有三个信号:I2CSDA,I2CSCL和I2CINT。我希望我能够使用“异构总线”,这是下一个主题!我可以将三行压缩成一行!

同构和异构总线

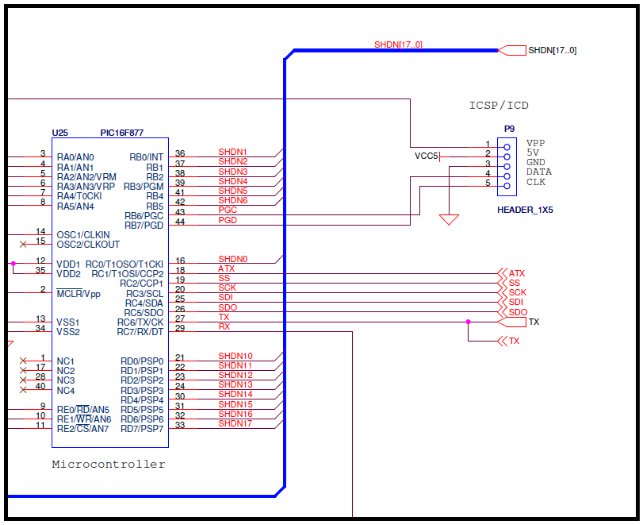

我所知道的所有原理图程序都支持将多个同样命名的网络收集到一个“总线”。该术语最初来自数据总线或地址总线中的信号捆绑。在下面的示意图中,此功能将信号捆绑为名称“SHDN”,后跟序列号。这被称为“同类”总线。

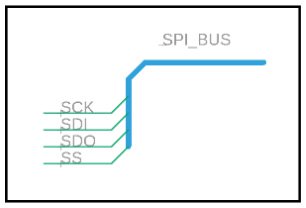

原理图中间是一个带有四个信号的SPI接口:SS,SCK,SDI和SDO。它们是一个功能组,将它们组合起来并为所有这些组合使用一行和一个名称会很方便。一些原理图程序允许将信号分组为“异构”总线。这种类型的总线似乎没有标准名称。 Altium称之为“信号线束”。 OrCAD使用术语“NetGroup”。在Eagle中,所有公交车都是异构的。 KiCad正在开发此功能并将其称为“组总线”。

这是在Eagle中为原理图中的四个网络创建的异构总线。

在我看来,异构总线为原理图提供了逻辑结构,减少了混乱。

特殊IC封装

机械设计师在解决与更小和更小外形尺寸以及热管理相关的封装问题方面变得非常聪明。但是,他们的一些设计导致应该在原理图上显示的连接。我尝试在原理图中包含连接到网络的任何包元素。例如,用于连接器外壳的镀通安装孔或连接到GND或电源的部件上的散热片应在示意图中。以下是两个具有连接电源或GND功能的封装示例。

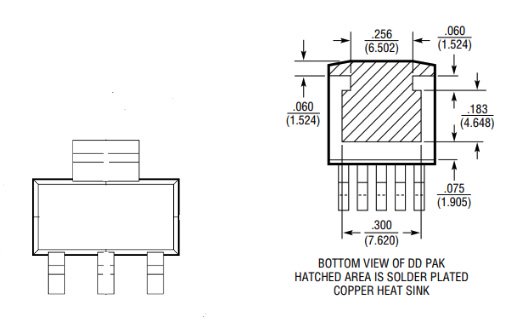

部分在左侧有一个金属片,通常焊接到电路板顶部的铜区域以散热。右边的部分底部有一个“裸露焊盘”,焊接在铜区域。在这两种情况下,标签或焊盘通常都在IC内部电气连接。

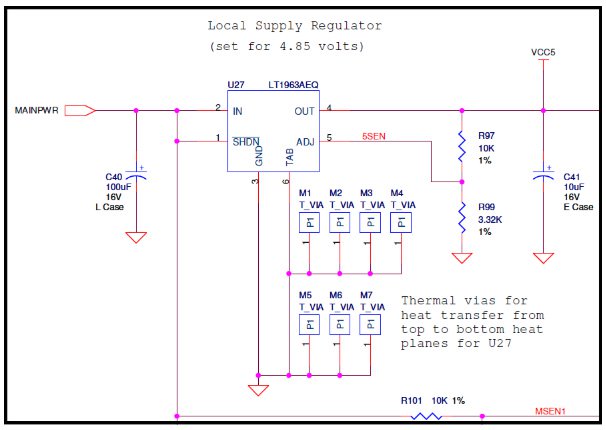

该示意图显示了如何使用右侧封装处理电压调节器的裸露焊盘。

引脚1到5是正常引脚。我添加了引脚6来表示裸露焊盘的电气连接并将其连接到GND。我还包括6个热通孔,从顶部到底部铜区域传导热量。过孔包含在原理图中,因为它们形成电气连接。结果如下:

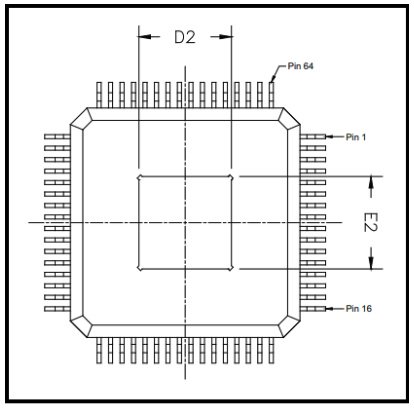

问题:64引脚部分何时不是64引脚部分?

解答:当它是“E64”封装时。

为此部件构建符号时,您会立即看到零件上没有接地引脚!英特尔论坛的一位评论者推测它是使用量子效应的尖端部分,不需要接地连接。嗯,不太好。接地是部件底部的裸露焊盘。这是底部的图纸,中间有垫子。

要处理对于这样的部分,只需在符号中添加Pin 65即可。然后,将其连接到原理图中的GND。务必在原理图上添加注释!数据表指出,焊盘仅用于电气连接,没有热功能。 PCB设计人员需要知道这一点!

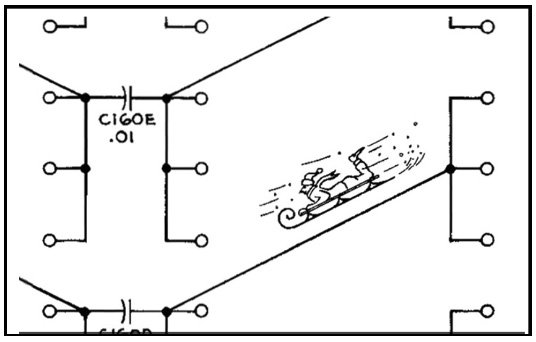

奖金主题

“回到过去”的原理图是手绘的,大多数是专业的绘图员。他们可能会不时地休息一下,在原理图上涂一些关于激发他们想象力的东西。以下是Tektronix示意图中的示例。

图像使用vintageTEK提供

你有没有在原理图中添加卡通或表情符号?

您是否曾使用非正交线作为网络?你的原理图程序是否允许它们?

-

FPGA

+关注

关注

1602文章

21309浏览量

593128 -

原理图

+关注

关注

1267文章

6180浏览量

225594 -

引脚

+关注

关注

16文章

1042浏览量

48954

发布评论请先 登录

相关推荐

逻辑示意图的创建技巧

逻辑示意图的创建技巧

评论