美国马萨诸塞州诺伍德市 - 全球领先的信号处理应用高性能半导体公司ADI公司今天推出了一系列时钟IC,可满足当今高性能电子应用中最严格的信号处理要求,如作为无线基础设施收发器,仪器仪表和宽带基础设施。在这些应用中,信号处理方案正在达到惊人的速度,并且抖动或时钟边沿的不确定性可能导致传输错误并对系统的整体性能产生不利影响。 ADI公司的新型时钟IC具有超低抖动性能(亚皮秒级),使器件能够提供极其干净的系统时钟,从而显着降低系统关键信号链的噪声。

除了低抖动之外,ADI的时钟IC还通过集成几个关键功能来提高系统性能,从而无需多个分立元件,减少电路板空间,最终降低BOM(物料清单)成本。这些功能包括低相位噪声PLL(锁相环)频率合成器内核,可编程分频器和可调延迟模块。结合亚皮秒级抖动性能,这些特性使ADI的时钟IC成为业界最佳的关键信号路径器件性能,如模数转换器(ADC),数模转换器(DAC) ,直接数字合成器(DDS)和混合信号前端(MxFE)设备。

“作为数据转换的行业领导者,ADI不断寻求为客户提供最高水平的系统性能,而ADI的时钟IC是提高系统性能的关键,”产品线总监Kevin Kattmann表示。高速转换器,Analog Devices。 “随着频率和数据速率越来越高,系统的精度和转换器的性能越来越受到时钟信号质量的限制.ADI的新系列时钟IC结合了同类最佳的信号完整性和创新功能,允许客户实现最佳系统性能,同时大大简化时钟树设计任务。“

ADI公司的时钟IC产品包括时钟分配和时钟生成器件。

ADI的时钟分配IC - AD9510,AD9511和AD9512

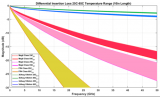

ADI公司的时钟分配IC系列包括AD9510,AD9511和AD9512。与其他解决方案相比,这些器件在宽频率范围内具有亚皮秒级性能,集成度更高,可编程性更强。

具有亚皮秒抖动的低相位噪声时钟输出

低相位噪声和低抖动是降低信号路径中总噪声的关键。 ADI的时钟分配IC具有LVPECL输出,以及用户可选的LVDS和CMOS选项:

LVPECL输出工作在800 MHz,附加抖动小于250 fs(飞秒)rms。

LVDS和CMOS输出分别工作在800 MHz和250 MHz。

在LVDS和CMOS模式下,附加抖动均小于300 fs rms。

LVPECL和LVDS时钟输出的电压电平均可编程,允许系统设计人员确定给定应用的最佳电压摆幅。 AD9510提供最大的灵活性,混合LVPECL,LVDS和CMOS逻辑,总共8个独立时钟输出。对于需要较少输出的设计,AD9511和AD9512将五个独立输出封装在更小的封装中,同时降低功耗。

可编程分频器

通过使用具有显着增强功能的分频器,ADI的时钟分配IC消除了产生门延迟和相移所需的额外元件。每个时钟分频器可编程为1到32之间的任何整数比,在处理一个PCB(印刷电路板)上的多个频率时提供灵活性。除法功能还包括用户可选择的偏移字,用于实现通道到通道的相位控制。由于器件在分频器模块内部执行相位控制,因此它们比相应的分立器件实现更低的抖动。

可编程延迟

ADI的时钟分配IC具有片上可编程延迟,允许用户调整数据转换器和数字ASIC,FPGA之间的设置和保持时间要求(现场) - 可编程门阵列)和数字上/下变频器,无需添加额外的时钟硬件。所有三款AD951x产品均包含至少一个精细延迟调节通道,可编程满量程范围为1 ns至10 ns。 6位延迟字提供64种独特的延迟设置,步长低至16 ps。

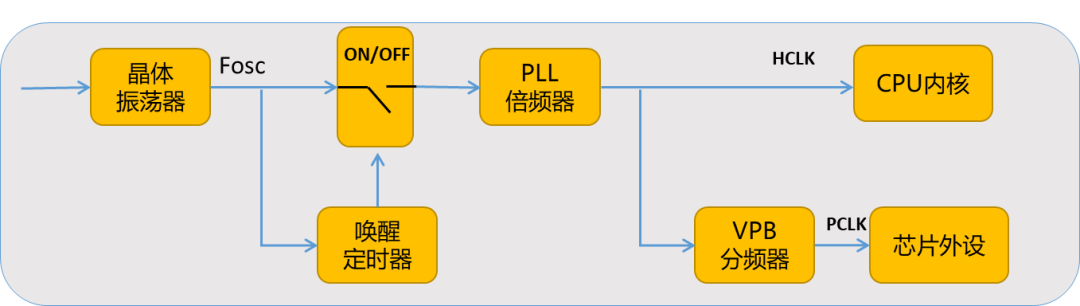

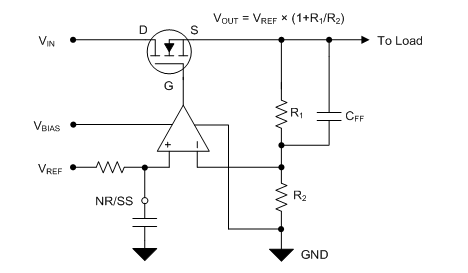

集成PLL频率合成器内核

AD9510和AD9511均集成了低电平相位噪声,1.5 GHz PLL频率合成器核心芯片。 PLL针对时钟应用进行了优化,包括可编程参考分频器,低噪声相位频率检测器,精密电荷泵和可编程反馈分频器。对于不需要片上PLL的应用,AD9512提供两个1.5 GHz时钟输入和五个独立时钟输出。

可用性和定价

AD9510现已开始提供样片,并于2005年2月开始量产.AD9511和AD9512开始采样于2004年12月,量产于2005年3月.AD9510采用64引脚LFCSP(引脚架构芯片级封装),千片批购价为每片11.95美元。所有三款AD951x产品均可在-40C至+ 85C的扩展工业范围内工作。

Click to Enlarge

ADI的时钟发生器IC

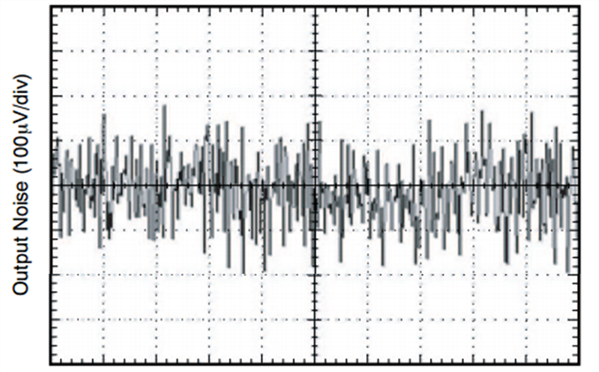

除时钟分配外,ADI还支持今年早些时候发布的AD9540的时钟生成。 AD9540时钟发生器专为满足高性能数据转换器严格的时钟要求而设计,有助于降低系统成本并提供宝贵的灵活性。 AD9540具有高性能PLL电路,包括灵活的200 MHz相位频率检测器和数字可编程电荷泵电流。该器件还提供低抖动(小于700 fs rms),655 MHz CML模式(PECL兼容)输出驱动器,具有可编程压摆率。支持高达2.7 GHz的外部VCO(压控振荡器)速率。极其精细的频率调谐分辨率(48位调谐字)和14位相位调整可实现对输出相位和频率的超精确控制。 AD9540的额定工作温度范围为-40°C至+ 85°C扩展工业温度范围。

-

adi

+关注

关注

143文章

45770浏览量

239997 -

分频器

+关注

关注

43文章

432浏览量

49298

发布评论请先 登录

相关推荐

提高系统效率的几个误解解析

矽力杰高性能20路PCIe时钟缓冲器

自动控制原理中,零点和极点对系统性能有什么影响?

飞机液压系统关键部件性能退化建模与仿真

高性能时钟有哪些特点 Xilinx 7系列时钟管理技术解析

车规级晶振:提升汽车电子系统性能的关键元件

一文带你详解芯片--SL8541e-系统性能优化

STM32有几个时钟源 STM32系统时钟专题讲解

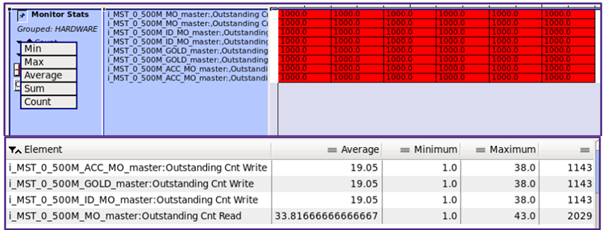

使用Synopsys智能监视器提高Arm SoC的系统性能

ADI的时钟IC是提高系统性能的关键

ADI的时钟IC是提高系统性能的关键

评论