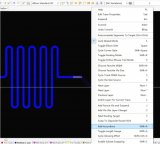

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。

高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据),一般要求延迟差不超过1/4时钟周期,单位长度的线延迟差也是固定的,延迟跟线宽,线长,铜厚,板层结构有关,但线过长会增大分布电容和分布电感,使信号质量,所以时钟IC引脚一般都接RC端接,但蛇形走线并非起电感的作用,相反的,电感会使信号中的上升元中的高次谐波相移,造成信号质量恶化,所以要求蛇形线间距最少是线宽的两倍,信号的上升时间越小就越易受分布电容和分布电感的影响。

因为应用场合不同具不同的作用,如果蛇形走线在电脑板中出现,其主要起到一个滤波电感的作用,提高电路的抗干扰能力,电脑主机板中的蛇形走线,主要用在一些时钟信号中,如CIClk,AGPClk,它的作用有两点:

1、阻抗匹配

2、滤波电感。对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的解决办法。一般来讲,蛇形走线的线距》=2倍的线宽。PCI板上的蛇行线就是为了适应PCI 3MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等.

-

PCB设计

+关注

关注

392文章

4571浏览量

83207 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

42573

发布评论请先 登录

相关推荐

什么是PCB扇孔,PCB设计中对PCB扇孔有哪些要求

电路板上的蛇形走线是什么

用这份PCB设计实战手册,轻松搞定RK3588

用这份PCB设计实战手册轻松搞定RK3588

可制造性案例│DDR内存芯片的PCB设计

可制造性案例│DDR内存芯片的PCB设计!

EMC之PCB设计技巧

AD9446 LVDS信号线的PCB走线的差分对间等长有没有要求?

PCB走线不要随便拉

PCB设计丨SATA硬件驱动器接口的可制造性问题详解

AD中PCB蛇形走线超级教程

pcb设计为什么要是用蛇形走线

pcb设计为什么要是用蛇形走线

评论