“互连组件”的概念与组件之间的总线和数据传输概念一样古老。互连组件支持在没有兼容接口的各种处理元件之间进行数据传输。它们还用于扩展没有所需扇出或足够带宽的系统总线,以满足数据传输需求。根据应用,使用不同类型的互连组件,具有不同的规格。一些流行的互连组件是双端口缓冲器,SERDES和PCI桥接芯片。以下是有效使用这些互连组件的几个示例:

将一个处理元件连接到另一个处理元件,例如,使用双端口缓冲器将DSP连接到RISC处理器。

将处理器连接到背板,例如,使用SERDES芯片将处理器上的并行接口连接到串行背板。

将处理器连接到总线,例如,使用PCI桥接芯片将主机处理器连接到PCI总线。

扩展总线,例如,使用PCI桥扩展PCI总线。

本文探讨了应用,要求和参数芯片到芯片互连,例如双端口缓冲器,用于将一个处理器连接到另一个处理器。由于简单的存储器接口,缺乏复杂的协议和各种选项,双端口缓冲器是最流行的芯片到芯片互连之一。此外,凭借广泛的组件组合,双端口缓冲器可有效支持各种要求,从电信号和数据传输带宽等基本物理层到多个虚拟通道等更复杂的需求。

以下部分深入探讨了互连标准演进过程,双端口作为默认互连,以及双端口如何满足各种应用的通用和特定需求。

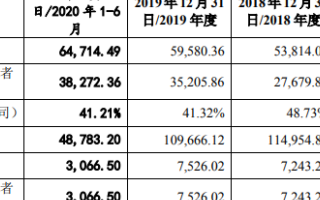

图1:互连组件示例。

标准:相关性,风险和更安全的方法

标准在定义接口方面发挥着重要作用。与专有接口相比,使用基于标准的接口有许多优点。使用标准接口可以提供多个组件这一事实提供了诸如易于设计,低成本和组件可用性等优点。使用标准接口的设计也提供了简便的可扩展性和设计可升级性。特定于应用程序的标准还提高了性能,因为它们针对给定的应用程序进但是,标准演进需要时间和精力。如下面IEEE标准的示例时间表所示(图2),标准的形成可能需要两年才能获得批准,可能还需要一年才能获得广泛的组件。

多方都是经过多年的努力,在批准和广泛适应之前,对即将推出的标准接口进行调整风险很大。

图2:IEEE标准流程图的时间线。

更安全和实用的替代方法是使用默认标准。对于给定的应用,默认标准不一定由行业机构开发。但是,默认标准是在许多具有明确定义规范的设备中使用的标准。使用默认标准可以获得准确的性能,并且业务风险有限。

SRAM接口:默认标准

具有双向数据总线,单向地址总线和相关控制信号的SRAM接口是最常见的接口之一在各种微处理器,数字信号处理器和其他处理元件上。标准SRAM接口也是最简单的总线,可以在CPLD和FPGA等可编程逻辑器件中实现。

今天的SRAM接口提供了选择总线宽度和高速I/O的灵活性,例如HSTL和LVTTL。它可以提供从几Kbps到36 Gbps的数据传输速率,具有72位总线宽度和250 MHz访问频率。这涵盖了芯片到芯片通信的各种应用的性能需求。

标准SRAM接口在大多数处理器平台(如RISC和CISC CPU,DSP和ASSP)中也非常常见。以下(图3)是具有SRAM接口的CPU的示例。这里要注意的一个关键点是这些处理器之间的接口速度和总线宽度的变化。

图3:几个具有存储器接口的流行DSP和处理器。

双端口缓冲器作为互连组件

鉴于存储器接口的存在非常普遍并且提供了诸如带宽之类的所需性能,因此存储器接口可以用作互连功能的“默认”接口。然而,存储器接口对于数据是双向的并且是用于控制的单向的。对于对等数据传输,绝对需要双向控制。双端口缓冲器使两个处理器都能像“主设备”一样工作,并有效地创建双向控制。

此外,双端口缓冲区提供了完全的灵活性,可以简化系统设计并实现性能目标,而不会增加多层协议的复杂性和与之相关的处理延迟。因此,双端口缓冲区通常用作互连组件。

为满足不同的系统要求,双端口缓冲区具有多种功能和参数。下一节将介绍双端口缓冲区如何解决各种系统的通用和特定于应用程序的需求。

实际问题

对于芯片到芯片的数据传输,互连组件(如双端口缓冲器)有效地弥合了不同的差距系统组件,解决了几个关键的互连问题:

时钟频率:两个处理元件之间的时钟频率差异给将数据从一个处理元件传输到另一个处理元件带来了严峻挑战。例如,在视频基础设施设备中,图像处理元件可以以一个时钟速率操作,而MPEG编码器在另一个时钟速率下操作。

在这种情况下,真正的双端口存储器可以使用自己的时钟连接这两个处理元件。由于设备的两个端口完全相互独立,因此这些时钟可以以不同的速率运行。

传输速率:两个处理元件之间的传输不匹配率非常高在多处理环境中很常见。在双端口互连中具有内置缓冲存储器有效地解决了这个问题。

图4:双端口解决方案符合物理层互连要求。

总线不匹配:总线宽度和电气接口的不匹配可能是约束或理想情况。例如,在设计升级中,经过验证的具有100 MHz LVTTL I/O的ASSP需要连接到FPGA。 ASSP可以以恒定速率抽出数据,但FPGA设计要求它以突发方式并以更高的传输速率输入数据。这意味着如果FPGA可以使用其200 MHz HSTL I/O,则可以使设计升级更加简单。

即使FPGA能够以恒定速率输入数据,使用只有一半总线宽度的200 MHz HSTL I/O可以显着增强电路板的PCB布线。更灵活的双端口在任一端口上提供各种不同的电接口,以最有效的方式解决这种情况。

通用控制和数据接口:控制平面和数据平面的通用物理接口是复杂多处理环境中的最佳要求。例如,在多个DSP在它们之间传输码片速率和符号率数据的无线基站中,它们还需要将控制信息(例如天线数,信号强度和过载情况)传送到另一个DSP。理想情况下,这需要通过用于数据平面的相同高速接口来实现,以保持电路板设计的复杂性。只有当接口能够支持多个虚拟通道时,才能执行此操作。

双端口缓冲区支持此要求,无需任何协议开销即可实现性能。通过使用邮箱,双端口缓冲区甚至可以向接收处理器发送中断信号,以进行高优先级控制平面通信。

虚拟通道:用于传输多个,独立的虚拟通道处理器之间的数据流可以从处理器中获取大量协议开销。

双端口缓冲区通过提供机制来灵活管理多个虚拟流,以便处理器可以处理这些虚拟流,如如果它们位于特定的存储位置。

互连的应用要求

除了双端口缓冲区解决的通用系统设计问题之外,如上所述,不同的应用程序要求定义了该特定应用程序的双端口缓冲区的参数。

例如,无线基础设施受性能的高度推动。 3G基站中的芯片到芯片数据传输可以达到多个Gbps。这要求互连组件不仅支持高数据传输速率,而且还提供足够的缓冲深度和架构灵活性,以支持高速数据传输。

同样,对于高端存储系统,支持多个虚拟通道的能力对于支持不同数据流的信用缓冲区非常有用。互连组件中的这种能力可以为系统设计增加更多价值。

新一代手机使用独立的基带处理器和应用处理器。连接手机中这两个处理器的双端口缓冲器需要非常小并且功耗很低。

最后,考虑视频基础设施环境通常同时处理多个视频源。通过互连组件的多个虚拟通道极大地简化了设计。

图5:双端口符合特定应用的互连要求。

处理器间互连要求通常随应用程序而变化。对于芯片到芯片的互连要求 - 在应用架构和优化的接口标准成熟之前 - 使用“默认”接口(例如存储器接口)可提供最佳性能而无需额外风险。

-

处理器

+关注

关注

68文章

18257浏览量

222079 -

dsp

+关注

关注

544文章

7681浏览量

344331 -

接口

+关注

关注

33文章

7633浏览量

148446

发布评论请先 登录

相关推荐

如何安装红杉WiFi组件?

无源组件与有源元件及机电组件的功能区别

有人有使用SPI-FRAM的示例代码或IDF组件吗?

CoreLink网络互连NIC-301技术参考手册

OpenHarmony组件复用示例

LTCC微波多芯片组件中键合互连的微波特性

多芯片组件(MCM),多芯片组件(MCM)是什么意思

兆龙互连拟募资4.28亿扩产数据电缆项目

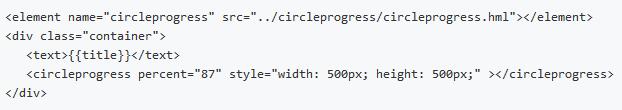

OpenHarmony自定义组件FlowImageLayout

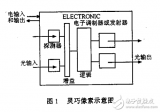

OpenHarmony自定义组件CircleProgress

互连组件使用示例

互连组件使用示例

评论