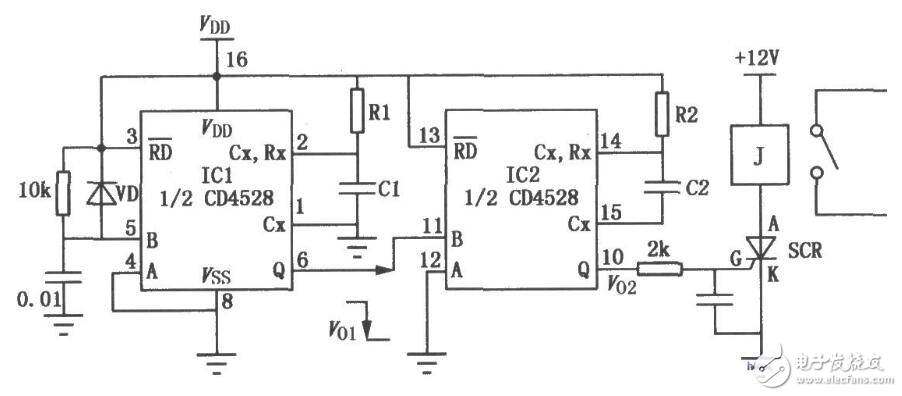

单稳态触发器CD4528组成的延时电路图如下:

单稳态触发器电路

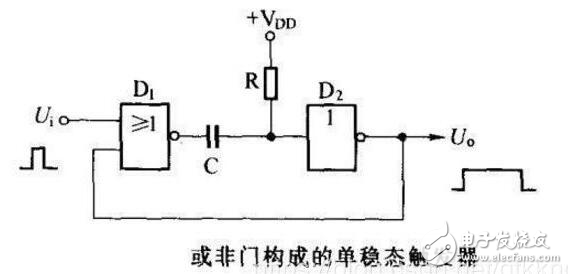

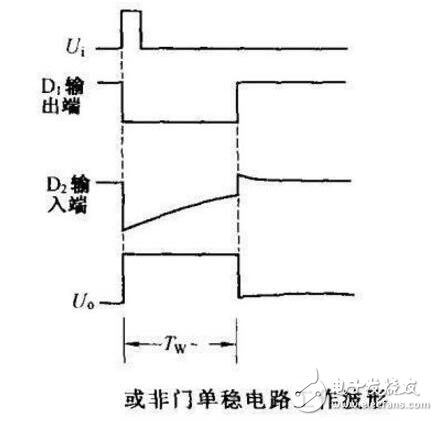

单稳态触发器电路处于稳态时,由于反相器D2输入端经R接+VDD,其输出端为0,耦合至D1输入端使D1输出端为1,电容C两端电位相等,无压降。

当在触发端加入触发脉冲时,或非门D1输出端变为0,由于电容两端的电压不能突变,因此D2输入端也变为0,D2输出端变为1,由于输出端电压又反馈到D1输入端形成闭环回路,所以电路一经触发后,即使取消触发脉冲Ui仍能保持暂稳状态,此时,电源+VDD开始经R对C充电。

随着C的充电,D2输入端电位逐渐上升。当达到反相器D2的转换阈值时,D2输出端又变为0.由于闭环回路的正反馈作用,D1输出端随即变为1,电路回复稳态。直至再次被触发,该电路各点波形如下图所示。

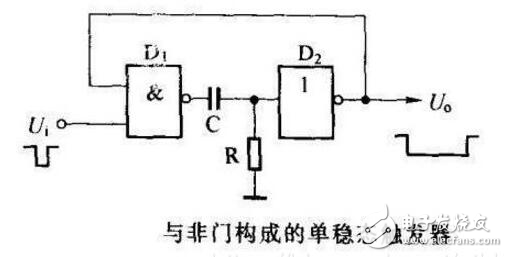

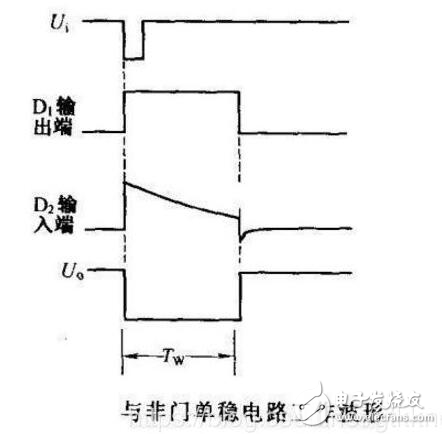

下图所示为与非门构成的单稳态触发器,电路由与非门D1,反相器D2,定时电阻R和定时电容C组成。和利用或非门单稳态触发器不同的是,定时电阻R不是接+VDD,而是接地。该单稳态触发器由负脉冲触发,输出一个脉宽为Tw的负矩形脉冲。

单稳态触发器电路处于稳态时,由于反相器D2输入端经R接地,其输出端为1,耦合至D1输入端使D1输出端为0,电容C两端电位相等,无压降。

当在触发端加入触发脉冲时,与非门D1输出端变为1,由于电容两端的电压不能突变,因此D2输入端也变为1,D2输出端变为0,电路进入暂稳态,随着C的充电,D2输入端电位逐步下降,当达到反相器D2的转换阈值时,D2输出端又变为1,电路回复稳态。直至再次被触发,该电路各点波形如下图所示。

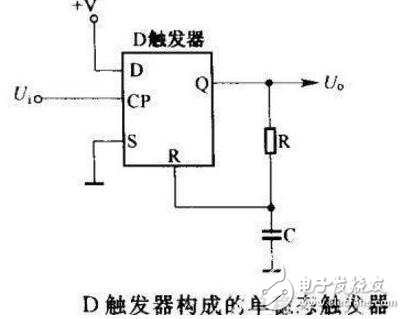

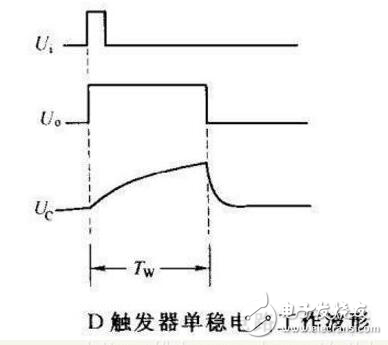

D触发器构成的单稳态触发器电路如下图所示。R为定时电阻,C为定时电容。D触发器的数据端D接1电平(+VDD),置1端S接地,输出端Q经RC定时网络接至置0端R,触发脉冲从CP端输入,输出信号由Q端输出。该单稳态触发器由正脉冲触发,输出一个脉宽为Tw的正矩形脉冲。

电路处于稳态时,Uo为0,当触发脉冲Ui加至CP端时,Ui上升沿使数据端D的1到达输出端Q,电路转换为暂稳态,U0=1,并经R向C充电。随着充电的进行,当电容C上的电压达到R端的转换电压时,使D触发器置0,Uo=0,电路回复稳态。这时C经R放电,为下一次触发做好准备。该电路各点波形如下如图所示。

-

触发器

+关注

关注

14文章

1674浏览量

60380 -

单稳态触发器

+关注

关注

1文章

44浏览量

23989

发布评论请先 登录

相关推荐

单稳态触发器有几个稳定状态 单稳态触发器的特点

单稳态施密特触发器与多谐振荡器有什么区别?

d触发器有几个稳态 触发器上升沿下降沿怎么判断

单稳态触发器的工作过程是什么 单稳态触发器的输出状态有哪些

什么是单稳态触发电路 单稳态触发电路有哪些特点?有哪些应用

单稳态触发器暂稳态持续时间误差产生的原因是什么

施密特触发器工作原理 施密特触发器有几个稳态

单稳态触发器有几个稳定状态

rs触发器和双稳态触发器的区别

D触发器与亚稳态的那些事

单稳态触发器延迟电路

单稳态触发器延迟电路

评论