一个不寻常的电路,“tanktwanger”,提供了一些优于传统时钟合成方法的时钟产生和调整优势。您可以针对众多应用调整主电路,但在构建此VHF设计时必须注意。

当您考虑时钟合成时,通常会想到简单的数字分频或PLL。然而,使用线延迟线和称为“tanktwanger”的异常电路,您可以生产出具有众多优势的时钟发生器,包括连续可变的相位。虽然最初设计用于评估同步光网络(SONET)OC1/OC3(51.84/155.52-Mbps)光纤接收器的误码率性能,但该电路还可用作以太网数据包的时钟启动器。 ,从20MHz晶体生成光纤分布式数据接口(FDDI)125-MHz时钟,并进行频移。使用与表面贴装ECLinPS(皮秒级ECL)逻辑系列(摩托罗拉,凤凰城)相同的技术将电路的操作扩展到OC12频率(622.08 Mbps)及更高频率。

在位 - 的情况下错误率测试(BERT)设备,该电路允许您在旋钮转动时将测试设备的位时钟定位在数据眼图的任何位置。然后,您可以使用此时钟驱动BERT接收器,并扫描眼图上的时钟采样边沿或将边缘定位在中心,同时监控示波器上触发此时钟边沿的两个信号。这种方法优于将短长度同轴电缆拼接在一起的切割方式,以使时钟进入您需要进行测试的阶段。

原来的术语“tanktwanger”适用于数据包数据,时钟恢复电路,当关闭水箱的直流电时,它会在第一位开始时立即启动LC水箱振铃偏压释放被压抑的磁通量。效果类似于敲琴弦,因此得名。该术语也适用于通过一系列共振脉冲对LC水箱进行温和的数字泵送,类似于每隔一个或第三个周期用一把弓抚摸小提琴或将孩子推到秋千上。您可以使用此技术来乘法,加法和减去频率(外差),从而使您免受仅用于时钟合成的数字除法和PLL的限制。

为了产生奇次谐波,您通常会驱动坦克来自对称(50%占空比)的数字方波。如果需要均匀谐波,则可以使用非对称脉冲驱动油箱,该脉冲来自异或门,延迟线等于所需谐波周期的一半。

平衡线圈的物理膨胀(正温度)系数)与电容器有意选择的负温度系数使得水箱的温度稳定性足够紧,以满足大多数实际需要。各种负温度系数的射频质量电容器随时可用;从NP0或C0G(每摄氏度变化小于30 ppm)到N1500(负1500 ppm/°C)或更高,以稳定LC储能电路。两个不同系数的并联电容器具有适当选择的皮法电压比,可以产生您需要的任何非标准温度系数。

Tanktwanger将ECL与LC罐相结合

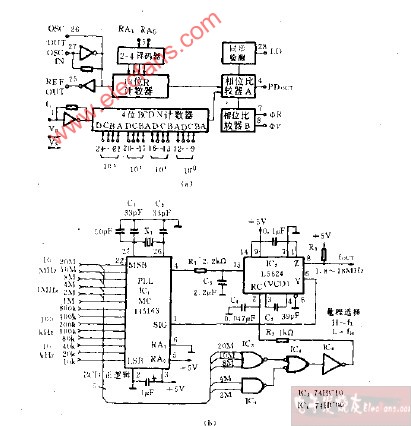

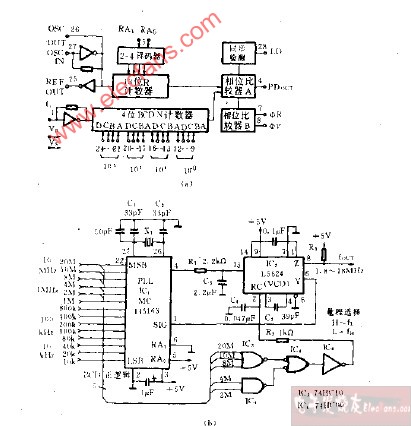

图1中的tanktwanger相移电路使用但不限于Motorola 10H ECL家族。您还可以在OC12速率(622.08 MHz)和更高频率下使用这种时钟合成方法,仔细构建并使用ECLinPS逻辑系列而不是10H系列。该图未说明IC引脚编号,因为物理布局因应用和尺寸要求而异。您必须选择引脚编号和IC的物理方向,以最大限度地减少非同轴引线长度。有关终端下拉电阻和传输线效应的基本知识,请参阅适用的Motorola数据手册和参考1。

图1a基于“tanktwanger”和延迟线的操作,该相移电路产生一个可变相位时钟,可用于调整数据眼图的采样边缘以进行制作误码率测试设备测量。您可以将此技术扩展到其他时钟生成电路,它也可以用于生成误码浴缸曲线。

图1b时序图显示了一些重要的波形。

请注意,电路接地连接到测试设置的公共,接地和台式设备底盘接地。两个电压,2V和-3.2V,为电路供电。 ECL具有开路发射极输出,可在±5V系统中将几百欧姆驱动至V EE 。但是,ECL输出也可以驱动50欧姆到V TT ,比V CC <负2V的电压/子>。通过将V CC 定义为2V,V TT 变为系统地,这提供了方便50欧姆跳线和测试设备终端50欧姆到系统地。即使在您的面包板上,您也会发现使用这个单电阻可以很容易地终止50Ω传输线。

从BERT发送器提供155.52-MHz差分时钟的50欧姆同轴电缆终止于电路接地。 IC 1A 的线路接收器缓冲时钟,IC 2 的双D翻转-flop将其除以4到38.88 MHz。 IC 2B 的输出驱动一个LC谐振电路,调谐到38.88 MHz谐振。电压相关电容器(变容二极管)是储能电容网络的一部分。当您调整其偏置电压时,该电容会将谐振频率略微高于或低于38.88 MHz。这种调节可使油箱正弦波的相位延迟或提前超过±45°。

缓冲放大器IC 1B 使正弦波平方。该ECL线路接收器通常以其输入对称关于V BB 进行操作(比V CC ),但其共模范围允许它在使用2和-3.2V电源时在地面附近工作。这两个电源电压简化了电路,因为两个缓冲输入均直接接地,一个通过线圈,不需要偏置电阻。这些电源电压设置还允许通过简单地直接焊接到接地层来轻松机械安装微调电容器和空气缠绕线圈。

方形38.88-MHz信号驱动端接延迟线长度等于155.52-MHz时钟周期的一半,或3.215纳秒。该线路仅为64.3厘米的RG174同轴电缆,其传播延迟为1纳秒/20厘米。 IC 3 对延迟线的输入和输出进行异或操作,在每次输入转换时产生3.215纳秒宽的脉冲。

此脉冲它具有丰富的均匀谐波和四倍于155.52 MHz的倍频槽。每隔一个周期,XOR脉冲会对油箱进行振动,并且油箱本身会响起以填补缺失的脉冲。 IC 4 中的缓冲放大器正弦波正弦波 - 不要重复使用IC的部分 1 避免串扰抖动 - 为测试设备产生可调节相位的OC3时钟输出,其中同轴电缆以50欧姆端接到台式(接地)地。由于38.88-MHz时钟可以至少摆动±45º,因此乘以4的时钟至少可以旋转±180°,即大于一个完整的时钟周期。

如果你使用51.84-MHz OC1时钟输入而不是155.52-MHz时钟,那么38.88-MHz坦克会以12.96 MHz的三次谐波振铃,而不是基频,电路仍然产生OC3时钟。只需在IC 6 处添加一个线或或,3分频,双D触发器计数器,即可创建相位可调的51.84-MHz时钟,允许电路很容易适应OC1。

考虑其他tanktwanger应用

图2 ,3和4中的简化示意图显示了其他内置和测试坦克的可能性。这些数字并没有显示所有电路细节,只是一般的想法。

图2这款基于tanktwanger的10Base-T以太网数据包的时钟启动瞬间响起,第一位的时钟边沿在眼中心后半个符号时间立即可用。

图2中的电路 - 术语“tanktwanger”的真正灵感 - 在以太网数据包间隙期间对直流电感器进行直流偏置。第一个输入数据位的第一个边沿时钟IC 3A 并强制输出IC 2A 从低到开收集器。此动作使坦克立即振铃,并且该第一位的时钟边缘在眼睛中心稍后立即可用半个符号时间。 ECL缓冲区作为正ECL(PECL)运行;串联二极管将输入置于此缓冲器的共模范围内。

25 ns的有效延迟线和异或门,IC 1A ,从每个数据边缘生成脉冲。将这些脉冲施加到罐上可在包的持续时间内保持振铃。这种使用数据边缘振荡油箱的技术是众所周知的,但由于油箱的Q(品质因数)而导致启动延迟。油箱的Q是电抗与电阻损耗之比。但是,直流偏置关断的额外冲击确保了即时时钟。这种额外的冲击是你试图通过在它们上面放置一个二极管来抑制继电器线圈的现象。此步骤可防止继电器线圈的关断尖峰(实际上是继电器线圈和杂散电容形成的振荡电容)导致开关晶体管死亡。

图3晶振驱动坦克达到100 MHz的五次谐波,从20 MHz晶振产生一个125 MHz的FDDI时钟。

图3从20 MHz晶振产生FDDI 125-MHz时钟。晶体驱动坦克达到100 MHz的五次谐波。电路缓冲该信号,将其除以4得到25 MHz,并用100 MHz信号对结果进行异或。 XOR在频域中进行外差,产生输入频率的和与差。 125 MHz的总和振荡第二个储能电路,缓冲器在储能正弦波上平方,产生125 MHz的FDDI时钟。

图4要从16.384 MHz输入产生57.6 KHz采样时钟,您可以将此基于频率移位器的频率移位器调谐到其九次谐波。这里示出了不同的偏置布置,其允许ECL级从“标准”单电源供电。在铜线pcb原料上做这个时,权衡是线圈和微调帽的Vtt地平面机械锚点的损失 - 如果使用slug调整现成的线圈,这不是问题。

图4的移频器将数据专用交换机的16.384-MHz主时钟除以256,以生成64 kHz的RS-232C采样时钟。通过将主时钟频率移至14.7456 MHz,该电路对于暂时将采样时钟移至57.6 kHz,恰好是标准9600波特率的六倍的测试是必要的。主时钟必须保持锁相到实验室网络参考,需要主电压控制晶体振荡器(VCXO)/PLL,不能用函数发生器代替。问题是那个特殊频率的VCXO没有时间。图57.6 kHz恰好是64 kHz的十分之九。电路将主时钟移位相同的比率除以10(前5个,然后是50%对称波形为2),然后用tanktwanger乘以9,产生14.7456 MHz的移位主时钟。

构建测试夹具

分析所有这些tanktwanger电路的工作原理相对简单;实际上,从真实的物理布局中实现您想要的电路性能需要技巧。您需要知道如何构建此VHF/ECL电路,如何安装和调整储罐,如何正确地进行互连,以及最后如何探测和调试电路。这些项目在高频率下都不是微不足道的。通过遵循以下建议的做法,您可以构建高效的面包板,以便在ECL和其他宽带模拟或数字技术中运行良好。

本讨论重点介绍了构建以下所需的物理布局和设计实践。相当简单但专业的测试夹具。有时,可能只需要一个特殊测试电路的副本,并且在这种情况下,如果您可以在穿孔板上手工构建电路板,那么铺设电路板几乎不值得。但是在涉及VHF频率和ECL的地方,穿孔板并没有完全削减它。如果电路完全可以工作,那么只有一个实心铜接地层。

这个测试夹具使用标准DIP封装的ECL 10H系列,便于组装,尽管你可以调整两种技术。通孔和表面贴装RF IC。您可以通过将0805尺寸的电阻替换为1206种类型来实现面包板表面贴装封装。您需要使用镊子而不是尖嘴钳,稳定的手是一种资产。此外,使用细尖烙铁,薄无焊剂焊料和免清洗助焊剂,并尽可能降低热量,以避免损坏组件。熟练的汇编程序的服务在这里是个好主意,尽管即使是最笨手指的工程师也应该能够处理DIP封装。

准备面包板和IC引脚

从一块双面铜包层开始, 1 / 16 -in。印刷电路板材料切割成您认为需要的两倍大。像tanktwanger这样的电路往往会增加附加功能;留出足够的空间用于设计即用型添加物。当您完成并调试电路后,那时你才应该用钢锯小心地切掉多余的印刷电路板。确定IC物理位置并选择电路引脚,以最大限度地减少非同轴引线长度。为每个储能电路留出足够的空间(1英寸 2 )。

顶部元件侧铜平面接地。这个平面是焊接大多数以地面为参考的零件以进行机械支撑的地方。它连接到工作台设备和地面。底面平面用于分配2V电源。每个ECL IC封装的引脚1和16穿过元件侧的埋头孔(使用带#68钻头的旋转手动工具钻孔),然后将引脚焊接到该下侧平面(图5)。使用 3 / 16 -in执行地平面的counters孔。手钻夹头中的钻头足够深,以防止IC引脚在通过时短路到地平面。将IC的剩余引脚(不是1和16)向外弯曲90°并切断它们的“尾部”以留下 1 / 8 -in.-long”pinpads“用于电线和元件连接。将自粘橡胶支脚放在底部平面的角落和中间,以便将您的电路板支撑在工作台上,并在探测时防止其滑动或短路。

图5IC和元件的布局和布线对这些VHF电路尤其重要。使铜板Vtt接地的顶部和底部进行配电。焊接电容直接从IC接地。将50欧姆端接/下拉电阻焊接到引脚下方和Vtt接地层。

安装准备好的IC时,将每个封装的引脚1和16从地面推入预先钻好的埋头孔 - 平面侧,将它们折叠,并将它们焊接到2V底面。每次添加下一个芯片时,请测量从2V到地的电阻,以确保不会造成任何短路。

当所有IC都安装好后,安装去耦电容(图5的)。您可以在每个IC电源引脚和接地层之间直接焊接这些0.01至0.1 mF,1206尺寸的表面贴装型。使用低热量快速小心地焊接,以避免电容器陶瓷开裂。每个芯片使用三个电容 - 一个用于两个V CC 引脚,另一个用于V EE pin。安装每个电容器后,用DVM检查是否有短路。在卡上安装至少一个10至100μF的钽电容,电压从2V到接地;用于IC电源引脚的2V孔钻孔和埋头孔。

使用28到30 AWG绝缘线,从中心点以星形方式将-3.2V分配到所有IC的引脚8。将机械大的10至100μF钽电容焊接到接地层(记住将正极引线接地)和-3.2V焊接作为滤波器和中央机械连接点。

将红线焊接到2V平面,将绿线焊接到地平面,将黑线焊接到-3.2V连接点,以连接到两个实验室电源。标记电线的功能,并使用细尖毡标记将它们直接写在印刷电路板上,以最大限度地减少某人有朝一日用不正确的电源连接炸毁电路板的可能性。如果发生反极性电压应用,每个电源对地和一对保险丝的反向偏置功率二极管也可以很长时间地保护您的工作。

安装油箱

您的电路板现已准备好用于储能电路(图6)。安装38.88 MHz的第一个储罐及其变容二极管网络。完成足够的布线以测试并使第一个坦克产生共振是个好主意;然后,安装足够的布线和第二个坦克并使其共振,依此类推。在每个构造步骤中验证电路比在一次性构建的面包板上同时确定多个错误的来源要好得多。

图6对于储罐本身,使用连接调节螺钉的端子将修整器电容器焊接到接地层。对于电感器,您可以将总线导线缠绕在铅笔 1 上。

使用电气连接到调节螺钉的端子将微调电容器焊接到接地层。这种连接是必要的,因此用金属工具接触调节对调谐的影响最小;当您移除工具时,由于杂散电容的变化,您不希望调整发生变化。使电容靠近缓冲放大器输入引脚。您应该放置整个油箱部分,包括驱动ECL输出和缓冲输入引脚,以允许该区域的最小引线长度。

接下来,用铅笔或白板上的裸镀锡母线缠绕油箱线圈标记,在每个绕组之间放置一些空间,使相邻的转弯不会相互短路。风额外转弯(总共七或八)并在共振后切掉多余的部分。在一端弯曲一英尺,用于焊接到地平面。如果防止意外的物理糖化,可以接受细线。重型导线可以提高Q和战舰的稳健性。

更高的Q提高了最终信号的光谱纯度,但只要合理(20或更高),Q值并不重要。不要使用有损陶瓷谐振电容器;只使用良好的射频质量,固定陶瓷或微调电容来保持良好的Q值。确保电容器损耗由制造商在射频频率而非1 kHz下规定。

注意传输线互连

您必须使用微型50欧姆同轴电缆(RG174是常见类型)进行长度超过一英寸或两英寸的连接,该电缆终止于驱动源的最远端一个49.9欧姆,1%1206表面贴装电阻到接地层。您使用的所有ECL输出都需要此下拉电阻,即使连接物理上太短而无法保证传输线。然而,这种要求的优点在于,在传输线环境中并且正确选择电源电压,下拉电阻也可以兼作匹配线端接,防止线路反射及其相关问题。这种使用长线的能力允许您创建精确的延迟线,因为同轴电缆上的传播延迟(光速为66%或每20厘米为1纳秒)。再次,阅读参考1了解更多的传输线理论和设计实践。

在面包板上,50欧姆的终端电阻非常适合放在它们之间接地层和芯片键盘的下侧。小心焊接两者。将同轴电缆的中心导体焊接到插针的顶部,并将同轴屏蔽编织层焊接到附近的接地层。

保持同轴电缆编织连接和露出的中心导体尽可能短。使用锋利的造型刀准备同轴末端以减少 1 / 4 in。绝缘夹克。尽量不要剪断任何编织线 - 两根或三根断线都可以。不要让股线在印刷电路板上滚动,它们将落在芯片下并最终导致短路。在每个电缆末端将编织线分成两组,以焊接到地平面;与单个编织连接相比,这种连接提供了更安全的电缆固定。剥去中心导体绝缘层以留下编织分裂的绝缘层 1 / 16 in。 -off point。

焊接时需要注意RG174同轴电缆。耐热特氟龙电缆也很容易买到,但使用特氟隆的难度超过了RG174。如果过热保护编织线并且电缆末端存在物理应力,RG174的中心电介质可能会在焊接过程中熔化。结果是中心导体和地之间短路。为避免此问题,请在尖嘴钳的手柄周围缠上橡皮筋,用散热片夹住护罩(图7)。 (您可能还记得以这种方式焊接锗晶体管。)

图7在尖嘴钳的手柄周围缠绕橡皮筋以形成散热片可防止RG174同轴电缆的中心电介质在屏蔽编织线焊接过程中熔化。

最后,您可以使用双面铜包覆印刷电路板材料的碎片为敏感的模拟接收器前端构建屏蔽“房屋”( 1 / 32 -in。厚度为此目的是优选的)。您甚至可以使用锡罐或薄型沙丁鱼罐作为印刷电路板外壳或焊接到地平面的薄型印刷电路板区域屏蔽。电源引线可以通过穿通电容器穿过屏蔽墙,您可以切割金属中的槽口以允许信号电缆退出。

调整储罐

坦克的共振频率f o 等于1/(2π√LC)。为了正常运行,需要将每个油箱调整到频率。具有可调磁塞的已知值的线圈是容易获得的。然而,对于实际的VHF值,几圈刚性#12至#18母线的一端刚性焊接到接地平面很容易制造,这是必要的。调整微调或选择最接近的标准固定电容值,并通过线圈的物理失真和抽头选择进行调谐。

您如何知道调谐的方式?使用10:1示波器探头监测储罐正弦波并计算循环时间。尝试将一小块铁氧体放入线圈中以提高其电感并降低其共振频率或一小块黄铜以达到相反的效果。将匝稍微靠近以提高电感,然后将它们像弹簧一样拉伸以降低它。观察正弦波,你想要的频率,或其谐波,开始从泥浆中升起并变成纯净的音调,同时你将坦克调整为精确的共振。

一旦找到任何谐波通过了解您的储能电容,您可以计算出线圈的电感,并从中计算出所需的电容,将其调谐到所需的谐波。但是,围绕铅笔或白板标记绕五圈或六圈更容易,在使用5到100-pF微调电容器搜索所需的谐振频率时,稍微用它来找到合适的线圈抽头点。

在探测储能缓冲器输出时的方波时,通过触发原始时钟源的范围并注意缓冲时钟的相对相移,同时通过调谐储能槽来找到精确的调谐谐振。将相位定位在其可调范围的中间位置。您应该将38.88-MHz信号中心调谐,并将相位调节电位器设置为其相位摆动范围的中心。

图1中的储能电路与其驱动器之间的10 pF耦合电容提供峰值到峰值的振铃约为300到500 mV,以确保缓冲放大器完全削波。该电容的值取决于油箱的Q值和倍频系数,但该值并不重要。尝试一些值,找出最适合你的线圈;在大多数情况下,10 pF应该足够了。

如果使用可调铁氧体磁芯调谐,请确保使用正确尺寸的塑料校准工具。使用错误的工具,特别是金属螺丝刀,是保证核心裂缝并将其紧紧锁定在适当位置的保证方法。

如果你真的想使用商店购买的slug调谐线圈,最后要小心而不是缠绕你自己的高Q,空芯瞬间特价:当你将塞子拧入并通过绕组时,电感将上升然后再次下降。如果储能电容太小,储能电路可能看起来接近共振但从未到达那里。对于trimcap来说情况也是如此,它可以调整到最大值或最小值,然后远离最大值或最小值。确保在中间调整点附近有两个共振峰,因为铁氧体螺栓穿过线圈,或者每360°修整旋转有两个共振峰。

探测和调试电路

请记住,您的示波器探头会增加大约10 pF的储能电容,因此当您取下探头时,请重新加注或添加一个10 pF的固定电容。确保您的探头使用探头套件附带的弹性小物件,以获得坚固,无噪音的示波器轨迹。探测时,将弹簧向下按到印刷电路板接地层上。不要使用4英寸。您可以在高速CMOS环境中使用探针接地线。对于免提探头固定,请使用从IC插座中切出的空心圆形销(图8)。将引脚焊接到地平面;然后,示波器探头弹簧滑入插座销并保持相当牢固。使用相同的设置来保持裸露的探头尖端直接戳过探头弹簧。

图8用于免提探测你可以使用从IC插座获得的引脚。将引脚焊接到接地层后,示波器探头弹簧滑入插座并保持住。

如果要显示ECL输出,可以从该点移除50欧姆端接电阻,并将其替换为端接在示波器50欧姆输入端的焊接RG174电缆,以获得最准确,无噪声的示波器显示。

您可以通过焊接一个450欧姆的电阻( 1 / 8 W轴引线,非表面贴装)在测量点与RG174同轴电缆串联,RG174同轴电缆由示波器的50欧姆输入端接(图8)。该探头以500欧姆的负载加载被测电路,与普通的50欧姆负载相比几乎可以忽略不计。保持电阻器引线和外露的同轴中心导体和屏蔽只需要足够长的时间来完成工作。不要用这种方法测量坦克正弦波;坦克需要高阻抗负载才能在谐振环处振铃。

RG174微型50欧姆同轴电缆推荐用于OC3频率及以下的设备互连,因为它们非常灵活,可以轻松放在台面上。保持这些电缆长度相同(2m是一个良好的通用长度),以避免时钟与数据测量错误导致不同长度的时间偏差。 20厘米电缆的时间偏差相当于1 ns。等长电缆对差分信号同轴电缆对尤为重要。

注意事项:

1。线圈通常为一至六圈AWG12-16裸露的实心母线,围绕白板标记或铅笔形成,具有1/8至1/4英寸的转弯间距。实际转数取决于所需的共振频率和微调值。只要通过调整实现共振,绝对LC值并不重要。

选择带有微调电容的合适线圈抽头,调谐到所需的谐振频率。然后,您可以切断多余的转弯。

如果需要最大油箱Q,则保持铜平面上方的半个线圈直径高度。通常不重要。

您可以调整10pF电容值,以获得300至600 mV的峰峰值正弦波。最终值取决于罐Q和倍增因子。 10pF适用于大多数应用。

理论上,较大的C/L比率可以提供更高的负载Q,但ECL放大器负载已经很轻,我从未在实验上改变C/L比率看到太大差异。

-

电路

+关注

关注

170文章

5480浏览量

169503 -

PCB打样

+关注

关注

17文章

2965浏览量

21383 -

华强PCB

+关注

关注

8文章

1831浏览量

27459 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

42574

发布评论请先 登录

相关推荐

ADCLK946是否可以直接给AD9739作为时钟驱动LVDS

Spartan 3-AN时钟和VHDL让ISE合成时出现错误该怎么办?

为时钟源编程的计算机并行端口

采用MPC92433高性能时钟合成源完成时钟信号电路的设计

什么是tanktwanger及Tanktwanger电路为时钟合成带来哪些变化

什么是tanktwanger及Tanktwanger电路为时钟合成带来哪些变化

评论