作为SDRAM家族的新一代内存产品,DDR3提供了相较DDR2 SDRAM更高的运行效能与更低的电压,是DDR2 SDRAM的后继者,也是现时受各大公司欢迎的内存产品规格。

DDR3产品最大的特性就在于功耗小且效率高,这让它迅速获得前代DDR的市场。究其高效率的关键,在于DDR3采用了相较于DDR2的1.8V更低的工作电压:1.35V。那么,如何才能够得到稳定高效的供电电压?如何又能够简单而有效地控制电压?

为此,MPS重点推荐能够完美解决这一系列问题的高集成度芯片---NB685。

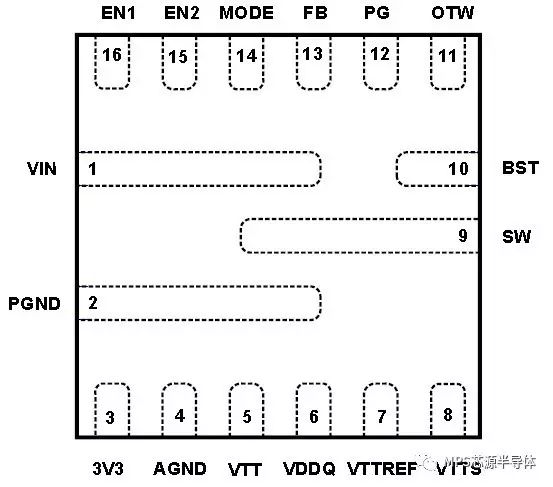

规格:3mm*3mm

如此小巧的身躯,又是如何能够承担起如此艰巨的任务呢?

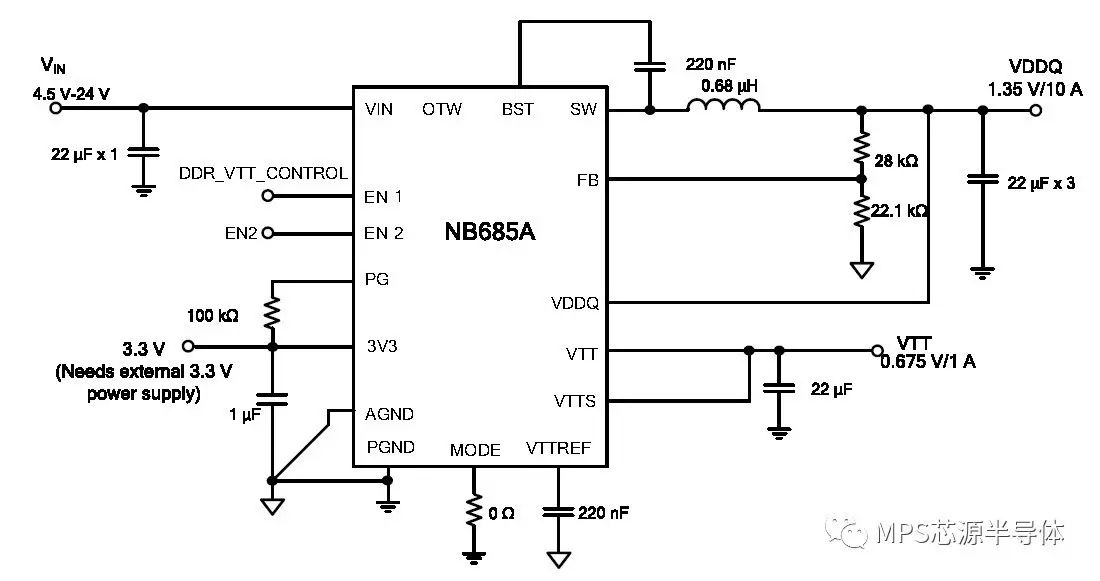

NB685简约而不简单,只需要简单而又不占太大空间的外部电路,即可有效地控制供电电压,使其能够为诸如DDR3, DDR3L, LPDDR3, DDR4等内存供电。并且输出电压可调节,只要微调外部电路即可。

当然,NB685在出色完成基本任务的同时,本着精益求精的原则,始终走在同行业的前列,拥有诸如以下优势:

1 强大的负载能力

能够承受12A的持续输出电流,以及13A的瞬时输出电流;1%的VTTREF输出电压精度;

2 极大地消除工作噪声

NB685拥有USM MODE(超音频模式),即使在低负载工作也不会造成声音污染;

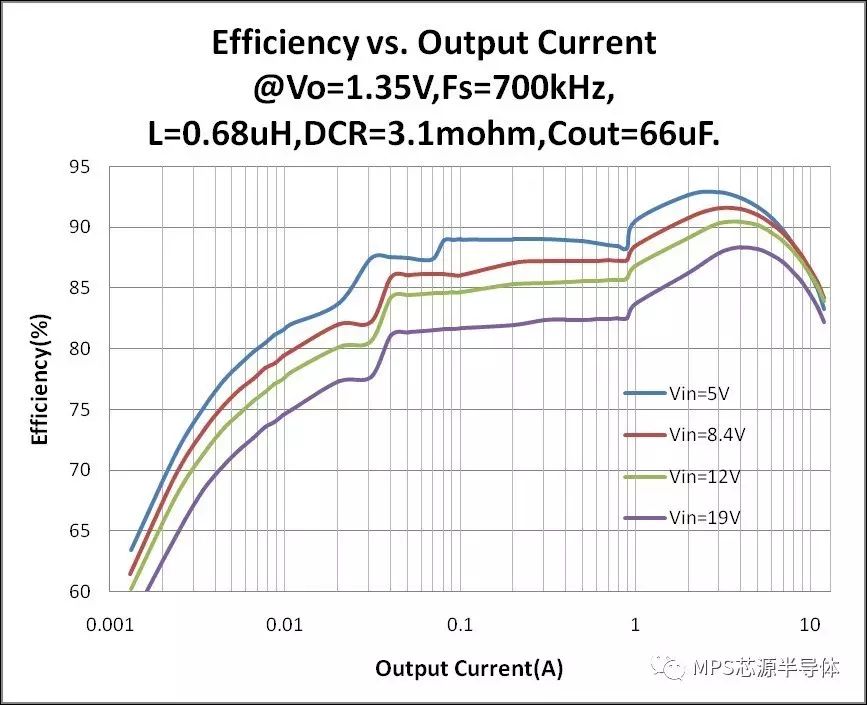

3 超低的静态电流(135uA)

使芯片在待机过程中不产生过多的能源损耗,极大的提高了工作效率;

即使是低负载工作状态,也能够维持在60%以上的效率!

正常工作效率最高能够达到90%以上!

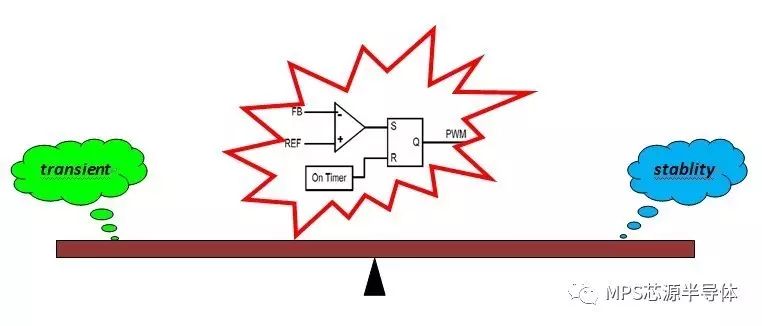

4 采用COT控制原理

完美平衡了高频状态下的稳定性与动态响应性能之间的矛盾关系;

5 周全的保护电路

诸如过流保护、过温保护、高低压保护之类的芯片保护设计,极大程度地降低了芯片在恶劣环境或者突发事故中的损坏率,更好的为芯片保驾护航。

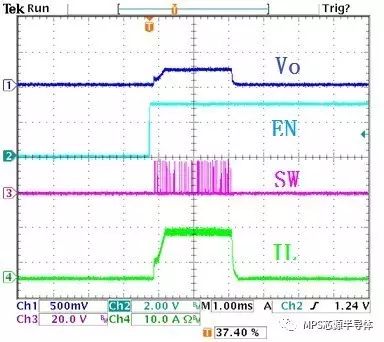

输出短路测试

即使在输出短路下,芯片的电流一直能够控制在13A左右而不损坏芯片!

应用领域:

-

电源

+关注

关注

182文章

16543浏览量

244668 -

电路

+关注

关注

170文章

5480浏览量

169475 -

静态电流

+关注

关注

3文章

187浏览量

20691

发布评论请先 登录

相关推荐

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据表

完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

DDR3存储厂迎涨价商机 华邦、钰创、晶豪科等订单涌进

DDR4和DDR3内存都有哪些区别?

DDR3和DDR4的技术特性对比

DDR3的规格书解读

关于简单高效解决DDR3电源供电问题的分析和介绍

关于简单高效解决DDR3电源供电问题的分析和介绍

评论