数据中心设备制造商长期以来一直热衷于利用FPGA可能实现的大规模并行性,以在高效的功率预算内实现与需求保持同步所需的处理性能和I/O带宽。然而,传统上,在FPGA中实现硬件计算平台一直是一项复杂的挑战,需要设计人员处理一些最低级别的硬件实现。

尽管一些最新的FPGA设计方法结合了高级综合(HLS)工具和软件编程语言(如OpenCL,C和C ++)简化了任务,并没有消除对专业FPGA设计专业知识的需求。需要一种高级工作流程,允许软件工程师将FPGA用作软件定义的计算平台,而无需硬件设计的痛苦。为满足这一需求,此类工作流应该能够:

从纯软件代码创建功能硬件

合并现有硬件IP块,如果

支持使用商用,现成的电路板和自定义平台

通过构造确保生成的硬件正确,从而消除硬件调试

仅支持使用标准软件调试工具调试功能块

考虑一个包含两个基本功能的软件算法:将数据处理成一个函数,然后发送到另一个函数进行进一步处理。从软件的角度来看,这个实现就像调用Function1(),然后单独调用Function2()一样简单,使用指向要处理的数据位置的指针。

图1对数据执行的功能

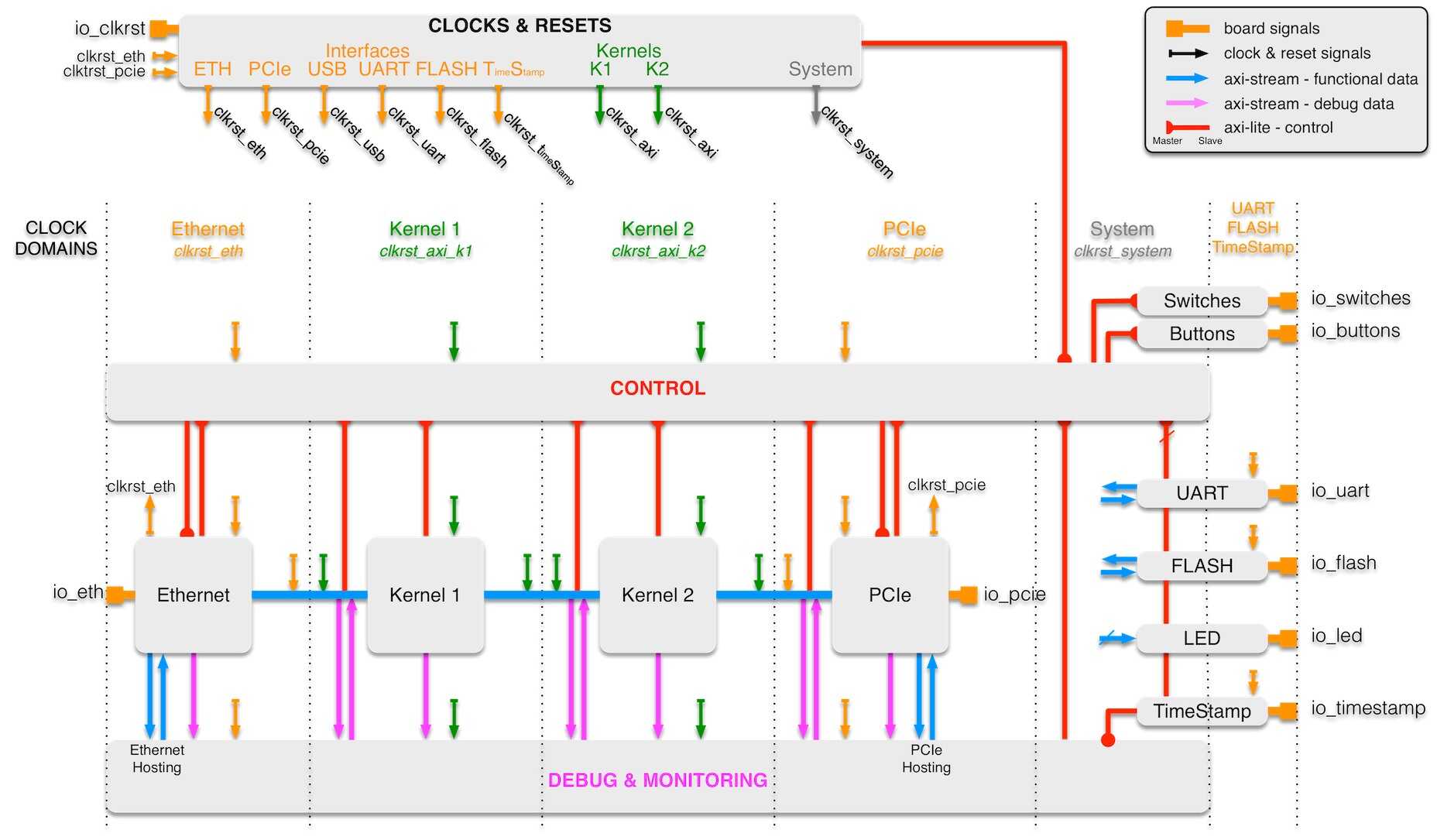

实施此类在没有正确的硬件抽象工具流程的基于FPGA的硬件平台上的算法将要求软件开发人员提出类似于图2中的硬件设计(其中内核1和内核2各自相应)功能1和功能2的硬件实现。

图2使用双功能算法的详细硬件实现传统的FPGA工具

硬件设计需要包括控制平面和数据平面。控制平面是执行引擎,它生成时钟和重置,管理系统启动,编排数据平面操作,并执行所有内务处理功能。数据平面实例化并连接处理元素,内核1和内核2,以及读取数据和写入处理数据所需的必要I/O接口。在图2中所示的示例中,这些接口是以太网和PCI Express(PCIe)。

熟悉的挑战

没有特定硬件专业知识的软件开发人员可以使用高级综合工具(如 Vivado HLS )生成内核1和内核2,以编译软件函数Function1()和Function2( )用C或C ++编写的VHDL或Verilog的FPGA硬件描述。但是,使用HLS工具无法生成设计的非算法元素,如接口,控制,时钟和复位。需要硬件设计人员将其创建为自定义IP。获取这些元素并连接它们的工作带来了另一个挑战,因为某些元素可能不容易获得,或者可能具有不同类型或大小的接口以及不同的时钟要求,特定的启动顺序等等。

实施设计同样面临严峻挑战。这些包括将设计映射到所选FPGA平台的资源,生成适当的约束,并确认在FPGA硬件上进行逻辑综合和实现后满足这些约束。即使是经验丰富的硬件设计人员也可能需要数周才能在新的FPGA硬件上实现最简单的设计。

新方法

PLDA集团是嵌入式电子系统和IP的开发商,它创建了QuickPlay,允许软件开发人员完成这些任务,从而在FPGA硬件上部分或全部实现CPU的应用程序。在这种以软件为中心的方法中,设计人员首先开发硬件引擎的C/C ++功能模型,然后使用标准C/C ++调试工具验证功能模型。然后指定目标FPGA平台和I/O接口(PCIe,以太网,DDR,QDR等),最后编译和构建硬件引擎。

为了使这个过程无缝工作,必须保证生成的硬件引擎与原始软件模型的功能相同。这意味着模型必须是确定性的,因此它将产生与硬件相同的结果,无论硬件实现运行得多快。不幸的是,大多数并行系统遭受不确定性执行。例如,多线程软件执行取决于CPU,OS,以及在同一主机上运行的非相关进程。多次运行相同的多线程程序可能会有不同的行为。

硬件中的这种非确定性需要在电子波形级别调试硬件引擎本身。这将破坏针对软件开发人员的工具的目的,但QuickPlay的数据流模型保证了确定性执行,而不管执行引擎如何。该模型由并发功能组成,称为内核,与流通道通信,这与软件开发人员如何在白板上绘制应用程序相关联。任何内核的内容都可以是任意的C/C ++代码,第三方IP,甚至是HDL代码。

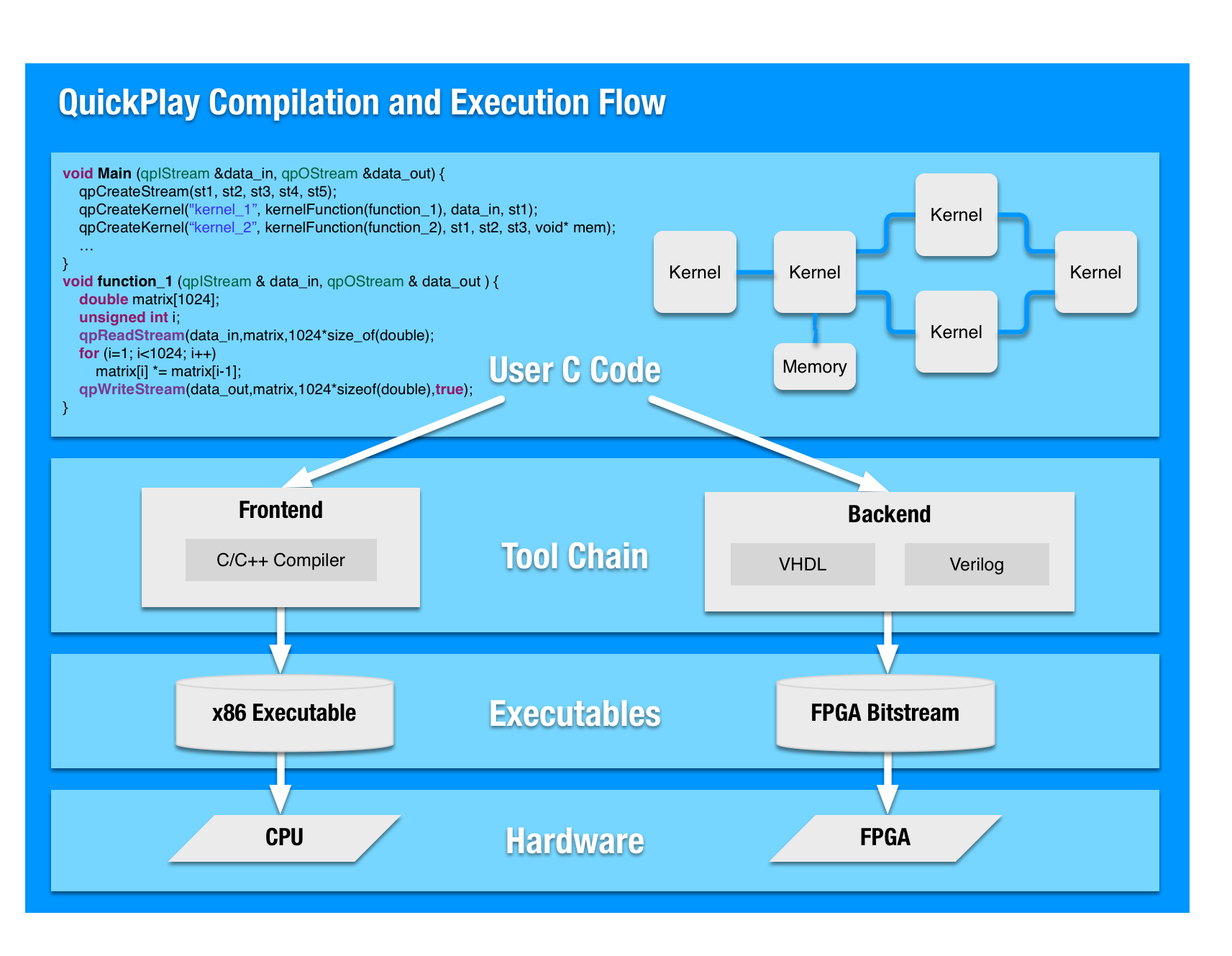

QuickPlay设计流程非常简单,如图3所示。

图3QuickPlay编译和执行流程

仔细研究设计流程

第1阶段:纯软件设计。 FPGA设计是通过在C中添加和连接内核,并使用开发软件指定通信通道来创建的。 QuickPlay IDE提供了一个C/C ++库和API来创建内核,流,流端口和内存端口,以及读取和写入流端口和内存端口。

第2阶段:功能验证确保软件模型正常工作。该模型在桌面上编译并使用测试程序执行,该测试程序将数据发送到输入,从而验证输出的正确性。

阶段3:然后从软件模型生成FPGA硬件。在此阶段,使用简单的下拉菜单选择目标FPGA平台和映射到设计输入和输出端口的物理接口。

阶段4:系统执行类似于功能验证,除了FPGA设计在选定的FPGA板上运行,而主机应用程序仍在软件中运行。实际数据可以流入和流出FPGA板。在此阶段可以运行比在功能验证期间更多的测试。

阶段5:系统调试。即使在硬件中执行功能后发现错误,也无需在硬件级别进行调试,因为QuickPlay可确保软件模型与硬件实现之间的功能等效。软件版本中也存在硬件版本中的任何错误。

阶段6 :(可选)优化。虽然QuickPlay构建的整个基础架构在性能和利用率方面都非常高效,但设计的整体质量将取决于用户创建的内核的质量。由于通用C代码不会产生最有效的硬件实现,因此软件开发人员可以遵循一些技术和指南来大大提高HLS生成代码的效率。进一步优化也可以通过使用Vivado HLS或在HDL中重新编码某些内核来完成。

摘要

这种简单的方法为大量软件工程师开放了基于FPGA的计算,他们现在可以使用熟悉的技术在软件中进行建模,然后构建系统和硬件测试。目前还没有其他工具采用这种方法,也没有提供软件工程师可以在源级别专门设计和调试的框架。

生成的硬件效率也使QuickPlay成为硬件工程师寻找的好工具通过让QuickPlay处理平凡的硬件设计任务来节省数周或数月的设计工作,同时他们专注于真正的增值:处理内核。

QuickPlay的数据流计算模型使其成为理想的选择大量的FPGA应用,无论是纯CPU协同处理,CPU采集数据的预处理还是后处理,还是仅涉及不涉及CPU的系统(网络,广播,视觉,医疗等应用)无线,HPC等。)

-

FPGA

+关注

关注

1600文章

21286浏览量

592898 -

PCB打样

+关注

关注

17文章

2965浏览量

21376 -

华强PCB

+关注

关注

8文章

1831浏览量

27455 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

42567

发布评论请先 登录

相关推荐

基于直方图算法进行FPGA架构设计

如何使用Verilog HDL进行FPGA设计

FPGA 等效门数的计算方法

FPGA 是如何分类的?FPGA的使用方法

基于FPGA的软件定义无线电参考设计

对FPGA进行系统设计的Xilinx软件使用方法

FPGA 开发经验与技巧—ORCAD 与 FPGA 软件协同设计

QuickPlay迅速构建基于 FPGA 的高效应用

FPGA通过开发软件和编程工具来对芯片进行开发

Xilinx 7系列FPGA管脚是如何定义的?

FPGA_ASIC-DSP和FPGA共用FLASH进行配置的方法

来自Digilent设计大赛的FPGA上的软件定义无线电

使用QuickPlay进行软件定义的FPGA计算 最新的FPGA设计方法

使用QuickPlay进行软件定义的FPGA计算 最新的FPGA设计方法

评论