逻辑电路

逻辑电路是一种离散信号的传递和处理,以二进制为原理、实现数字信号逻辑运算和操作的电路。分组合逻辑电路和时序逻辑电路。

前者由最基本的“与门”电路、“或门”电路和“非门”电路组成,其输出值仅依赖于其输入变量的当前值,与输入变量的过去值无关—即不具记忆和存储功能;后者也由上述基本逻辑门电路组成,但存在反馈回路—它的输出值不仅依赖于输入变量的当前值,也依赖于输入变量的过去值。

由于只分高、低电平,抗干扰力强,精度和保密性佳。广泛应用于计算机、数字控制、通信、自动化和仪表等方面。最基本的有与电路、或电路和非电路。

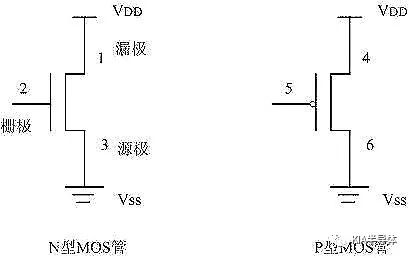

MOS管逻辑电路分析

MOS管构成的各种基本MOS管逻辑电路必须熟记于心,才能够更熟练的看懂芯片的框图。场效应管(Field-Effect Transistor)通过不同的搭配可以构成各种各样的门电路,如开篇所说,这些最基本的单元电路或许是现代IC的基础。

以下的电路形式在常用的74系列的芯片中大量存在着,之后介绍的OD门,缓冲器则常见于芯片的GPIO口等管脚的设计。

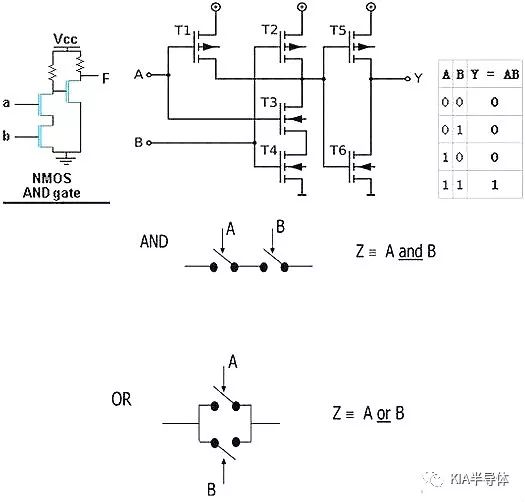

(一)MOS管构成的与门、或门电路

与门可以由六个管子构成,通过下面的示意图应该能更清楚看出与门的工作示意图,然后由真值表可以看出输入输出的对应关系。本文中给出与门的对应电路,如有兴趣,大家可以思考或门的电路结构,其实二者是存在对应关系的。

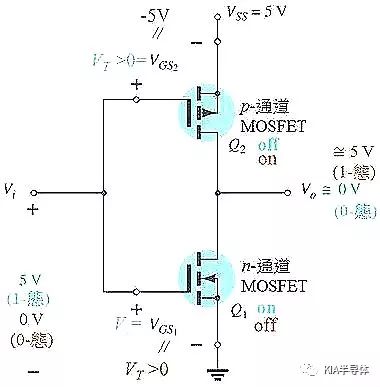

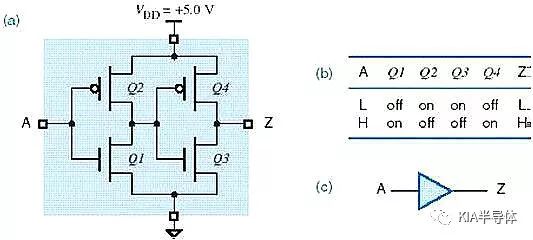

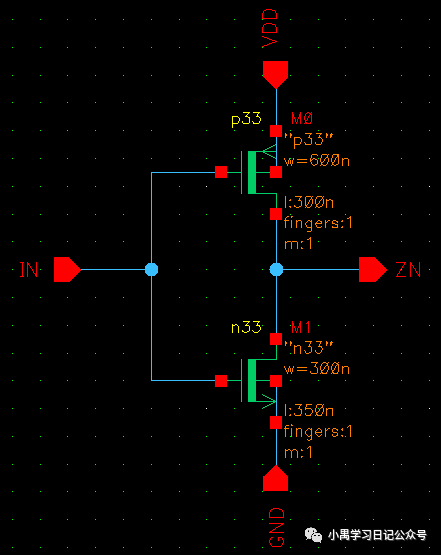

(二)反相器

下图则给出了反相器的电路图,输入和输出状态相反,谓之反相器。

电路分析:

输入Vi为低电平时,上管导通,下管截止,输出为高电平;输入Vi为高电平时,上管截止,下管导通,输出为低电平。

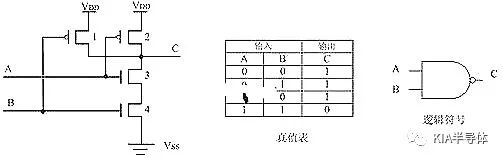

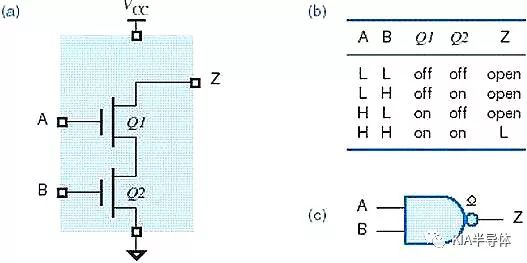

(三)与非门

下图则给出了与非门的电路图,与非门也就是同为零,异为一。

当A,B输入均为低电平时,1,2管导通,3,4管截止,C端电压与Vdd一致,输出高电平。当A输入高电平,B输入低电平,1,3管导通,2,4管截止,C端电位与1管的漏极保持一致,输出高电平。

当A输入低电平,B输入高电平,2,4导通,1,3管截止,C端电位与2管的漏极保持一致,输出高电平。当A,B输入均为高电平时,1,2管截止,3,4管导通,C端电压与地一致,输出低电平。

(四)缓冲器Buffer

CMOS缓冲器(buffer),缓冲器跟反相器是对立的,缓冲器输入与输出相同,反相器输入与输出相反。

电路分析:

前面一级Q1,Q2组成了一个反相器;后面一级Q3,Q4又构成了一个反相器,相当于反了两次相,于是又还原了。

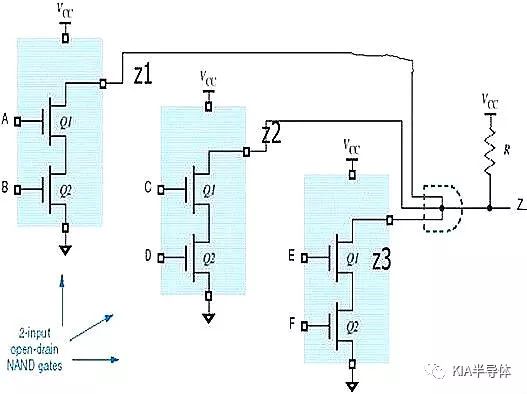

(五)漏极开路门

漏极开路门是一个十分经典常用的电路,常见于主芯片的GPIO口或者单片机的GPIO口的设计中。要最重要的一点就是:漏极开路是高阻态,一般应用需要接上拉电阻。

【漏极开路门的应用-线与逻辑】Z=z1z2z3

“线与”逻辑是因为多个逻辑单元的输出的三极管,共用一个上拉电阻,只要一个逻辑单元输出低电平,即集电极(漏极)开路输出的管子导通,那么输出低电平;

而只有全部单元截止,输出端被上拉电阻置为高电平,这是一个很实用的电路,可以用于逻辑仲裁等电路系统中。

组合逻辑电路分析方法

在asic设计和pld设计中组合逻辑电路设计的最简化是很重要的,在设计时常要求用最少的逻辑门或导线实现。

在asic设计和pld设计中需要处理大量的约束项,值为1或0的项却是有限的,提出组合逻辑电路设计的一种新方法。

与逻辑表示只有在决定事物结果的全部条件具备时,结果才发生的因果关系。输出变量为1的某个组合的所有因子的与表示输出变量为1的这个组合出现、所有输出变量为0的组合均不出现,因而可以表示输出变量为1的这个组合。

组合逻辑电路的分析分以下几个步骤:

(1)有给定的逻辑电路图,写出输出端的逻辑表达式;

(2)列出真值表;

(3)通过真值表概括出逻辑功能,看原电路是不是最理想,若不是,则对其进行改进。

-

逻辑电路

+关注

关注

13文章

468浏览量

42195 -

门电路

+关注

关注

7文章

191浏览量

39834

发布评论请先 登录

相关推荐

集成逻辑电路、组合逻辑电路

钟控传输门绝热逻辑电路和SRAM 的设计

MOS管的主要电路逻辑

逻辑电路的基础知识介绍

常见的组合逻辑电路分析

同步时序逻辑电路

硬件工程师必看的技能之MOS管构成的基本门逻辑电路

组合逻辑电路和时序逻辑电路的区别和联系

简要介绍MOS管构成的基本门逻辑电路的作用

简要介绍MOS管构成的基本门逻辑电路的作用

评论