在说明差分对布线重要性之前,首先了解影响传输线阻抗因素:走线线宽、线长、线厚、侧壁形状、阻焊层覆盖范围和传输线介质是明显的影响因素。而介电常数和介质厚度也会影响传输线阻抗精度,具体计算公式请参考信号完整性分析相关书籍。知道这些影响因素,可以帮助我们设计出好的走线,特别是在需要明确走线阻抗的时候,通过相关的软件来调整走线宽度和厚度等都可以完成固定阻抗的走线。

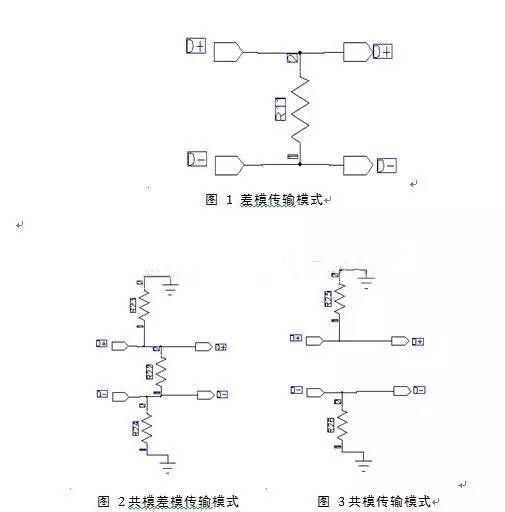

差分对,之所以是叫差分对,是因为它上面传送的信号等于两个互补并且彼此互为参考的信号之间的差值,因此可以极大地降低外部对其的干扰。

差分对的布线方式应该要适当的靠近且平行。所谓适当的靠近是因为这间距会影响到差分阻抗(differential impedance)的值,此值是设计差分对的重要参数。需要平行走线。

在电路设计中,如果所有的信号线都采用单端线,做好了阻抗设计,一般情况下系统是可以正常工作的,一旦信号线两端的地电位不同,甚至差距比较大,则会引起系统不能正常工作,而采用差分对布线或者走线是一种有效的解决方法。因为差分线具有等长,等阻抗,经过近似相同的环境,这在稳定信号上有着先天的优势。

在原理图设计中,差分信号通常以“_N”和“_P”作为后辍进行标记,差分线可以有效解决信号源和负载之间没有良好的参考地连,可抑制电子产品的干扰和减小信号线对外产生的电磁干扰(EMI)。

那么,为什么差分线能有效的消除噪声呢?首先我们看下在布差分线时的常规要求:差分线在设计时要保证两条线的长度相等,通常在5%之内。两条差分线之间有3w的距离和差分线周围包地都是很好的设计经验。

这样,一方面,差分线的两条信号线产生的磁场相互抵消,以此降低EMI;另一方面,差分对信号线假如同时引入外部噪声干扰信号,因为取其差分结果,这样可以很好的消去噪声,这与经典的三运放放大器有着异曲同工之妙。

在绘制PCB差分对的走线时,尽量在同一层进行布线,差分对走线换层会由于增加了过孔,会引入阻抗的不连续。

其次,若换层还会使回路电流没有一个好的低阻抗回路,会存在RF回路,若差分对较长,那么共模的RF能量就会产生影响了。

还有一个原因是差分对在不同板层之间有不同的信号传输速度,在信号完整性分析相关资料中都能看到信号在微带线上传输比带状线快,这也会引起一定的时间延时。

在连接方面,还要注意差分对的连接问题,如果负载不是直接负载而是有容性负载,那么可能会引入EMI。在电路设计方面也需要注意终端的阻抗匹配,防止发送反射而引入EMI问题。

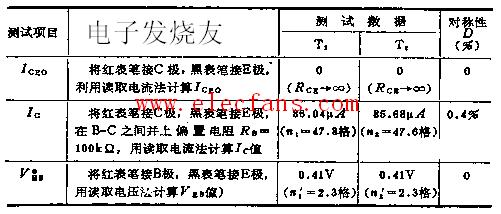

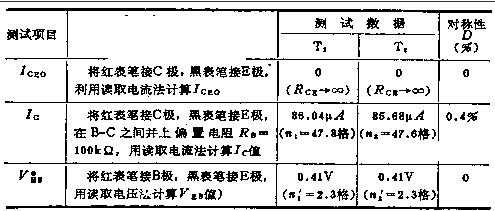

关于终端阻抗匹配,差分信号传输我们通常采用差模模式,还有一种传输模式是共模模式。其终端电阻配对参考设计如下所示

匹配电阻的大小通常用阻抗分析仪进行测量和标定。

对于我们常用的差模终端匹配电阻,通常选用50欧姆或者100欧姆进行,实际中也需要进一步的匹配。由于差模模式传输的信号是相互间的参考而与地无关,因此没有了共模的RF能量。也可以在设计初定为共模差模模式,在后期调试过程中采用不同的模式进行比较,这也不失为一种好方法。

-

电阻

+关注

关注

85文章

5037浏览量

169618 -

介电常数

+关注

关注

1文章

78浏览量

18159 -

差分对

+关注

关注

0文章

8浏览量

6771

发布评论请先 登录

相关推荐

探讨绘制性能良好的差分对的方法和步骤

探讨绘制性能良好的差分对的方法和步骤

评论