芯片制造商已经在基于 10nm 和/或 7nm finFET 准备他们的下一代技术了,但我们仍然还不清楚 finFET 还能坚持多长时间、用于高端设备的 10nm 和 7nm 节点还能延展多久以及接下来会如何。

在 5nm、3nm 以及更小节点,半导体行业还面临着巨大的不确定性和许多难题。即使在今天,随着每个节点的工艺复杂度和成本的上升,传统的芯片尺寸缩减也在放缓。因此,能够负担先进节点芯片设计的客户越来越少。

理论上,正如英特尔所定义的那样,finFET 有望延展到 5nm 节点。(一个完整延展的 5nm 工艺大致相当于代工厂的 3nm)。不管这些让人困惑的节点名称是啥,finFET 很可能将在 fin 宽度达到 5nm 时寿终正寝。所以在 5nm 或更先进的节点,芯片制造商将需要一种新的解决方案。否则传统的芯片缩放将会放缓或完全停滞。

一段时间以来,芯片制造商已经为 5nm 及以后节点探索了各种各样的晶体管。到目前为止,仅有三星提供过细节。在 5 月份,该公司推出了自己的技术路线图,其中包括在 2020 年之前实现一种 nanosheet FET。

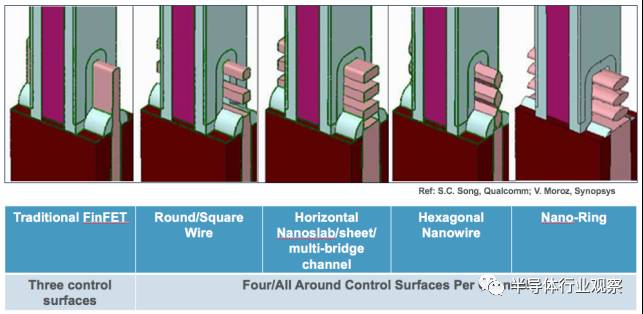

其它芯片制造商也倾向于同一时间框架内的相似结构,即使它们还没有公开宣布它们的意图计划。 nanosheet FET 和其它变体、nanowire FET 都是属于环绕栅极(gate-all-around)类别。其它变体还包括hexagonal FET、nano-ring FET 和 nanoslab FET。

图 1:水平式环绕栅极架构的类型,来源:高通、 Synopsys、Applied Materials

目前来看,环绕栅极技术似乎是 finFET 之后最实用的技术。这是 finFET 之后的一步进化,它们具有很多同样的工艺步骤和工具。有一种横向环绕栅极技术基本上就是一个被栅极包裹着的侧向 finFET。细小的线或片用作信道。

另外还有其它晶体管选项。一些芯片制造商甚至寻求使用先进的封装技术来进行扩展。供应商正在权衡各种选择以及寻求每种方法的技术价值和经济价值。“finFET 还能延展一两代,”英特尔一位资深研究员和工艺架构与集成总监 Mark Bohr 说,“但问题可能在于‘其中一种替代技术是更好的选择吗,它是否是环绕栅极的、III-V 族材料或隧道 FET?’如果我们不得不这样做,我们可以扩展 finFET。但问题在于‘还有更好的选择吗?’”

所谓的 III-V 族材料,Bohr 是指通道中使用 III-V 族材料的 finFET,这可以极大提升器件中的迁移率。隧道 FET(TFET)是一种陡峭次阈值斜率器件(steep sub-threshold slope device),可以在很低的电压下运行。

尽管环绕栅极技术气势正盛,但并不是每个人都会选择它——至少目前还没有。“我不一定赞同那一点,但它确实赢得了很多关注。”Bohr 在一次采访中表示,“现在就预测哪种技术会成功还为时尚早。但现在已经有足够多的好想法能确保还能再多续几代。”

但是,分析师相信 10nm/7nm finFET 还将在可预见的未来里持续。International Business Strategies(IBS)首席执行官 Handel Jones 说:“(finFET 提供了)更高性能、更低功耗和更低成本的组合。”

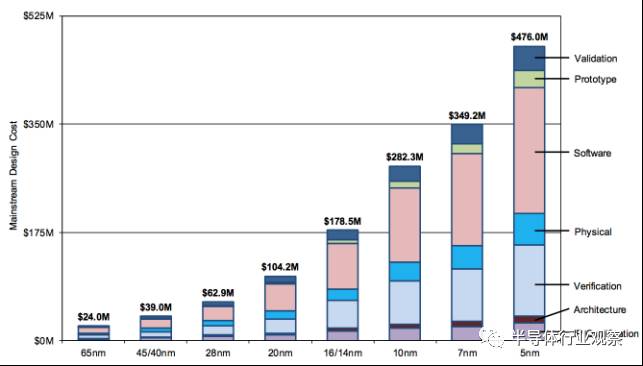

如果下一代晶体管在 5nm 或以后节点投入生产,那么这项技术将会非常昂贵且会受限于特定的应用。Jones 说:“很可能会采用环绕栅极,但主要的好处在于高性能。”据 IBS 报告称,在 5nm 节点将需要花费 4.76 亿美元来设计一款主流芯片,相较而言,在 7nm 节点为 3.492 亿美元,在 28nm 节点为 6290 万美元。

图 2:IC 设计成本,来自 IBS

为了帮助客户取得领先,Semiconductor Engineering 已经预先估计了未来的状况并突出强调了其中的难点工艺步骤。

不同的选择

未来至少有三条主要路径——暴力缩减尺寸、停留在成熟节点和先进封装。

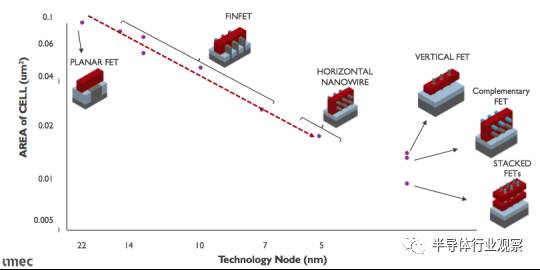

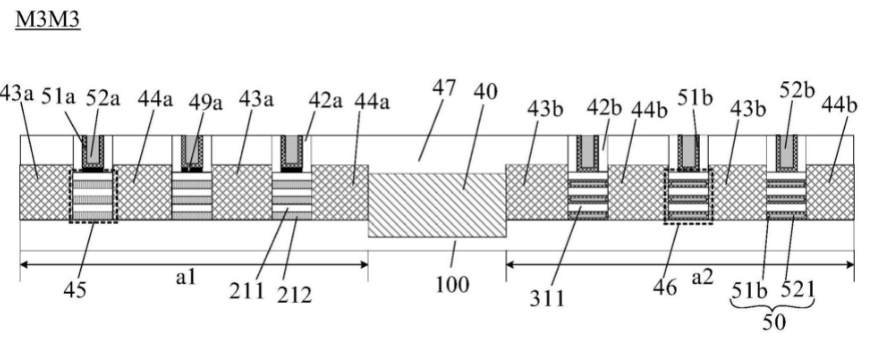

那些资金充足的公司很可能继续推进传统的尺寸缩减,实现 10/7nm 及以后节点。环绕栅极技术是 finFET 之后的领先者,至少目前来说是这样。更长期来看,还有其它选择,比如 III-V 族 finFET、互补式 FET(CFET)、TFET 和垂直纳米线(vertical nanowires)。垂直纳米线涉及到以垂直的方式对线进行堆叠。

CFET 是一种更加复杂的环绕栅极技术,其中 nFET 和 pFET 线堆叠在彼此之上。当前的环绕栅极器件只堆叠一种类型的线,不管是 nFET 还是 pFET。

CFET、TFET 和垂直纳米线是更具变革性的技术,预计在短期内无法实现。它们将需要新的突破。

图 3:后几代晶体管架构,来自 Imec/ISS.

所以高端玩家会怎么做?GlobalFoundries 首席技术官 Gary Patton 说:“7nm 将是一个长寿的节点。finFET 还有很长的路要走。finFET 仍然还有很大的扩展空间。”

在 finFET 之后,研发方面存在多种选择。比如 GlobalFoundries 正在探索纳米片、纳米线和垂直纳米线。

对于一项技术的决策和时机选择取决于各种技术和经济因素。“你要努力开发一种能够生产并能提供价值主张(value proposition)的工艺。”Patton 说,“这种事已经不如以往那样直观了。而需要远远更多的审查核验。”

事实上,一项技术可能会持续处于研发阶段十年之久。然后根据一系列指标,最好的技术上市,其它技术则为之崩猝。

但是可以确定,并非所有公司都会需要 finFET 和纳米线。大部分都会停留在 22nm 平面工艺或以上的节点。许多公司无力承担 finFET,而且模拟和射频等器件也不需要这种技术。

“10nm、7nm 和 5nm 听起来很诱人。”联华电子公司(UMC)业务管理副总裁Walter Ng 说,“但有多少公司能真正负担得起并且把设计和制造费用赚回来?只有少数几家才能真正做到需求推动前沿。”

但那些处于 22nm 及更高节点的公司也面临着一些挑战。“其它每家公司都需要了解它们可以怎样继续竞争。”Ng 说,“他们正在努力寻找一种实现差异化和压低成本的方式。”

所以很多公司转向了先进封装。所有芯片都需要 IC 封装,比如说,客户可以使用传统的封装,比如倒装 BGA。先进封装是这一思想的延展,在同一封装集成多个 die 以创造高性能系统。2.5D/3D 和 fan-out 是这类方法的代表。

所以这一市场的最终赢家会是谁?Coventor 首席技术官 David Fried 说:“还没有答案。人们确实还是寻找应用来推动实际的解决方案。”

Fired 指出并不存在一种适用于所有应用的解决方案。比如,finFET 或后续技术的晶体管可以用于高端微处理器。“但对于物联网设备,这可能是个错误方向。”他说,“不存在一种能够推动整个市场的单一应用。人们必须停止寻找一劳永逸的答案。很多不同的技术可以在同一时间都获得成功,但它们针对的是不同的应用。”

Fried 预测说:“我猜想 7nm 似乎是相当具有变革性的。将会是 finFET。如果我们看到变成了 finFET 之外的其它技术,那可能是在 5nm 节点了。但要记住,横向环绕栅极纳米线器件(lateral gate-all-around nanowire device)就像是使用了 2 次额外蚀刻的 finFET。从 finFET 到横向环绕栅极纳米线器件是相当变革性的。我希望我们能在 5nm 节点时开始看到它。除此之外,我们并没有太多可见性。”

晶体管趋势和工艺

现在 finFET 是前沿的晶体管技术。在 finFET 中,对电流的控制是通过在 fin 的三个侧面的每一个上实现一个栅极来实现的。

栅极间距(gate-pitch)是一个关键指标。英特尔 10nm finFET 技术的栅极间距是 54nm,14nm 技术的栅极间距是 70nm。(英特尔的 10nm 相当于代工厂的 7nm)。

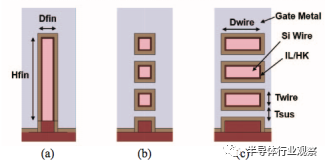

当栅极间距接近 40nm 时,就需要重大决策了。根据 Imec 的仿真,finFET 开始接近 42nm 栅极间距了。Imec 半导体技术和系统执行副总裁 An Steegen 说:“纳米线将会向下扩展并且仍然会有很好的静电控制。”据 Imec 介绍,纳米线 FET 已经在 36nm 栅极间距上表现出了很好的静电控制能力。Imec 也已经设计出了一种直径低至 9nm 的纳米线。

图 4:Imec 的微型纳米线,来自 Imec

一般而言,环绕栅极可以提供比 finFET 更好的性能,但也存在一些难题,即驱动电流和寄生电容。将这些问题结合到一起的是一个相对新的层,被称为 middle-of-line(MOL)。MOL 使用一系列接触式结构将分离的晶体管和互连件连接起来。在 MOL 中,寄生电容是个问题。它会给器件的各个部分带来外部电阻。这包括与低电阻肖特基势垒和硅化物所在的结(junction)的接触。

有一种版本是横向纳米线 FET,其中你是将一个 finFET 切成碎片,每一个碎片都变成一个微小的水平纳米线,用作源极和漏极之间的通道。

其它常见变体还包括纳米片(nanosheet)或纳米板(nanoslab)FET。这两种技术都类似于横向纳米线 FET,但线要宽和厚很多。

每一种变体都有各自的优势劣势。英特尔的 Bohr 说:“(纳米片 FET)并不如听起来那样具有变革性。它只是侧向放置的 finFET。不确定它是否有纳米线那样高的价值。”

在纳米线 FET 中,环绕栅极整条线,可以实现对栅极的更好控制。Applied Materials 晶体管与互连组高级总监 Mike Chudzik 说:“正是这种改进过的栅极控制,使得你可以继续延展栅极长度。”

正如前面说的那样,finFET 被切割成了碎片。因此,器件上的表面积会减少。Chudzik 说:“你正在失去硅本身的红利。我很肯定你能在截止电流上获得好处,但在整体驱动电流上会出现缺憾。”

所以纳米片 FET 也是合理的。他解释说:“这就是你开始延长这些线的地方。你要获得更大的驱动电流。此外,你也可以调整这些线或片的形状来帮助降低电容。”

另一个被称为 nano-ring FET 的版本也有类似的优势。他说:“nano-ring 的整个思想实际上就是将片稍微挤压到一起,这么做能够有效地降低电容。”

第一款环绕栅极器件很可能将有三根线。但随着时间的推进,芯片制造商将需要堆叠更多的线以提供更多性能。他说:“我们肯定不想引入一种只能持续一个节点的新器件架构。(所以我们的想法)是考虑堆叠更多纳米板。但你不能只是不断无限地堆叠通道,因为你会遇到大量同样的寄生、电容和阻抗问题,正如你会在更高的 finFET 中遇到的那样。”

作为未来的预兆,GlobalFoundries、IBM 和三星最近发表了一篇关于 5nm 和 3nm 节点纳米片 FET 的论文;称这项技术相比于 finFET,能在更小的 footprint 上得到更好的性能。

图 5:(a) finFET、(b) 纳米线 (c) 纳米片的横截面仿真图,来自 IBM

对一些层使用极紫外(EUV)光刻技术,来自这三家公司的纳米片 FET 有三个片或线。它有 12nm 的栅极长度、使用 5nm 硅通道的 44nm/48nm 接触的 poly pitch。据该论文称,nFET 有 75mV/decade 的亚阈值斜率(sub-threshold slope),而 pFET 的则为 85mV/decade。

在实验室中,研究者堆叠了 3 层纳米片,每一片厚度为 5nm,中间有 10nm 的间隔。他们使用片宽度为 15nm 到 45nm 的单堆叠纳米片结构演示了逆变器和 SRAM。该论文称:“相比于具有继承于 finFET 的多个阈值和隔离解决方案的 extremely scaled finFET,它有更好的静电性能和动态性能。所有这些优势使得堆叠的纳米片器件成为了一种非常有吸引力的 finFET 替代选择,而且可以扩展到 5nm 及以后的器件节点,在图案化策略方面的复杂度也更低。”

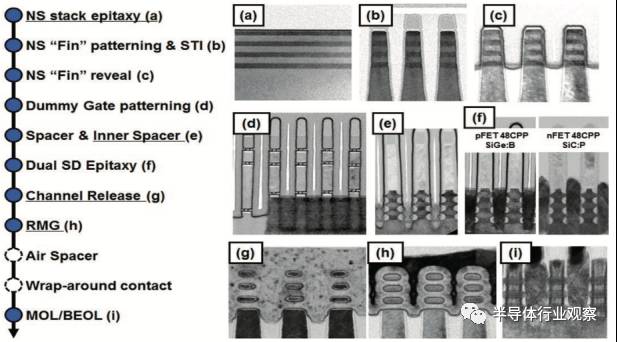

图 6:堆叠的纳米片工艺序列和 TEM,来自 IBM、Samsung、GlobalFoundries.

一般而言,环绕栅极和 finFET 的工艺步骤是类似的,只有一些例外。但这些例外使得环绕栅极技术具有了很大的挑战性。图案化、缺陷控制和变异性是其中的一些问题。

环绕栅极的第一步就不同于 finFET。在环绕栅极中,目标是使用一个外延反应器(epitaxial reactor)在基底上构建一个超晶格结构。这个超晶格由交替的硅锗(SiGe)层和硅层构成。理想情况下,一个堆叠由 3 层 SiGe 和 3 层硅构成。

然后,就像 finFET 流程一样,下一步涉及到浅沟槽隔离的形成。Applied Materials 的 Chudzik 说:“这个超晶格在硅锗和硅之间有 ultra-abrupt 结是至关重要的。”

接下来是下一个关键步骤。在环绕栅极中,栅极不仅会围绕通道,而且还会围绕一些接触区域。这会增加这个混合结构的电容。Chudzik 说:“所以你需要形成所谓的 inner spacer,这里你实际上是将高 k 区域和源极-漏极区域隔开。这可以通过 ALD 类型的薄膜完成。”

然后,使用一种替换工艺从这个超晶格结构中移除 SiGe 层。这会留下硅层和它们之间的间隔。每一个硅层都是纳米线的基础。

掩模/光刻难题

在这个工艺流程中,还有一系列光刻步骤。在 16nm/14nm 和 10nm/7nm 节点,芯片制造商使用的是今天的 193nm 浸没式光刻工具和多重图案化。

在 7nm 和/或 5nm 节点,半导体行业希望加入 EUV。在 EUV 中,电源将等离子体转换成13.5nm 波长的光,从而在芯片上实现更精细的特征。

芯片制造商希望为最困难的部分加入 EUV,即 metal1 和通孔。在其它许多步骤,还将继续使用传统的光刻技术。

据 ASML 报道,与三重图案化相比,EUV 可以将金属线的成本降低 9%,将通孔的成本降低 28%。ASML 产品营销总监 Michael Lercel 说:“(EUV)可以消除晶圆厂的步骤。如果考虑执行多次浸没式光刻步骤的成本,再加上其他工艺步骤(如清洁和计量)的成本,我们相信相比于三重图案化浸没式和肯定的四重图案化等等,EUV 每层的成本更低。”

但目前 EUV 还不足以用于生产。ASML 正在准备其最新的 EUV 扫描机 NXE:3400B。起初这款工具配置了一个 140W 的电源,可以实现 100 片晶圆/每小时(wph)的吞吐量。

为了将 EUV 投入生产,芯片制造商需要 250W 的功率,实现 125 wph 的吞吐量。ASML 最近已经开发出了一款 250W 电源,将在明年年初出货。

与此同时,EUV 抗蚀剂是另一个绊脚石。为了让 EUV 达到所需的吞吐量,行业需要 20mJ/cm² 剂量的抗蚀剂。“好的成像似乎需要更多,现在达到了 30mJ/cm² 到 40mJ/cm² 的范围。”Lam Research 技术管理总监 Richard Wise 说,“所以为了我们希望达到的目标,剂量不是必需的。”

比如,据分析师称,在 30mJ/cm² 剂量下,250W 电源的 EUV 扫描机的吞吐量是 90 wph,这低于所需的 125wph 目标。

但是开发所需剂量的抗蚀剂难度很大。Wise 说:“要降低剂量,存在大量的基础物理难题,因为 EUV 存在随机效应。”

这涉及到一种被称为光子散粒噪声(photon shot noise)的现象。光子是光的基本粒子。在图案化的过程中,光子数量的变化会影响 EUV 抗蚀剂。它可能导致出现我们不想要的线边缘粗糙度(LER)——LER 的定义是理想形状上特征边缘的偏差。

在行业攻坚抗蚀剂的同时,光掩模制造商也正在开发 EUV 掩模。今天的光掩模由一个在玻璃基底上的不透明铬层组成。而 EUV 掩模则是一种反射技术,由基底上交替的硅层和钼层组成。

“我们需要 EUV 来避开三重图案化。”D2S 首席执行官 Aki Fujimura,“这意味着 EUV 掩模将会有比 ArF 掩模多很多的主特征,而且其中每一个特征都会很小。由于 EUV 能更准确地反映晶圆上的掩模偏差,所以 EUV 掩模需要印刷更多更小的结构,且每一个都要更准确。”

要生产 EUV 掩模,光掩模制造商还需要一些新工具。比如他们需要更快的电子束掩模写入器。随着掩模特征越来越复杂,今天的单束电子束工具需要更长的时间来图案化或写入掩模。今天的电子束基于可变形束(VSB)技术。

这个问题的解决方案是多束掩模写入器,今天已有 IMS 在提供多束掩模写入器了,可用于光掩模和 EUV 掩模,而 NuFlare 也正在开发多束工具。

多束有助于改善掩模产量、周转时间和成本。Fujimura 说:“世界上大多数掩模仍然可以完美地使用 VSB 写入器制造,但关键的少数将需要多束写入,从而保证合理的写入时间。”

他说:“最可能的情况是 EUV 将在 5nm 节点时就绪,一些掩模层将会有很高的多束写入需求。比如,如果一个掩模层包含大量非正交、非 45 度的特征,那么肯定会需要多束。193i 无法看到掩模上的小扰动,所以在有相对大的步进大小时,这些图案的‘曼哈顿化(Manhattanization)’效果良好。但是 EUV 可以做到更好,这会极大地增加发射数量,使得 VSB 写入不太可能实现。但这些是针对特定芯片的非常专门的掩模。对于绝大多数掩模层,尽管掩模上的主特征的数量会倍数式地暴增,但用来描绘装饰图案和 SRAF 的发射的数量却将大幅减少。具有足够精度的先进 VSB 写入器可能足以用于大多数 EUV 掩模了。”

检测/计量难题

在 5nm 及以后节点,检测和计量也是一大关键。“向垂直架构发展的趋势带来了缺陷隐藏的检测难题和描述复杂的计量难题。”KLA-Tencor 客户参与高级总监 Neeraj Khanna 说,“在这些节点,EUV 会被大量采用,这会推动新的随机和系统性的缺陷机制。随机问题将会带来对更高采样率的需求。”

这意味着什么?Khanna 说:“我们预计这些新架构会带来对检测和计量的新需求。这个行业必须不断创新和拓展核心技术。”

-

芯片

+关注

关注

446文章

47769浏览量

409067 -

集成电路

+关注

关注

5320文章

10725浏览量

353315 -

晶体管

+关注

关注

76文章

9053浏览量

135172

发布评论请先 登录

相关推荐

专用集成电路 通用集成电路有哪些

通用集成电路和专用集成电路按什么分类

集成电路芯片有哪些

集成电路跟芯片是一个概念吗?集成电路和芯片区别?

集成电路芯片的基本概念 集成电路材料与器件 集成电路介绍

集成电路的核心是什么?集成电路有哪些器件?

集成电路分为几类?集成电路的应用领域分析

华为公开“集成电路及其制作方法、场效应晶体管”专利

关于FinFET与集成电路的对比分析介绍

关于FinFET与集成电路的对比分析介绍

评论