半导体行业观察:极紫外(EUV)光刻技术正蓄势待发,但为了将这项人们期待已久的技术用于大规模生产,还仍然有一些难题有待解决。

EUV 光刻是在芯片上图案化微小特征的下一代技术,原本预期在 2012 年左右投入生产。但这么多年过去了,EUV 不断延后,从一个节点拖到了下一个节点。

如今,GlobalFoundries、英特尔、三星和台积电都在竞相要在 7nm 和/或 5nm 节点时将 EUV 光刻用于大规模制造(HVM);根据供应商的不同,时间规划在 2018 年到 2020 年之间。此外,美光、三星和 SK 海力士还希望将 EUV 用于生产十几纳米的 DRAM。

但和之前的技术一样,要将 EUV 投入大规模制造,有一些问题还要解决。芯片制造商还必须权衡各种复杂的利弊关系。

基于行业最新的数据,这里简单给出了当今 EUV 所处的状态以及其中的一些权衡:

ASML 正在装配其第一款具有生产价值的 EUV 扫描仪,其中使用了人们等待已久的 250W 光源,计划将在今年年底前完成。但是,EUV 真正投入大规模应用的时间还不能确定。

抗蚀剂是指暴露在光中时可在表面形成图案的材料。目前抗蚀剂还不能达到 EUV 的目标规格。虽然这个规格可以降低,但吞吐量会受到打击。而且有时候与抗蚀剂的相互作用会导致工艺发生变化甚至图案化失败。

EUV 防护膜(pellicle)是掩模基础设施的一个关键部分,目前还没有为大规模制造做好准备。防护膜是指防止颗粒落在掩模上的薄膜。所以芯片制造商可能要么需要等待 EUV 防护膜,要么就得不使用防护膜就投入生产——至少在初期可以这么做。

尽管如此,即使这些问题没有解决,芯片制造商也还是可以在 7nm 节点时应用 EUV 光刻。非要使用的话,EUV 也可以用在一两层上的制造上。但在 5nm 及以后节点,EUV 还不满足这些节点的更严格的规格,也就是说半导体行业还是必须要投入更多时间和金钱来解决这些问题。

“我们离在大规模制造中实现 EUV 的目标越来越近,”Stifel Nicolaus 的分析师Patrick Ho 说,“还有一些事情需要解决,而且客户使用 EUV 处理的层的数量也各不相同。英特尔更保守。三星则更大胆,因为他们也想将其用于 DRAM 和代工/逻辑业务。我相信台积电的 5nm 节点将实现完全的大规模制造,时间上可能是在 2020-2021 年。”

很显然,代工客户需要在 EUV 发展曲线上保持领先。为了帮助半导体行业了解情况,Semiconductor Engineering 在本文中对这项技术进行了解读,并分析了EUV 的三大主要部件上的利弊权衡——扫描仪/源、抗蚀剂和掩模基础设施。

为什么要用 EUV?

目前,芯片制造商使用 193nm 波长的光刻技术在晶圆上描绘精细的图案。但实际上,193nm 浸没式光刻在 80nm 间距(40nm 半间距)达到了极限。

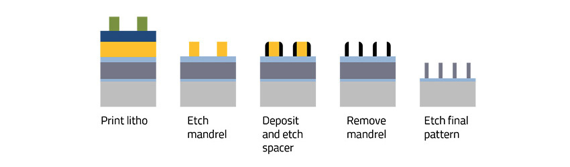

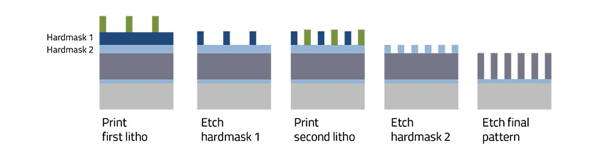

因此,从 22nm/20nm 开始,芯片制造商开始在使用 193nm 浸没式光刻的同时配合使用各种多重图案化(multiple patterning)技术。多重图案化是一种在晶圆厂中使用多个光刻、蚀刻和沉积步骤的工艺,其目标是为了将间距减小到 40nm 以下。

图 1:自对准衬垫料可以避免掩模不对准的问题,来自 Lam Research

图 2:双重图案化可以增加密度,来自Lam Research

多重图案化是有效的,但步骤更多,因此会增加流程的成本和周期时间(cycle time)。周期时间是指晶圆厂加工一块晶圆从开始到结束的总时间。

为了解决这些问题,芯片制造商需要 EUV。但因为 EUV 在 7nm 节点时还无法进入初始应用阶段,所以芯片制造商首先将使用浸没式/多重图案化。人们希望在 7nm 后期能够用上 EUV。而 5nm 节点就必须使用 EUV 了。

“从光学上看 7nm 节点就可以实用了,但可能在成本方面并不理想。”D2S 首席执行官Aki Fujimura 说,“行业希望随着 7nm 产量的攀升,能够在同样的设计规则上使用 EUV。而从实际的角度来看,如果没有 EUV,5nm 将无法实现。”

EUV 最初是针对 7nm 节点的触点和通孔设计的。据GlobalFoundries 称,为了加工触点/通孔,7nm 节点的每个光刻层都需要 2 到 4 个掩模。

而如果使用 EUV,那么每层就只需要 1 个掩模来加工触点/通孔即可,而且 7nm 和 5nm 节点都是这样。据 ASML 称,理论上 EUV 能简化流程,并且可将晶圆上的周期时间减少大约 30 天。

GlobalFoundries 首席技术官 GaryPatton 说:“这是一个非常好的权衡,因为你把触点的四重图案化或三重图案化换成了一个掩模。这也不会影响到任何设计规则,所以客户能够在周期时间上取得优势,从而得到更好的产量。当 EUV 技术成型之后,我们将会将其过渡到我们做 metal level 和 shrink 的地方。”

所以 EUV 在 7nm 节点是可行的,有人甚至认为使用单重图案化就可以。但在 5nm 节点,规格要求更严格,特征尺寸变得更小。为此芯片制造商需要使用多重图案化的 EUV,这将是最复杂最昂贵的工艺。

早期采用 EUV 的公司希望在 2019 年到 2020 年左右将 EUV 用于 7nm 节点。“这差不多就是工作的中心。我们正努力更加进取。”GlobalFoundries 高级研究员和高级技术研究总监 Harry Levinson 表示,“四大主要芯片公司的 HVM 都规划在未来一两年。现在真正的问题是谁会成为第一,谁又将是第二。”

光源问题

但在此之前,芯片制造商必须首先将 EUV 投入大规模制造(HVM)。事实已经证明,这比之前预想的还更加困难,因为 EUV 光刻复杂得让人难以置信。

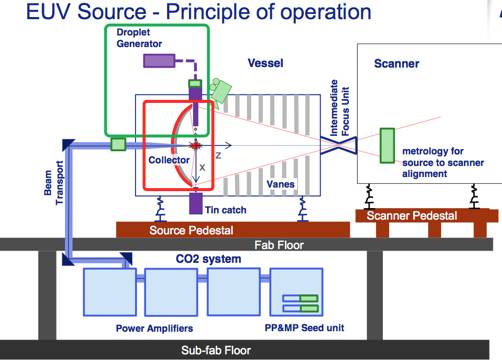

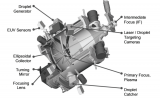

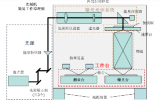

图 3:EUV 的复杂性,来自ASML

在 EUV 中,光源会将等离子体转换成波长 13.5nm 的光。然后,这些光会在一种包含 10 个多层镜面的复杂配置方案中反射。

然后这些光会经过一个可编程的illuminator 并抵达掩模。在这里,光还会在另外 6 个多层镜面上反射并以 6% 的角度抵达晶圆。

图 4:准确反射的光,来自ASML/Carl Zeiss SMT Gmbh

光源是个大难题。它需要足够大的功率来生成 EUV 光,从而让 EUV 扫描仪足够快地运行并在经济上可行。

要将 EUV 投入大规模制造,芯片制造商需要能产生 250W 光源功率的 EUV 扫描仪。这能带来 125 wph(每小时晶圆数量)的吞吐量。

实现这些目标所需的时间超过预想。不久之前,光源还只有 10W 功率。现在,ASML 的光源功率已经从 80W 提升到了 125 W,让 EUV 的吞吐量从 60 wph 提升到了 85 wph。

现在 ASML 已经准备开始生产自己的第一款 EUV 扫描仪了,即NXE:3400B。该工具的数值孔径为 0.33,分辨率为 13nm。 ASML 高级产品经理 Roderik van Es 说:“看看这个系统的成像性能,我们已经实现了 13nm LS 和 16nm IS。”(LS 表示线和空间,IS 表示隔离线。)

该工具一开始时将装载一个 140W 的光源,可实现 100 wph 的吞吐量。ASML 最近已经演示了一款 250W 光源。据 Es 说,这个 250W 光源的工业版本将在年底前发布。

但就算有了 250W 光源,光刻师还是会担忧这个系统能持续工作多长时间。今天的 193nm 扫描仪可以以 250 wph 或更快的速度不停止地运行。相比而言,目前预生产的 EUV 机器的上线工作时间只能占到 70% 到 80%。

“可用性,即工具下线维护前的时间长度,仍然让人有些担忧,尤其是对英特尔而言。”Stifel Nicolaus 的Ho 说,“像英特尔这样的公司无法接受 70% 甚至 80% 的可用性,它们需要百分之九十几的可用性指标。”

但是,NXE:3400B 在这一领域的表现如何还有待观察。如果上线运转的时间仍然还有问题,光刻师可能会因为冗余的时间而考虑购买其它工具。

当然,这是芯片制造商希望避免的昂贵选择。分析师表示,每台 EUV 扫描仪的售价大约为 1.25 亿美元,相比而言,现在的 193nm 浸没式扫描仪的售价为每台 7000 万美元。

抗蚀剂问题

多年以来,EUV 的头号难题都是光源问题。但现在,头号难题的位置正从光源转向涉及抗蚀剂的工艺。

EUV 抗蚀剂分为两大类:化学增强型抗蚀剂(CAR)和金属氧化物抗蚀剂。CAR已经在行业内应用了很多年,是一种基于扩散的工艺。较新的金属氧化物抗蚀剂则基于氧化锡化合物。

抗蚀剂的选择涉及到三个指标的权衡,这被称为 RLS 三角——分辨率(R)、线边缘粗糙度(LER)和灵敏度(S)。

为了达到所需的分辨率,芯片制造商需要灵敏度或剂量为20mJ/cm²的 EUV 抗蚀剂。这些抗蚀剂已经有了,但是要将其投入大规模制造,难度却比之前预想的更大。

GlobalFoundries 的 Levinson 说:“在 32nm 及以下节点,什么都没用——不管是 CAR 还是金属氧化物,不管剂量如何,至少在合理范围(<100mJ/cm²)内是这样。”

但业界已经开发出了30mJ/cm²和 40mJ/cm²的 EUV 抗蚀剂。基于 RLS 三角原则,抗蚀剂剂量越高,分辨率就越高。但它们的速度更慢,会影响 EUV 的吞吐量。

据 ASML 的数据,在不使用防护膜,使用30mJ/cm²剂量时,带有 250W 光源的 EUV 扫描仪的吞吐量大约为104-105 wph,低于 125 wph 的目标。

“已有的 EUV 抗蚀剂可以支持 7nm HVM,但特征尺寸更小时就难以为继了。”Levinson 说,“因为在研发低剂量抗蚀剂上耗费了太多时间,下一个节点可能存在风险。”

这是根据花在开发20mJ/cm²抗蚀剂上的时间和资本而得到的结论。半导体行业正在开发这种抗蚀剂,目标是用于 5nm 节点。

抗蚀剂难题道阻且长。Lam Research 技术总监 Richard Wise 在最近一场活动中说:“剂量不一定需要达到我们想要的目标。由于 EUV 的随机性效应,在降低剂量上还面临着很多基础的物理难题。”

随机性就是指随机的变化。“光是由光子构成的。曝光少量抗蚀剂的光子的数量的平均值对应于所需的曝光剂量。”Fractilia 首席技术官 Chris Mack 解释说,“但这个平均值会随机改变。如果曝光一定量抗蚀剂的光子数量过高,那么相对的随机变化就会很小。但当曝光少量抗蚀剂的光子数量变小时,相对的随机变化就会变大。”

这个效应被称为光子散粒噪声。散粒噪声是指在光刻工艺中光子数量的变化。

所有类型的光刻技术都有随机性之苦,EUV 尤甚。Mack 说:“首先,EUV 光子携带的能量比 193nm 光子多 14 倍。所以对于同样的曝光剂量,光子数少 14 倍。其次,我们正在努力通过使用低曝光剂量让我们的 EUV 扫描仪的吞吐量更高。这也意味着光子更少。光子越少,光子的随机不确定性即散粒噪声就越大。”

光子数量的变化会带来问题。TEL 资深技术员Ben Rathsack 说:“我们有更高能量的光子,但数量不够。所以我们在图案中有线宽粗糙度和线边缘粗糙度。”(LER 的定义是特征边缘与理想形状的偏差。)

如果光子数量不够,变化还可能导致其它问题。Imec 先进图案化部门主管Gregory McIntyre 说:“在成像方面,我们所说的第一难题是纳米桥接、线断开和融合或缺失孔等地方的极端粗糙度事件或随机故障。”

所以在 EUV 曝光工艺中,扫描仪可能有时候无法处理某个线、空或触点。或者该过程可能会导致线断开或触点融合。

防护膜问题

除了抗蚀剂之外还有其它问题,即所谓的 EUV 光掩模基础设施。光掩模是给定 IC 设计的主模板。在开发出一个掩模之后,就要将其送到晶圆厂。该掩模会被放置在光刻工具中。这个工具让光穿过这个掩模,从而在晶圆上投射出图案。

半导体行业多年来一直都在制造 EUV 掩模,但这项工艺仍然很有难度。KLA-Tencor 标线板产品部总经理 Weston Sousa 说:“掩模行业正在加大力度开发 EUV 标线板。在图案缺陷和修复上难题还有很多,从坯料质量到特征尺寸均匀性。”

成本和产量也存在问题。GlobalFoundries 的 Patton 说:“我担心的是掩模。掩模本身有缺陷,在生产制造时也会给掩模带来缺陷。”

eBeam Initiative 最近一项调查的数据表明掩模的整体产率处在健康的 94.8%,但 EUV 掩模产率仅有 64.3% 左右。

随着节点的演进,掩模缺陷也越来越小,更难以找到。英特尔的专供光掩模部门Intel Mask Operation 的掩模技术总监 JeffFarnsworth 说:“在周期早期,缺陷标准更加宽松。随着向 HVM 层面推进,标准会越来越严格。HVM 层面的标准肯定不宽松。”

此外,据三星一位研究者 Heebom Kim 称,EUV 掩模比复杂光学掩模还贵八倍之多。但据ASML 称,随着 EUV 投入大规模制造,EUV 掩模的成本可能会下降至比光学掩模贵不足三倍的水平。

光学掩模和 EUV 掩模是不同的。在光学掩模中,掩模坯料由玻璃基板上的不透明铬层组成。

相比而言,EUV 掩模坯料则由基板上 40 到 50 层交替的硅和钼层组成。在光学掩模和 EUV 掩模中,掩模坯料都会进行图案化,从而形成光掩模。”

掩模生产商希望实现两个目标。一是生产无缺陷的 EUV 掩模,二是防止缺陷出现在掩模上。因为来自扫描仪或其它工艺的颗粒物可能会无意中落在掩模上。

如果 EUV 扫描仪在曝光阶段给掩模引入了缺陷,那么它们可能就会出现在晶圆上,进而影响芯片产量。

总体而言,掩模生产商正在生产无缺陷掩模上大步迈进。而防止颗粒物落在掩模上是一个不同的问题,这涉及到掩模基础设施中的一个关键部件:防护膜(pellicle)。防护膜可用作掩模的防尘罩。

图 5:开发出的原型防护膜,来自ASML

不久之前,半导体行业还坚持认为 EUV 扫描仪可以不使用防护膜,只需要在洁净的环境中就可以加工晶圆。之后芯片制造商改变了自己的看法,表示无法保证 EUV 扫描仪或其它工具能在流程中保持百分之分的洁净。芯片制造商说如果没有防护膜,EUV 就很容易受到颗粒物污染,进而产生缺陷。

所以业界开始开发 EUV 防护膜。光学掩模的防护膜基于薄聚合物材料。而 EUV 防护膜的唯一供应商 ASML 则开发了一种基于多晶硅的 EUV 防护膜,其厚度仅有 50nm。

在实际工作过程中,当 EUV 光击中防护膜时,膜的温度会上升到 600 到 1000 摄氏度之间。

问题是这种防护膜很脆。在这样的温度下,有人担心这种 EUV 防护膜会在加工过程中退化,导致 EUV 掩模和扫描仪损坏。

到目前为止,ASML 的 EUV 防护膜已经过了 140W EUV 光源测试。但这种防护膜在 250W 功率下的反应还未可知。

“从机械强度和应用性上看,EUV 防护膜还面临着一些挑战。”Applied Materials 掩模和 TSV 蚀刻部门首席技术员兼 CTO Banqiu Wu 说,“防护膜会吸收一些 EUV 能量。这些能量将会导致防护膜温度升高。防护膜也处在真空环境中,这意味着自然对流冷却速度非常低。又因为防护膜很薄,天然的热转移也非常困难。”

总而言之,在 HVM 中使用基于多晶硅的防护膜还存在一些不确定性,甚至有人对此仍有怀疑。所以目前半导体行业正在进行调整并在考虑两个选择:等待一种支持 HVM 的防护膜或不使用防护膜就开始生产。

比如英特尔就已经声明不会在没有防护膜时投入 EUV 生产。英特尔的 Farnsworth 说:“我们正在积极进取。”

但是也有公司押注其它选择。很多公司正在考虑在没有防护膜时就开始 EUV 生产,至少可以在初期这么做。

理论上,使用 EUV 的芯片制造商可以在没有防护膜时加工触点和通孔。GlobalFoundries 的 Patton 说:“这些事情不需要防护膜,因为关键区域更小了,所以颗粒物带来问题的风险也更少了。”

但是,这也可能会产生一些不好的后果。即使 EUV 扫描仪是洁净的,我们不想要的颗粒物也会落在掩模上。

所以如果芯片制造商在没有防护膜时就投入生产,它们就必须在流程中实施更多掩模检查和清洁步骤。GlobalFoundries 的Levinson 说:“我们将不得不做一些关于晶圆印制和晶圆检查的事。但这些事很让人痛苦,所以我们需要一种优良的防护膜方案。”

在研发方面,半导体行业正在研发下一代防护膜和掩模基础设施的其它部分。可以肯定的是,EUV 抗蚀剂的开发方面也有紧迫感。当然,光源方面也是如此。

这些问题会一同得到解决吗?在 EUV 光刻正在进行的这个传奇故事里,时间会告诉我们答案。

-

芯片

+关注

关注

446文章

47769浏览量

409067 -

半导体

+关注

关注

327文章

24494浏览量

202057 -

EUV

+关注

关注

8文章

576浏览量

85578

发布评论请先 登录

相关推荐

ASML 首台新款 EUV 光刻机 Twinscan NXE:3800E 完成安装

什么是EUV光刻?EUV与DUV光刻的区别

日本的EUV***引进之路

EUV光刻胶开发面临哪些挑战?

EUV光刻DDR5内存狂飙 单条1TB不是梦

EUV***市场:增长趋势、竞争格局与前景展望

ASML的EUV***研发历程

一文解析EUV掩模版缺陷分类、检测、补偿

什么是EUV***?

EUV光刻技术优势及挑战

关于EUV光刻的优势和应用以及所面临的的困境

关于EUV光刻的优势和应用以及所面临的的困境

评论