集赛灵思多年投资和35年架构之大成,基于7nm工艺,多核异构且能灵活改变,面向所有开发者和各种应用的Versal 宣布发货了!

刚刚,自适应和智能计算的全球领先企业赛灵思公司(Xilinx, Inc.,(NASDAQ:XLNX))宣布已开始面向参与公司“早期试用计划”的多家一线客户交付 Versal™ AI Core 和 Versal Prime 系列器件。Versal 是业界首款自适应计算加速平台(ACAP),这是一款具有革命性意义的新型异构计算器件,其功能远超传统的 CPU、GPU 和 FPGA。

ACAP 是一种高度集成的多核异构计算平台,可在软硬件两个层面随时进行更改,从而动态地适应数据中心、汽车、5G 无线、有线以及国防市场的广泛应用与工作负载需求。

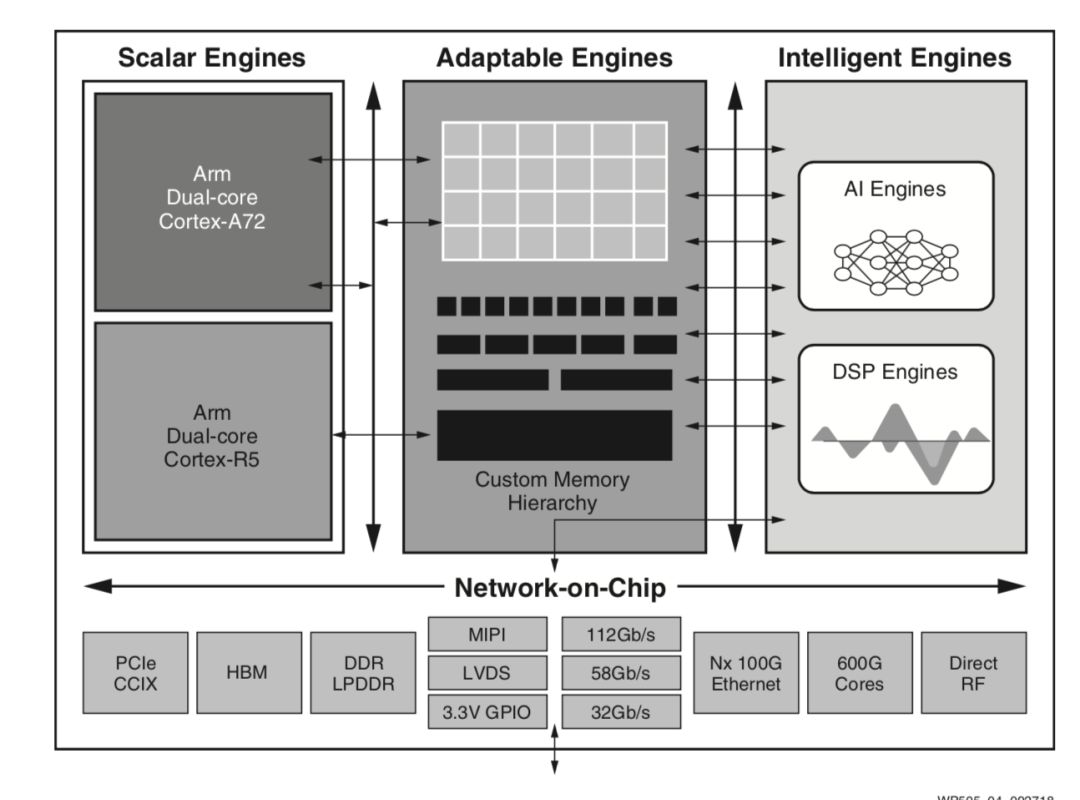

Versal ACAP 的体系架构从构建伊始即可支持软件可编程,拥有高度灵活的、每秒传输速率高达数兆比特的片上网络 (NoC)。NoC 无缝集成所有引擎和关键接口,使得该平台在启动时即可使用平台的各项资源,并且方便软件开发者、数据科学家和硬件开发者等都能轻松进行编程。通过一系列工具、软件、库、IP、中间件和固件,ACAP 让使用者能随时通过业界标准设计流程开发各种定制化的加速计算解决方案。

Versal 到底是什么?

看完上面的介绍,可能很多人还是很蒙圈,这个Versal ACAP 到底是个很东东呢?这里深度解读一下。

在去年10月的赛灵思2018开发者大会(XDF)上,赛灵思CEO Victor Peng亲自发布了基于7nm工艺的ACAP平台首款产品Versal--Versal 这个词代表多样性和通用性,它是一款号称针对任何应用做AI加速应用的平台级产品,首先推出AI核心版和基础版,后续会推出旗舰版、AI RF版、边缘计算版、HBM版等,这是2018年继华为麒麟980,苹果A12之后,又一堪称惊世之作的7nm产品。

Victor 在演讲中指出,放眼全球,人工智能技术发展迅速,芯片技术已经赶不上AI的发展,新的算法新的框架新的场景应用层出不穷,要应对这样的变化,就需要有灵活多变的架构去是适应这样的变化,早在四年前,赛灵思启动“珠穆朗玛”技术,就是打造一个具有自适应、和可以灵活实现计算加速的平台,这就是ACAP平台。

“随着 AI 和大数据的爆炸性发展以及摩尔定律的放缓,行业已经走到了一个关键的转折点。芯片设计的周期已经无法跟上创新的脚步。Versal 是历经 4 年的开发的业界首款 ACAP产品。我们对其进行了独特设计,支持所有类型的开发者通过优化的软硬件来为他们的整体应用提速,同时具备即时的灵活应变能力,从而能够跟上科技快速发展的步伐。在业界需求最迫切的时刻 ACAP 可谓雪中送炭。”他强调。

“现在中国人工智能技术非常火爆,有大量人工智能初创企业,我认为他们其实不一定要去开发AI芯片,他们可以采用我们的Versal平台开发具体应用,可以在算法和框架方面深入研究,这样不用从头做起,可以加速AI应用。”他指出,“就像深鉴科技,他们两年前就在基于赛灵思的产品做AI方面的开发,因此在被我们收购后其成果可以迅速应用到Versal平台上,当然,这也说明了我们产品的灵活性很好。”

Versal深度揭秘

赛灵思产品及技术营销高级技术总监Kirk Saban在随后的演讲中详解介绍了这款可能改变人工智能应用格局的产品。

他在专访中指出,我们处于一个杂乱无序的数据堆积如山的时代,一种架构无法独自完成数据处理,需要异构计算。

而从过去40年半导体发展历史来看,计算引擎CPU单纯采用"工艺缩放scaling"技术发展的道路遇到了很大的挑战,难以通过等量的计算提升换取等量的性能提升,半导体工艺的变化迫使计算引擎变成并行趋势。

“摩尔定律终结后,CPU、GPU已经不适应未来趋势,NV的新品只有最高的计算值,例如最新的T4号称是P4强l6倍,但实际性能提升只有2.5倍左右,所以我们需要新的架构。”Kirk指出。

所以,目前半导体行业在探索能替代的架构,包括一些原先在特殊领域的架构,但是这些架构各有优缺点,谁是最好的呢?

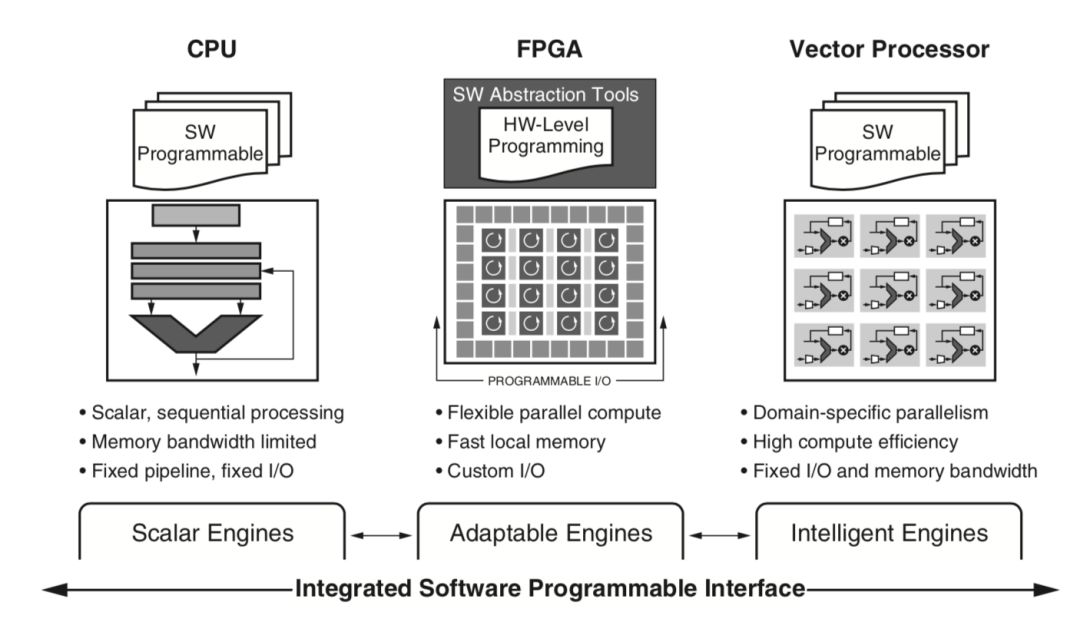

1、标量处理(例如,CPU)在具有不同决策树和大量库的复杂算法中非常有效 - 但在性能缩放方面受到限制。

2、矢量处理元件(例如,DSP,GPU)在较窄的可并行化计算功能集上更有效 - 但由于不灵活的存储器层次结构,造成延时和功耗增加,

3、可编程逻辑(例如,FPGA)可以针对特定计算功能进行精确定制,使其在延迟敏感的实时应用(例如,汽车驾驶员辅助)和不规则数据结构(例如,基因组测序)方面表现最佳 - 但其算法=需要花费数小时来编译,时间太长了!

Kirk表示赛灵思推出的新型异构计算架构,即自适应计算加速平台(ACAP)是把各个架构的优势融合起来,它提供了与下一代可编程逻辑紧密耦合的最好的世界级矢量和标量处理元件( PL),全部与高带宽片上网络(NoC)融合在一起,可以提供对所有三种处理类型的存储器映射访问。,与任何单独的一个架构相比,这种紧密耦合的混合架构可以实现惊人的定制和性能提升!

“当今开发者需要软件的可编程能力、满足广泛应用的性能和适应快速创新的灵活应变能力。我们的产品可以满足开发者这三个要求。”他指出。“通过软件可编程实现对个各种负载的灵活支持,实现性能的大幅度提升。”

赛灵思ACAP框图

实际上,Versal是完全软件可编程,可以实现高达20倍的性能显著提升,比当今最快的FPGA还要快100倍!Versal产品组合包括 Versal 基础系列( Versal Prime),Versal 旗舰系列 (Versal Premium旗舰)系列和 HBM 系列,能针对要求最严格的应用提供业界领先的性能、连接性、带宽和集成功能。此外,该产品组合还包括 AI 核心系列(AI Core),AI 边缘系列 ( AI Edge) 和 AI 射频系列(AI RF),采用突破性的 AI 引擎。

AI 引擎是一种新型硬件模块,专为解决各种应用低时延 AI 推断的新需求而设计,同时支持高级 DSP 实现方案,满足无线和雷达等应用要求。它与 Versal 自适应硬件引擎紧密结合,支持整体应用加速,也就是说软硬件都能调节,从而确保最高性能和效率。

当天发布的Versal Prime 系列和 Versal AI Core 系列,相对于业界领先的 GPU,AI 推断性能预计能提升 8 倍。

VERSAL AI 核心系列

Versal AI 核心系列提供该系列最高计算性能和最低时延,实现突破性的 AI 推断吞吐量和性能。该系列针对云端、网络和自动驾驶技术进行了优化,提供业界最广泛的 AI 和工作负载加速功能。Versal AI 核心系列 有 5 款产品,提供 128 到 400 个 AI 引擎。该系列包括双核 Arm® Cortex™-A72 应用处理器、双核 Arm® Cortex™-R5 实时处理器、256KB 片上 ECC 存储器、超过 1900 个专为高精度低时延浮点运算而优化的 DSP 引擎。此外,它还包括 190 多万个系统逻辑单元以及超过 130Mb 的 UltraRAM、高达 34Mb 的块 RAM 和 28Mb 分布式 RAM 和 32Mb 新加速器 RAM 块,任何引擎都能直接访问,这也是 Versal AI 系列的独特之处,而且都能支持定制存储器架构。该系列还包括 PCIe® Gen4 8 信道和 16 信道以及 CCIX 主机接口、功耗优化型 32G SerDes、多达 4 个集成型 DDR4 存储器控制器、多达 4 个多速率以太网 MAC、650 个高性能 I/O(用于 MIPI D-PHY)、NAND、存储级内存接口和 LVDS、78 个多路复用 I/O(连接外部组件)和超过 40 个 HD I/O(3.3V 接口)。以上所有器件均通过业界一流的片上网络 (NoC) 实现互联,具有多达 28 个主/从端口,以低时延提供每秒多 Tb 带宽,而且提供高功率效率和原生软件的可编程性。完整的产品列表现已发布。

THE VERSAL PRIME 系列

Versal Prime 系列经过精心设计,适用于多个市场的广泛应用,并针对各种工作负载的连接性和在线加速进行了优化。这款中端系列包括 9 款产品,每款产品都采用双核 Arm® Cortex-A72 应用处理器、双核 Arm® Cortex-R5 实时处理器、256KB 片上存储器(带 ECC)、超过 4000 个专为低时延高精度浮点运算优化的 DSP 引擎。此外,它还包括 200 多万个系统逻辑单元,结合 200Mb 以上 UltraRAM、超过 90Mb 的块 RAM 以及 30Mb 分布式 RAM,能支持定制存储器架构。该系列还包括 PCIe® Gen4 8信道和 16 信道以及 CCIX 主机接口、功耗优化型 32Gb 每秒的 SerDes 和主流 58Gb 每秒的 PAM4 SerDes、多达 6 个集成型 DDR4 存储器控制器、多达 4 个多速率以太网 MAC、700 个高性能 I/O(支持 MIPI D-PHY)、NAND、存储级内存接口和 LVDS、78 个多路复用 I/O(连接外部组件)和超过 40 个 HD I/O(3.3V 接口)。以上均通过业界一流的片上网络 (NoC) 实现互联,具有多达 28 个主/从端口,以低时延提供每秒多 Tb 带宽,而且提供高功率效率和原生的软件可编程性。完整的产品列表现已发布。

Kirk 表示赛灵思未来的目标就是让机器学习更简单,用软件可编程让Versal在毫秒内实现可重配置,完成功能的切换,实现对负载场景的计算加速。“我们的AI引擎也有优化,AI核心版本针对不同AI应用有不同的AI引擎可以实现不同场景的支持。”而Victor也表示,赛灵思的ACAP平台是不断变化和进步的平台,因为AI技术还在发展初期还有更多算法更多框架出现,只有不断变化的架构才可以适应不断变化的需求。

首批 Versal ACAP 器件提前从台积电发回并出货给早期试用客户,是赛灵思创下的又一个历史性的里程碑和工程成就。Versal ACAP 是赛灵思多年软硬件投资及过去 35 年产品架构全部知识的积累。Versal ACAP 是一项重大的技术突破,它将面向所有应用和各种开发者开启一个异构计算加速的新时代。

—— Victor Peng,赛灵思总裁兼首席执行官

Versal ACAP 产品系列采用台积电 7 纳米工艺技术打造而成,是业界首款将软件可编程性与动态可配置的领域专用硬件加速以及帮助企业跟上当今快速创新步伐的灵活应变能力结为一体的平台。该产品系列融合了用于嵌入式计算的新一代标量引擎,用于 FPGA 芯片编程的自适应引擎,以及用于 AI 推断与高级信号处理的智能引擎,从而在计算性能和单位功耗性能上都大幅超越了CPU和GPU。

Versal AI Core 系列在整个 Versal 产品系列中提供了最高计算性能和最低时延,并通过 AI 引擎实现了突破性的 AI 推断吞吐量和性能。该系列针对云端、网络和自动驾驶技术进行优化,提供了业界最广泛的 AI 和工作负载加速功能。Versal Prime 系列的设计广泛适用于各种应用,并针对各种工作负载的连接性和在线加速进行了优化。

Versal AI Core 系列和 Versal Prime 系列均包含多款器件,每款器件都配备双核 Arm® Cortex®-A72 应用处理器、双核 Arm Cortex-R5F 实时处理器、超过 200 万个逻辑单元的自适应硬件以及 3,000 多个为高精度浮点与低时延优化的 DSP 引擎。Versal AI Core 器件提供多达 400 个专为 AI 推断和高级信号处理工作负载优化的 AI 引擎。

Versal 系列还包括其他四个产品系列,每个系列都有其独特的架构,可以为从云到联网乃至无线通信、边缘计算和端的各种市场的众多应用提供可扩展性和AI推断功能。

Versal 重要信息

全面供货

Versal AI Core 系列和 Versal Prime 系列将于 2019 年下半年上市。

赛灵思将于10月1日-2日在美国加州硅谷举办的2019 年赛灵思开发者论坛(XDF)上现场演示 Versal ACAP。

-

赛灵思

+关注

关注

32文章

1794浏览量

130510 -

Versal

+关注

关注

1文章

151浏览量

7535

原文标题:刚刚,赛灵思发了个大招!--Versal ACAP 开始出货了!

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

赛灵思Versal ACAP如何为算力“跨界赋能”?

赛灵思宣布两款Versal ACAP评估套件现已上市

Versal ACAP中的配电系统

使用QEMU启动Versal VCK190 ACAP

Versal ACAP收发器向导 LogiCORE IP产品指南

使用Model Composer设计PID控制器的Versal ACAP应用说明

用于PCI Express的Versal ACAP集成块产品指南

放大招!Versal ACAP 正式出货

放大招!Versal ACAP 正式出货

评论