首选我们来聊聊时序逻辑中最基础的部分D触发器的同步异步,同步复位即复位信号随系统时钟的边沿触发起作用,异步复位即复位信号不随系统时钟的边沿触发起作用,置数同理,rst_n表示低电平复位,我们都知道D触发器是一个具有异步复位异步置数的器件,那么怎么样Verilog来具体描述这个器件呢,接下来我们就来看一下,

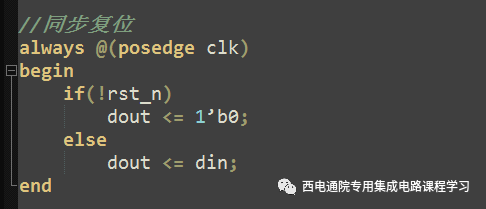

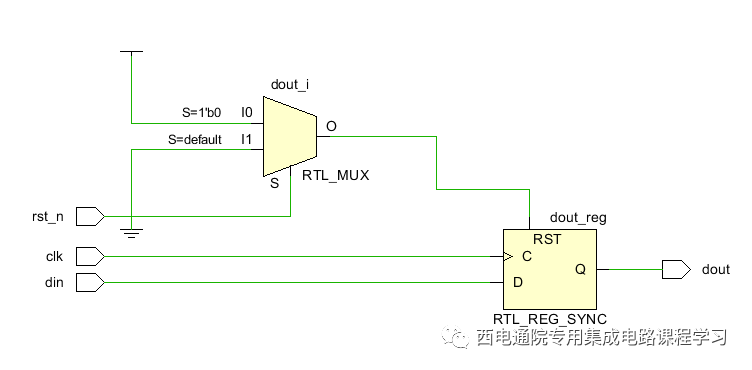

D触发器的几种表示形式同步复位

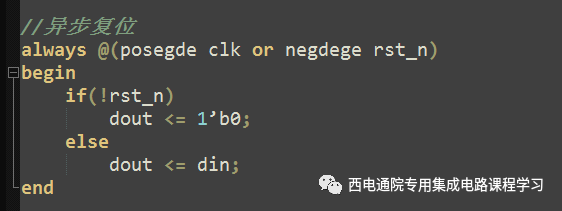

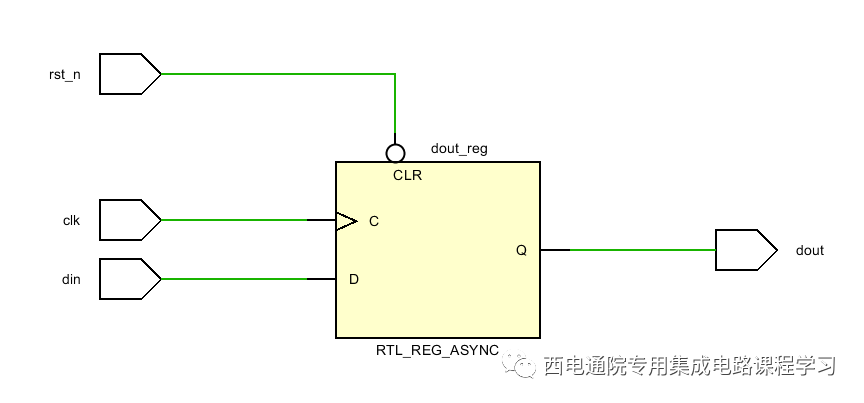

异步复位

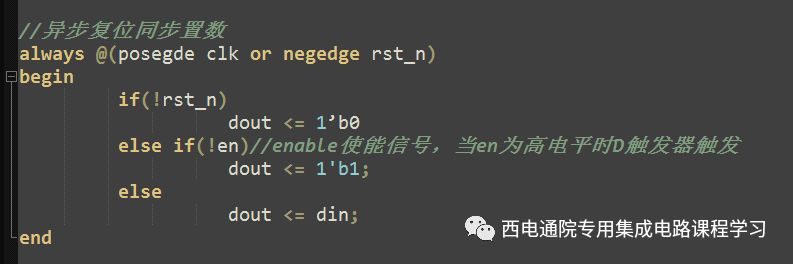

异步置数,同步置数。

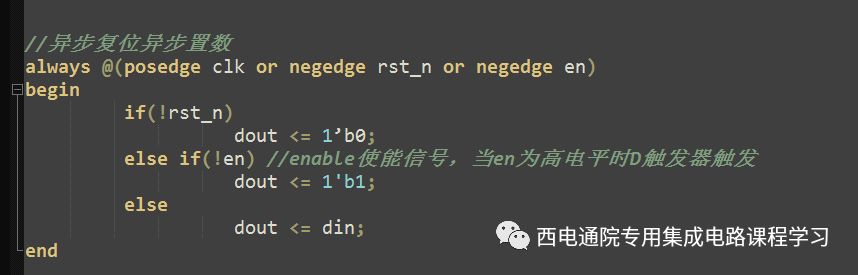

异步复位,异步置数

同步异步无非就是一个是否受系统时钟边沿触发,如果想要异步就直接加一个敏感信号就好了。不过一般工程中的书写形式就是异步复位,不过这种设计方法也有弊端,原因就是时序逻辑的冒险与竞争的问题。

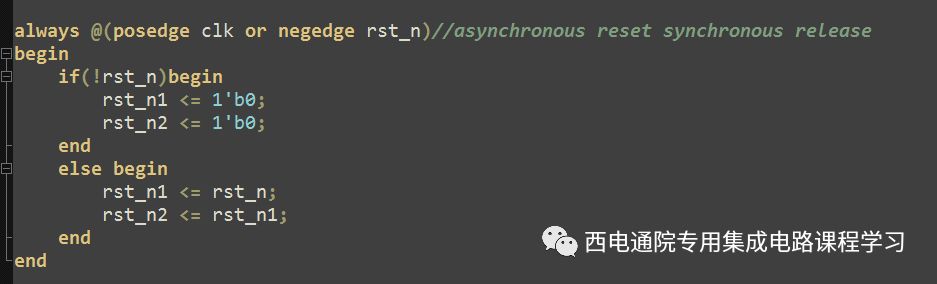

异步复位、同步释放

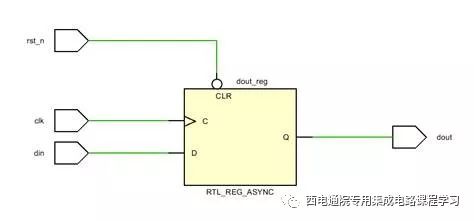

如下图可以看到异步复位的结构图,D触发器是复位优先级高于clk优先级,所以采用通异步复位的方法,但是异步复位D触发器存在竞争与冒险,比如当clk的上升沿和rst_n的下降沿同时来临的时候这时候系统应该听谁的,同样当clk的上升沿和rst_n的上升沿同时来临的时候容易使寄存器出现亚稳态。

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态引时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。这时系统是处于极不稳定的状态,这也是我们需要考虑的。

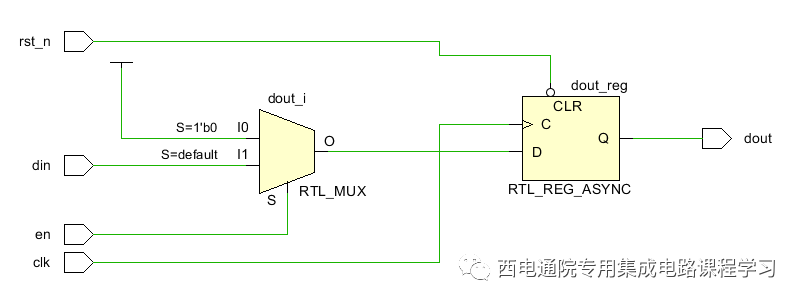

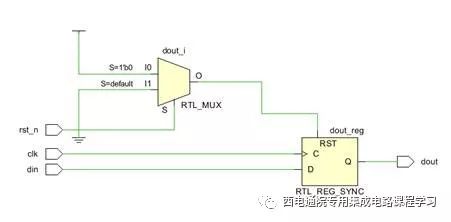

有人说既然异步复位会出现冒险竞争那我们使用同步复位不就行了,我们来看看同步复位的逻辑结构图,同步复位虽然解决了当clk的边沿来临的时候rst_n的边沿也正好来临所出现的冒险与竞争,但是从综合的电路上可以看出,多了一个组合逻辑,选择器(MUX),可想而知如果所有的寄存器复位都是这样,那会多浪费多少资源。那么这样就没有办法再解决了吗?答案是有的,一位前辈曾经说过,从正确到完美的道路是十分艰辛的,我们为了追求完美,引入异步复位、同步释放机制,即解决了同步复位浪费资源问题,又解决了异步复位带来的亚稳态。

这是复位信号同步化代码,系统时钟不变化,还是采用异步复位的方法,但是当复位信号操作时会进入一个同步寄存器,使得复位信号同步化,这样既避免了异步复位的冒险与竞争,又避免了同步复位耗费太多资源。只需要将复位信号同步化编写成独立模块,然后顶层例化就好了。系统时钟信号不变化。

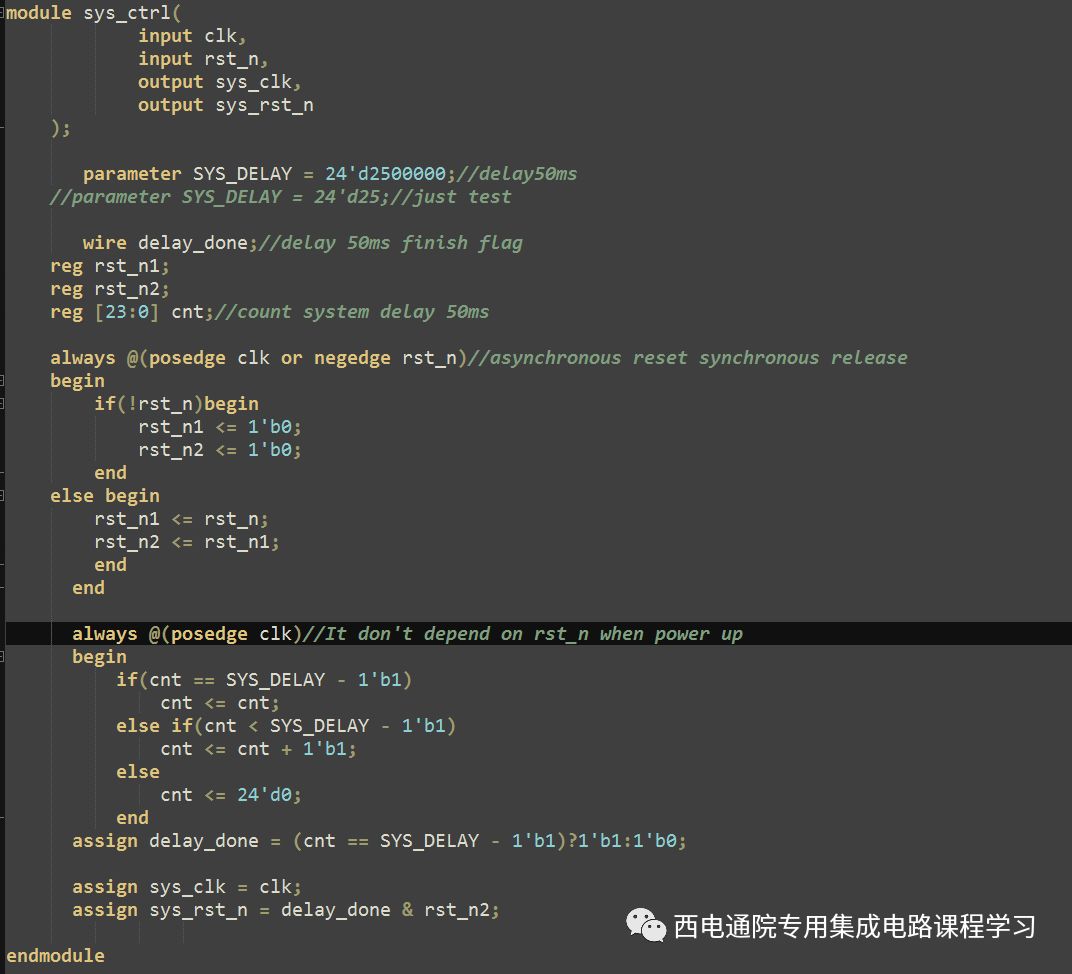

上电延时

开发板接通电源后会有一小段不稳定的状态,在比较大的工程中,逻辑资源利用的比较多的情况下,如果加上电源后直接进行复位操作,同样会使寄存器不稳定,所以,类似于按键消抖的方法,我们也给板子加电源后延时50ms,当系统稳定后在进行复位操作,再看bingo的书时,他是将这两个个分成两个模块然后实例化到一起,但为了提高代码的可移植性,我将异步复位同步释放和上电延时50ms写在一个模块。具体实现如下。

对于较小的工程,进行这些操作与否也就无可厚非,如果对于一个项目,需要要求必须尽善尽美,FPGA的优势便是数字信号处理,速度快,我们在保持速度的前提下,还需要使其准确率也提高,尽量占用少量的资源。这样异步复位,同步释放的机制就体现出来了。

-

寄存器

+关注

关注

30文章

5025浏览量

117697 -

D触发器

+关注

关注

2文章

147浏览量

47367

原文标题:异步复位同步释放机制-系统完美稳定

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?

D触发器,CLK突变时,输入D也突变,触发器的输出应该如何判定?

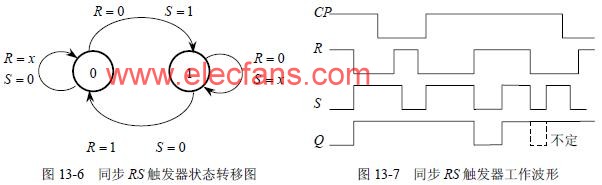

同步RS触发器原理

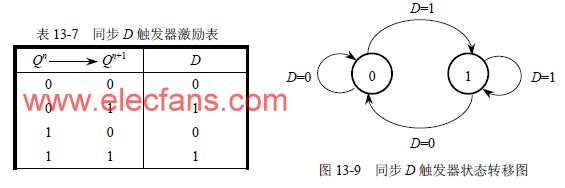

同步D触发器原理

同步触发器的触发方式和空翻问题

D触发器的几种表示形式同步复位、同步释放

D触发器的几种表示形式同步复位、同步释放

评论