一种高速流水线乘法器结构

大小:0.62 MB 人气: 2018-03-15 需要积分:0

标签:乘法器(36289)

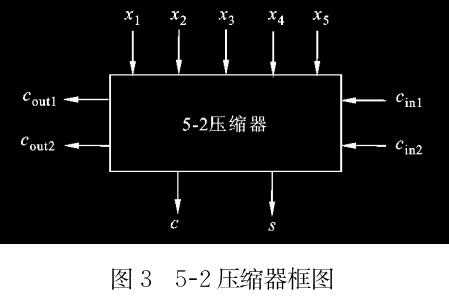

设计了一种新颖的32×32位高速流水线乘法器结构.该结构所采用的新型Radix-16 Booth算法吸取了冗余Booth编码与改进Booth编码的优点,能简单、快速地产生复杂倍数.设计完成的乘法器只产生9个部分积,有效降低了部分积压缩阵列的规模与延时.通过对5级流水线关键路径中压缩阵列和64位超前进位(CLA)加法器的优化设计,减少了乘法器的延时和面积.经现场可编程逻辑器件仿真验证表明,与采用Radix-8 Booth算法的乘法器相比,该乘法器速度提高了11%,硬件资源减少了3%.

非常好我支持^.^

(0) 0%

不好我反对

(0) 0%

下载地址

一种高速流水线乘法器结构下载

相关电子资料下载

- 触控小家电国产MCU新选择—LKT6850 357

- FPGA浮点IP内核究竟有哪些优势呢? 209

- 使用模拟乘法器的同步解调与基于开关的乘法器 37

- INA226驱动程序 1044

- 乘法器的Verilog HDL实现方案 258

- 基于DSP48E1的FIR滤波器设计 385

- HMC575LP4ETR有源宽带倍频器典型应用 275

- FPGA常用运算模块-复数乘法器 717

- FPGA常用运算模块-加减法器和乘法器 1336

- 定点乘法器设计优化V1 257