8.2.1 只读存储器ROM

顾名思义只读存储器ROM(Read-only memory)就是只能读出,不能写入的存储器,属于固定存储器,计算机或数字系统中需要长期存放的程序、表格、及一些常数、符号等数据就存放于其中,掉电时内存数据不会丢失。

一、只读存储器的电路结构

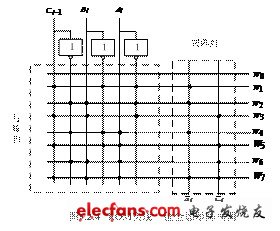

只读存储器的电路结构如图8.2.1 所示

只读存储器ROM的内部电路由存储阵列、地址译码器、输出缓冲器及存储器控制电路组成。

存储阵列是存储器的主体,实质上是由存储单元组成的集合体,每个存储单元又包含若干个基本存储单元,从而形成存储阵列。每个存储单元所包含的基本存储单元数由存储器容量中的“字长”来决定;存储阵列中所包含的存储单元数由存储容量中的“字节数”来决定。通常组成基本存储单元的元件可以是电容、半导体二极管、三极管和MOS管等,而每个基本存储单元可以存储一位二进制信息。

地址译码器由地址寄存器和地址译码器两部分组成。地址寄存器用于存放CPU送来的地址码,地址译码器则对地址寄存器中的地址码进行译码,产生相应的地址选择信号,进而选中相应的存储单元或基本存储单元。根据地址译码器的不同结构,存储器也可分为单译码编址存储器及双译码编址存储器。单译码编址时选中的是存储单元,双译码编址时,选中的是基本存储单元。

输出缓冲器实际上是一个三态、双向的缓冲器,用于锁存从存储单元中读出的每位信息,或用于存放需要写入存储单元的信息,因此是一个双向的缓冲器;三态主要是为了便与系统总线连接,其位数由存储阵列中存储单元的位数决定。例如:8K×4存储器的三态双向缓冲器应当有4位。三态双向缓冲器受控制电路和输出允许信号控制。

控制电路主要是通过接受CPU(中央处理器)送来的控制信号,经过组合变换后对地址寄存器、存储阵列和三态缓冲器等进行控制。

8.2.2 ROM在组合逻辑电路中的应用

按照所用器件类型分,ROM可分为二极管ROM、MOS场效应管ROM、双极型三极管ROM三种。首先来看一个4×4位二极管构成的掩膜ROM电路,如图8.2.2 所示。

地址译码器是一个2线-4线的地址译码器,地址线为![]() ,输出为

,输出为![]() (字线),可选取存储阵列中的任意一个字。输出控制端

(字线),可选取存储阵列中的任意一个字。输出控制端![]() 时,4条位线上的数据便能够通过三态门从

时,4条位线上的数据便能够通过三态门从![]() 上输出。例如,当地址码

上输出。例如,当地址码![]() 时,经过地址译码,使得字线

时,经过地址译码,使得字线![]() ,而

,而![]() ,

,![]() 字线上的高电平通过接有二极管的位线

字线上的高电平通过接有二极管的位线![]() 使得

使得![]() =1,而其余位线

=1,而其余位线![]() 由于和

由于和![]() 的交叉处无二极管,因此

的交叉处无二极管,因此![]() ,最终结果输出的数据为

,最终结果输出的数据为![]() ,由此不难分析出当

,由此不难分析出当![]() 时对应输出的数据分别为:

时对应输出的数据分别为:

从上述分析中可以看出,这个存储矩阵实际上是由16个存储单元构成的,图中每个十字交叉点就代表一个存储单元,交叉处有二极管的单元表示存储数据1,否则存储数据0;从图中还可看到,与位线![]() 的交叉点处有二极管的字线有两根,即

的交叉点处有二极管的字线有两根,即![]() ,而这两根字线都可能通过交叉点处的二极管使得

,而这两根字线都可能通过交叉点处的二极管使得![]() =1,因此位线上各点之间的关系是一种“逻辑或”的关系,故该存储矩阵实际上是一个编码电路,即一个组合电路,又可以将其看作是如图8.2.3所示的简化阵列图。图中有二极管的交叉点画有实心圆点,无二极管的交叉点不画。存储矩阵中位线上各圆点之间的关系为逻辑或,如

=1,因此位线上各点之间的关系是一种“逻辑或”的关系,故该存储矩阵实际上是一个编码电路,即一个组合电路,又可以将其看作是如图8.2.3所示的简化阵列图。图中有二极管的交叉点画有实心圆点,无二极管的交叉点不画。存储矩阵中位线上各圆点之间的关系为逻辑或,如![]() ,因此位线

,因此位线![]() 上加画了或门。而地址译码器实际上可由4个二极管与门构成的,其输出字线

上加画了或门。而地址译码器实际上可由4个二极管与门构成的,其输出字线![]() 与输入的关系是逻辑与的关系,即

与输入的关系是逻辑与的关系,即![]() ,

,![]() ,因此地址译码器也可用阵列形式画出,其输出线上应画与门。有时为画图方便,与门和或门的逻辑符号可以省略。故从阵列图中可以看出,ROM实际上就是一个“与-或阵列”。

,因此地址译码器也可用阵列形式画出,其输出线上应画与门。有时为画图方便,与门和或门的逻辑符号可以省略。故从阵列图中可以看出,ROM实际上就是一个“与-或阵列”。

由于ROM是一个与-或阵列,因此可以将存储器的地址线作为输入变量,将存储器的数据线作为输出变量,实现多输入、多输出的组合逻辑功能,即可以用存储器来实现组合逻辑函数。

例 8.2.1用ROM实现一位全加器电路,并画出其相应的阵列图。

解:用ROM实现组合电路,关键是要先写出逻辑函数的表达式,即ROM的输出函数表达式,并且应写成最小项之和的形式,这样便构成了一个标准的与-或表达式,从而能够根据ROM与-或阵列的特点,画出其阵列图。

一位全加器的和信号Si及进位信号Ci的逻辑表达式分别为

![]()

![]()

选择输入信号![]() 作为ROM的地址输入信号,全加器的和信号

作为ROM的地址输入信号,全加器的和信号![]() 及进位信号

及进位信号 ![]() 作为ROM的输出。从逻辑表达式中可以看到,和信号

作为ROM的输出。从逻辑表达式中可以看到,和信号![]() 及进位信号

及进位信号![]() 可由字线对应的最小项相或得到的,由地址输入信号译码得出各字线的最小项分别为:

可由字线对应的最小项相或得到的,由地址输入信号译码得出各字线的最小项分别为:![]() ,

,![]() ,…

,…![]() 。即地址译码器输出与输入之间是逻辑与的关系。而译码器的输出又可看作是存储矩阵的输入,存储矩阵的输出与其输入之间是逻辑或的关系,故

。即地址译码器输出与输入之间是逻辑与的关系。而译码器的输出又可看作是存储矩阵的输入,存储矩阵的输出与其输入之间是逻辑或的关系,故

![]() ,

,

![]() 。

。