5.3.1 钟控JK触发器电路结构与工作原理

RS触发器结构简单,其功能有限,一般使用时,RS触发器必须考虑约束条件问题。在RS触发器的基础上,对电路改进,避免输入端约束条件的限制,这就是JK触发器。JK触发器电路的结构形式如图5.3.1所示。

比较图5.2.8中的钟控RS触发器和图5.3.1中的钟控JK触发器,不同之处在于将G1的输出反馈到了G4的输入端,将G2的输出反馈到了G3的输入端,由于输出端的互补,反馈到G3和G4端的值不会出现同时为1的情况,所以在JK输入端同时为1时,也不会出现![]() 的情况,对输入端JK来说也就没有约束条件的限制。

的情况,对输入端JK来说也就没有约束条件的限制。

由图5.3.1,在CP = 1时,有![]() ,

,![]() ,代入与-非门组成的RS触发器的特性方程(5.2.1)式得

,代入与-非门组成的RS触发器的特性方程(5.2.1)式得

![]()

![]()

![]()

即

![]()

![]() (5.3.1)

(5.3.1)

而![]()

![]()

![]()

![]()

通过上面分析可以看出JK触发器没有约束条件得限制。式(5.3.1)是CP = 1时JK触发器的特性方程。在CP = 0时,触发器的输出状态保持不变。

|

表5.3.1 JK触发器逻辑状态转移真值表 |

||

J K |

|

状 态 |

|

0 0 0 1 1 0 1 1 |

0 1 1 0

|

保持 复位 置位 计数 |

对(5.3.1)式的分析,可以得到JK触发器的逻辑状态转换图,如图5.3.2所

示。也可以得到其逻辑状态转移真值表,见表5.3.1。在图5.3.2和表5.3.1中,钟控JK触发器的状态转移,都是在CP = 1期间发生的。

从表5.3.1可以看出,J输入端是高电平有效置位,K输入端是高电平有效复位,J、K输入端都没有高电平时,输出端的状态保持不变,J、K输入端都是高电平时,输出端的值翻转为初始值的相反值,通常可作为计数使用。

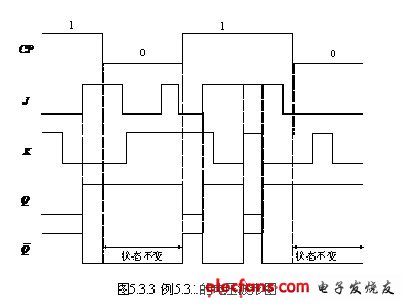

例5.3.1 在图5.3.1所示的JK触发器中,已知J、K波形如图5.3.3所示,试画出输出端![]() 和

和![]() 的电压波形图。

的电压波形图。

解:根据前面分析所得的JK触发器特点,可以作出输出端的波形如图5.3.3所示。值得注意的是在时钟信号CP=1期间,J=K=1时,触发器翻转为前一状态相反的状态值。

5.3.2 主从JK触发器

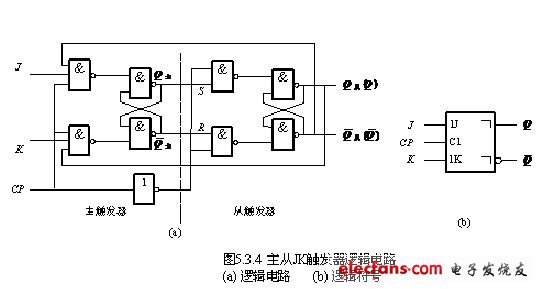

主从结构的JK触发器,可以防止钟控信号作用期间输出端Q的多次翻转现象。主从JK触发器的逻辑电路,如图5.3.4所示。其中(a)图是其逻辑电路,(b)图是其逻辑符号。

时钟信号的值与主、从触发器的关系为:

(1) CP=0时,主触发器被封锁,从触发器工作。

(2) CP=1时,主触发器工作,从触发器被封锁。

下面分析在JK输入端分别为不同的逻辑值时,输出端的状态情况。

(1). J = K = 0时

在CP=1期间,![]() 的状态保持不变,在时钟信号从1变化到0时刻,

的状态保持不变,在时钟信号从1变化到0时刻,![]() 的状态保持不变,即

的状态保持不变,即![]() ;

;

(2). J = 0,K = 1时

若![]() 、

、![]() ,

,![]() 的状态值保持不变。由于主从触发器的输出状态

的状态值保持不变。由于主从触发器的输出状态![]() 和

和![]() 是取决于主触发器的状态,根据假设的输出初始状态可得:在CP=1期间,

是取决于主触发器的状态,根据假设的输出初始状态可得:在CP=1期间,![]() 、

、![]() ,时钟信号从1变化到0时刻,

,时钟信号从1变化到0时刻,![]() 、

、![]() ,即:

,即:![]() 。

。

若![]() 、

、![]() ,在CP=1期间,则

,在CP=1期间,则![]() 、

、![]() ,时钟信号从1变化到0时刻,

,时钟信号从1变化到0时刻,![]() 、

、![]() ,即:

,即:![]() 。

。

所以,当J = 0,K = 1时,时钟信号由1→0时刻,从触发器置0。

(3). J = 1,K = 0时

若![]() 、

、![]() ,在CP=1期间,则

,在CP=1期间,则![]() 、

、![]() ,时钟信号从1变化到0时刻,

,时钟信号从1变化到0时刻,![]() 、

、![]() ,即:

,即:![]() 。

。

若![]() 、

、![]() ,由于主从触发器的输出状态

,由于主从触发器的输出状态![]() 和

和![]() 取决于主触发器的状态,根据假设的输出初始状态可得:在CP=1期间,则

取决于主触发器的状态,根据假设的输出初始状态可得:在CP=1期间,则![]() 、

、![]() ,时钟信号从1变化到0时刻,

,时钟信号从1变化到0时刻,![]() 、

、![]() ,即:

,即:![]() 。

。

所以,当J = 1,K = 0时,时钟信号由1→0时刻,从触发器置1。

(4). J = 1,K = 1时

若![]() 、

、![]() ,在CP=1期间,则

,在CP=1期间,则![]() 、

、![]() ,时钟信号从1变化到0时刻,

,时钟信号从1变化到0时刻,![]() 、

、![]() ,即:

,即:![]() 。

。

若![]() 、

、![]() ,在CP=1期间,则

,在CP=1期间,则![]() 、

、![]() ,时钟信号从1变化到0时刻,

,时钟信号从1变化到0时刻,![]() 、

、![]() ,即:

,即:![]() 。

。

所以,当J = 1,K = 1时,时钟信号由1→0时刻,从触发器翻转为相反的状态。

通过上面的分析可知,当CP=1时,主触发器工作,而从触发器保持不变,主触发器的输出与此时的输入端JK有关,也与触发器的初始状态有关(由于![]() 、

、![]() 反馈到了输入端)。在时钟信号从1变化到0时刻,从触发器接收主触发器数据,将主触发器的数据送到输出端保存下来。

反馈到了输入端)。在时钟信号从1变化到0时刻,从触发器接收主触发器数据,将主触发器的数据送到输出端保存下来。

例5.3.2 在图5.3.4所示的主从JK触发器中,已知J、K波形如图5.3.5所示,试画出输出端![]() 的电压波形图。设初态

的电压波形图。设初态![]() 。

。

解:初态![]() ,此时的

,此时的![]() 。在图中的CP=1期间,JK输入端的值没有发生变化,所以根据上面的分析,对应画出

。在图中的CP=1期间,JK输入端的值没有发生变化,所以根据上面的分析,对应画出![]() 的波形如图5.3.5所示,在时钟信号的下降沿时,从触发器接收主触发器的信号,保存在输出端。对应的波形如图5.3.5所示。

的波形如图5.3.5所示,在时钟信号的下降沿时,从触发器接收主触发器的信号,保存在输出端。对应的波形如图5.3.5所示。

5.3.3 主从JK触发器的一次翻转现象

在例题5.3.2中,在时钟信号下降沿到来时,可以直接根据此时的J、K的值来得到输出端的值,因为在CP=1期间,输入端的值没有发生变化。如果在CP=1期间,输入端的值发生了变化时,就不能根据此时时钟信号下降沿对应的J、K的值来得到输出端的值。下面可以通过例题5.3.3来分析这种情形。

例5.3.3 在图5.3.4所示的主从JK触发器中,已知J、K波形如图5.3.6所示,试画出输出端![]() 和

和![]() (Q)的电压波形图。设初态

(Q)的电压波形图。设初态![]() 。

。

图中第一个时钟信号上升沿到来时,主触发器工作,此时![]() 、J = 1、K = 0,从图5.3.4分析可得

、J = 1、K = 0,从图5.3.4分析可得![]() 。接着J、K的数据发生了变化,在J = 0、K = 1时(图中得①处),因为触发器的输出端Q (

。接着J、K的数据发生了变化,在J = 0、K = 1时(图中得①处),因为触发器的输出端Q (![]() )的值还没有变化,

)的值还没有变化,![]() 的值仍为0,反馈到输入端和K相与,此0逻辑值封锁了K为1的逻辑值,所以,在这种情况下,

的值仍为0,反馈到输入端和K相与,此0逻辑值封锁了K为1的逻辑值,所以,在这种情况下,![]() 的值没有根据J = 0、K = 1而置为0,而是仍保持在

的值没有根据J = 0、K = 1而置为0,而是仍保持在![]() 状态。在第一个时钟信号下降沿到来时,从触发器接收主触发器的数据,即

状态。在第一个时钟信号下降沿到来时,从触发器接收主触发器的数据,即![]() 。

。

图中第二个时钟信号上升沿到来时,主触发器工作,此时![]() 、

、![]() 、J = 1、K = 1,可得新的状态

、J = 1、K = 1,可得新的状态![]() 。接着J、K的数据发生了变化,在J = 1、K = 0时(图中得②处),和上面分析相同的道理,因为触发器的输出端Q (

。接着J、K的数据发生了变化,在J = 1、K = 0时(图中得②处),和上面分析相同的道理,因为触发器的输出端Q (![]() )的值还没有变化,

)的值还没有变化,![]() 的值仍为0,反馈到输入端和J相与,此0逻辑值封锁了J为1的逻辑值,所以,在这种情况下,

的值仍为0,反馈到输入端和J相与,此0逻辑值封锁了J为1的逻辑值,所以,在这种情况下,![]() 的值没有根据J = 1、K = 0而置为1,而是仍保持在

的值没有根据J = 1、K = 0而置为1,而是仍保持在![]() 状态。在第一个时钟信号下降沿到来时,从触发器接收主触发器的数据,即

状态。在第一个时钟信号下降沿到来时,从触发器接收主触发器的数据,即![]() 。

。

同样的道理分析,可以得出在第三个时钟脉冲为1期间,![]() 和Q的波形如图所示。

和Q的波形如图所示。

从例5.3.3的分析看出,时钟脉冲为1期间,J和K的数据发生了多次变化,但是由于输出端Q (![]() )的值要等到下降沿到来时才会改变,输出端Q和

)的值要等到下降沿到来时才会改变,输出端Q和![]() 总有一个为0,反馈到输入端,由于与门的作用,必然会封锁其中一个输入端,使得主触发器的输出

总有一个为0,反馈到输入端,由于与门的作用,必然会封锁其中一个输入端,使得主触发器的输出![]() 的变化只能发生一次。这种变化的关系是:

的变化只能发生一次。这种变化的关系是:

(1) 当输出端![]() 时,主触发器只能接收使

时,主触发器只能接收使![]() 置为1的信号,此时只能使

置为1的信号,此时只能使![]() 置为1,

置为1,![]() 不能从1再置为0。

不能从1再置为0。

(2) 当输出端![]() 时,主触发器只能接收使

时,主触发器只能接收使![]() 置为0的信号,此时只能使

置为0的信号,此时只能使![]() 置为0,

置为0,![]() 不能从0再置为1。

不能从0再置为1。

所以,在判断主从触发器的输出端的状态时,不能从下降沿到来时刻,从输入端的值来得出输出端的状态,除非在CP=1的期间,输入端的值没有发生变化,才可以用这种方法来得出输出端的状态。如果在CP=1的期间,输入端的值发生变化,输出端的状态应该从主触发器得到。

在主从结构的RS触发器也有类似的情况,只是它没有将输出端Q反馈到输入端,所以在CP=1的期间,![]() 可以多次翻转。

可以多次翻转。

5.3.4 边沿JK触发器动作特点

主从结构JK触发器,解决了一般钟控触发器输出端的多次翻转现象,但是也存在主触发器的一次翻转现象,不能根据时钟信号的下降沿到来时,由J、K的值得出输出端的状态,其抗干扰能力也较弱。为了提高其抗干扰能力,同时能够根据时钟信号的下降沿到来时,由J、K的值得出输出端的状态,具有这种动作特征的触发器就是边沿JK触发器。图5.3.7是其逻辑电路和符号。

电路中![]() 、

、![]() 是直接复位、置位功能端,其作用如下:

是直接复位、置位功能端,其作用如下:

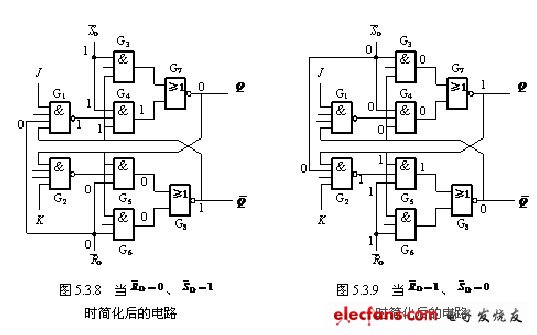

(1)当![]() 、

、![]() 时,其简化后逻辑电路如图5.3.8所示。门G5、G6输出为0,G8输出为1,即

时,其简化后逻辑电路如图5.3.8所示。门G5、G6输出为0,G8输出为1,即![]() ;同时

;同时![]() 的低电平送到了G1,则G1输出为1,G4输出为1,G7输出为0,即

的低电平送到了G1,则G1输出为1,G4输出为1,G7输出为0,即![]() ,触发器复位。从分析的结果来看,输出与时钟信号、J、K输入端无关,此时

,触发器复位。从分析的结果来看,输出与时钟信号、J、K输入端无关,此时![]() 具有直接复位作用。由于复位与时钟信号无关,所以也称为异步复位。

具有直接复位作用。由于复位与时钟信号无关,所以也称为异步复位。

(2)当![]() 、

、![]() 时,简化后的逻辑电路如图5.3.9所示。同样可以得到

时,简化后的逻辑电路如图5.3.9所示。同样可以得到![]() 、

、![]() ,触发器置位,此时

,触发器置位,此时![]() 具有置位作用。由于置位与时钟信号无关,所以也称为异步置位。

具有置位作用。由于置位与时钟信号无关,所以也称为异步置位。![]() 和

和![]() 的复位和置位都是低电平有效。

的复位和置位都是低电平有效。

(3)当![]() 、

、![]() 时,则可以得到

时,则可以得到![]() 、

、![]() 。实际使用时应该避免出现

。实际使用时应该避免出现![]() 和

和![]() 同时为低电平的情况,因为它们的低电平同时消失时,输出的状态不确定。

同时为低电平的情况,因为它们的低电平同时消失时,输出的状态不确定。

(4)当![]() 、

、![]() 时,输出端的值由CP、J、K的值来决定。其工作原理分析如下:

时,输出端的值由CP、J、K的值来决定。其工作原理分析如下:

(ⅰ) 当CP=0期间,触发器状态不变

门G1和G2输出为1,门G3和G6输出为0,如果初态![]() 、

、![]() ,则G5输出为1,G8输出为0,同时G4输出为0,G7输出为1,输出端的值没有改变。如果初态

,则G5输出为1,G8输出为0,同时G4输出为0,G7输出为1,输出端的值没有改变。如果初态![]() 、

、![]() ,输出端的值仍然不会改变。所以在CP=0时,触发器处于保持状态。在CP由0→1时刻,触发器状态仍保持不变。

,输出端的值仍然不会改变。所以在CP=0时,触发器处于保持状态。在CP由0→1时刻,触发器状态仍保持不变。

(ⅱ) 当CP=1期间,触发器状态不变,但触发器接收CP下降沿到来前瞬间的J、K的信号,改变输出端的值。

如果初态![]() 、

、![]() ,则G5和G6输出为0,G8输出为1,反馈到G3,则G3输出为1,从而G7输出为0,即触发器状态保持,与J、K的值无关。如果初态

,则G5和G6输出为0,G8输出为1,反馈到G3,则G3输出为1,从而G7输出为0,即触发器状态保持,与J、K的值无关。如果初态![]() 、

、![]() ,同样处于保持状态。

,同样处于保持状态。

在CP由1→0时刻,门G1、G2的传输延迟时间比基本触发器的延迟时间长。时钟信号的下降沿首先封锁了G3和G6,使其输出为0,此时图5.2.7的简化为图5.3.10所示的(a),进一步简化为图5.3.10的(b)图,与图5.3.1电路的结构形式完全相同。在时钟信号下降沿时刻,J、K的数据作用到了输出端,其输出端的逻辑状态的变化遵循JK触发器的特性方程。即:![]()

![]() 。

。

通过上面的分析可知,实现JK触发器的边沿触发是利用门电路的传输延迟时间来达到的。触发器的次态仅仅取决于CP信号的边沿(可能是下降沿,也可能是上升沿)到达时输入的逻辑状态,在此之前或者之后,输入端的信号变化时不会影响到输出端的值。这一边沿变化的特点提高了其抗干扰能力和工作的可靠性。

下降沿触发JK触发器的功能表如表5.3.2所示。

|

表5.3.2 下降沿触发JK触发器逻辑功能表 |

|||

CP |

|

|

状 态 |

|

× × ↓ ↓ ↓ ↓ |

0 1 × × 1 0 × × 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 |

0 1 1 0

0 1 1 0

|

复 位 置 位 保 持 置 0 置 1 计 数 |

例5.3.3在图5.3.7所示的边沿JK触发器中,已知J、K、![]() 和

和![]() 波形如图5.3.11所示,试画出输出端

波形如图5.3.11所示,试画出输出端![]() 的电压波形。设初始状态

的电压波形。设初始状态![]() 。

。

解:边沿JK触发器的工作特点是:输出端的逻辑状态取决于时钟信号下降沿到来时J、K的值,![]() 、

、![]() 是低电平直接复位、置位功能端。可以作出输出端的波形如图5.3.11所示。

是低电平直接复位、置位功能端。可以作出输出端的波形如图5.3.11所示。