前面各章已经介绍了逻辑电路的一般表示方法,但那里的方法并不适合于描述可编程逻辑器件PLD内部结构和功能。为此,本章将介绍一种新的逻辑表示法——PLD表示方法。这种表示方法在芯片内部配置和逻辑图之间建立了一一对应的关系,并将逻辑图和真值表结合起来,构成了一种紧凑而易于识读的表达形式。本节介绍几种比较简单的PLD。

1.连接方式

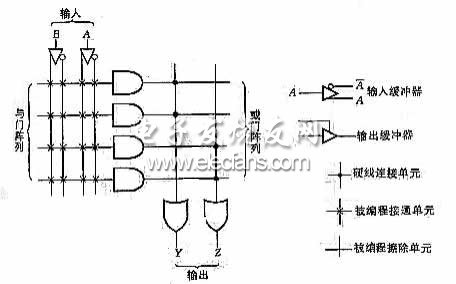

PLD电路由与门和或门阵列两种基本门阵列组成。图5.17(a)是一个基本的PLD结构图。

(a)基本的PLD结构图 (b) PLD连接方式

图5.17 PLD表示法

从图中可以看出,门阵列交叉点上连接方式共有三种情况,其图形符号如图5.17(b):

(1)硬线连接:固定连接,不可以编程改变。

(2)可编程“接通”单元:依靠用户编程来实现“接通”连接。

(3) 可编程“断开”单元:编程实现断开状态。这种单元又称为被编程擦除单元。

2.基本门电路的PLD表示法

PLD的输入缓冲器(或反馈缓冲器)采用互补输出结构,其图形符号如图5.17b所示,其真值表列于表5.2。

表5.2 PLD输入缓冲器真值表

|

输入 |

输出 |

|

|

|

|

0 |

0 1 |

|

1 |

1 0 |

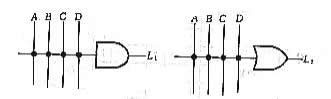

一个4输入端与门的表示法如图5.18a所示。图中L1=ABCD,通常把A、B C、D称为输入项,L1称为乘积项(或简称积项)。4输入端或门如5.18b所示,其中L2=A+B+C+D。

(a)与门符号 (b)或门符号

图5.18 PLD表示法的图形符号

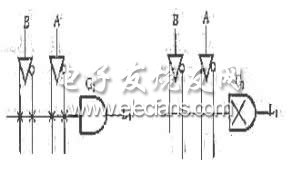

在图5.19中,逻辑电路的输出变量  和

和  为:

为:

|

|

输入项  被编程接通,与门的所有输入项均不接通,保持“悬浮”的1状态,输入项

被编程接通,与门的所有输入项均不接通,保持“悬浮”的1状态,输入项  硬线连接。

硬线连接。

图5.19 PLD表示的与门阵列 (a)与门默认状态符号 (b)图a的等效符号

图5.20 与门的默认状态

图5.19中与门G1对应的所有输入项被编程连通,输出项恒等于0,这种状态为与门编程的默认状态,如图5.20a所示。可以在与门G1中划一个“´” 取代各输入项对应的“´”,其图形符号如图5.20b所示。

3.PROM的PLD表示法

PROM实质上是可编程逻辑器件,它包含一个固定连接的与门阵列(该与门阵列就是全译码的地址译码器)和一个可编程的或门阵列。相应地,4位输入地址码的PROM可用图5.21中PROM的输入项推广到m个,则实现地址译码器的与门数为2m个,输入项数提高,与门阵列增大。而与门阵列增大,则开关时间变长,速度减慢。因此,一般只有小规模的PROM才作为可编程逻辑器件使用,密度高达2百万位/片的大规模PROM,一般只作为存储器用。

图5.21 PROM电路的PLD表示法