DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制

2017-09-01 14:03:41 4392

4392

DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,

2017-09-26 11:39:47 6363

6363

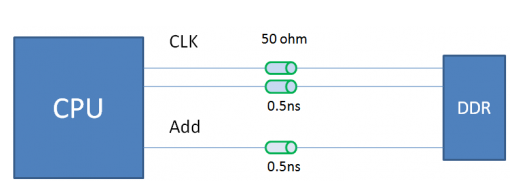

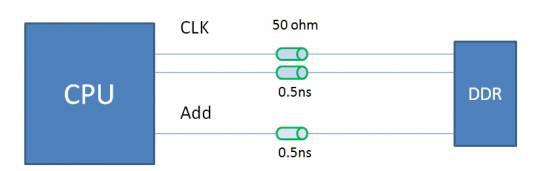

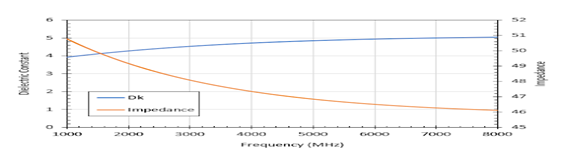

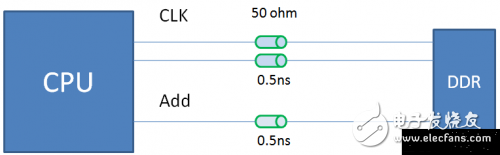

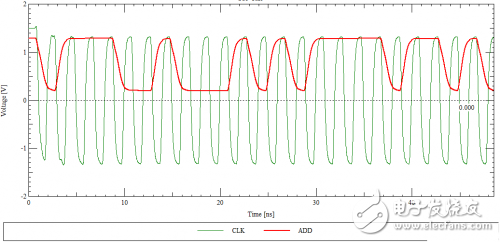

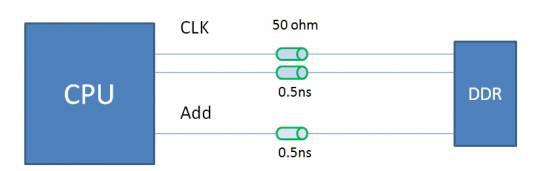

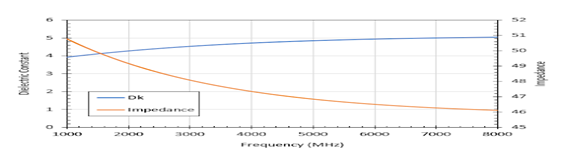

PCB设计时DDR线宽和阻抗是怎样确定下来的呢?让我们通一个具体的项目来学习一下。

2018-07-06 09:04:47 16923

16923

对PCB设计者来说,创建原理图符号库和PCB封装库是十分基础却又非常重要的工作。只有确保原理图符号库和PCB封装库准确无误,才能保证PCB设计工作得以顺利开展。

2022-10-27 10:37:28 706

706 上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。 由于

2023-08-24 08:40:05 899

899

100M到200M的ADC在PCB设计时,要进行严格的阻抗匹配么?有没有一些标准性的文档来说明呢

2023-12-05 06:30:10

做板载内存的时候只需要配置好内存SPD就可以了。控制组信号长度控制要求和地址/命令组信号的要求类似,设计的时候应该按照CPU厂家的要求来做,INTEL凌动N450要求控制在时钟信号0mil到正

2011-10-27 14:53:32

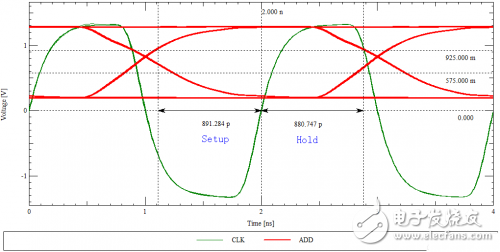

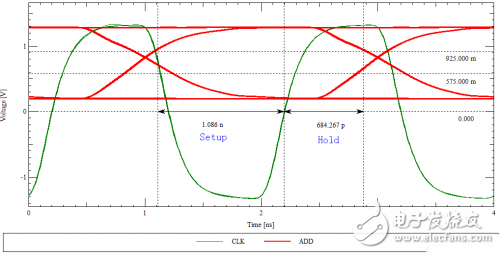

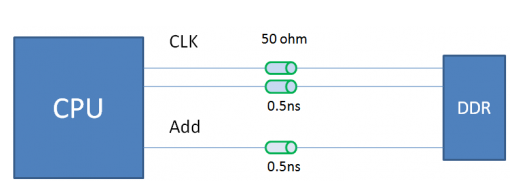

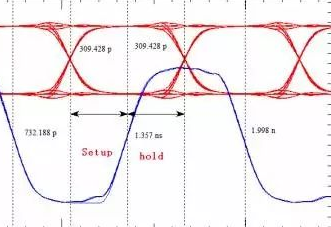

“Write leveling”技术来控制器件内部偏移时序等有效措施。虽然在保证设计实现和信号的完整性起到一定作用,但要实现高频率高带宽的存储系统还不全面,需要进行仿真分析才能保证设计实现和信号质量

2014-12-15 14:17:46

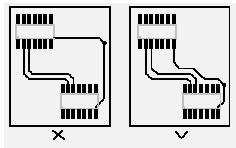

这篇帖子跟大家一起来讨论下DDR3布线的那些事:DDR3的设计有着严格等长要求,归结起来分为两类(以64位的DDR3为例): 数据 (DQ,DQS,DQM):组内等长,误差控制在20MIL以内,组间

2016-10-28 10:25:21

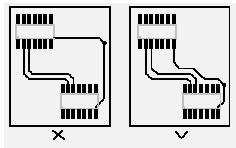

)GROUP F 中 CLK、CLKn 差分对的线长误差控制在 5mil 以内;CLK/CLKn 不能短于任意一组 DATA/DM/DQS。3.走线规则1)DDR3 的信号走线必须有完整参考面,以保证

2019-09-20 09:05:04

DDR布线在pcb设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的裕量。要保证系统的时序,线长又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制/命令信号

2018-09-20 10:29:55

,这个要怎么理解?原来SDRAM在写入或者读取数据的时候是靠上升沿或者下降沿来触发的,请注意,这里仅仅是上升沿或者下降沿,并不是上升沿和下降沿同时有效。如果时钟频率是800MHz,那么对应的数据率就为

2016-11-08 16:59:51

PCB新手在PCB设计中应该注意的问题

2012-08-04 16:42:45

经验,画过通讯、工业控制、嵌入式、数码消费类产品的高速、高密度、数模混合等PCB设计。处理高速信号很有经验,通过对于叠层的控制、信号的分类、拓扑结构的确定、微带线带状线分析、阻抗的控制、时序的分析、平面

2013-03-26 14:52:54

,同时走线过细也使阻抗无法降低,那么在高速(>100MHz)高密度PCB设计中有哪些技巧? 在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意

2012-03-03 12:39:55

平面。特征阻抗控制在50~60 Ω。信号线宽参考具体设计实施细则。信号组与其他非DDR信号间距至少保持在20 mil以上。组内信号应该与DDR时钟线长度匹配,差距至少控制在25 mil内。串联匹配

2017-10-16 15:30:56

阻抗匹配。串行电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于20M的信号,PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号

2019-02-14 14:50:45

布线在设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,布线,线长匹配的基本原则是:地址,控制/命令信号与时钟

2018-09-20 10:59:44

有过孔,因为过孔将增加走线的阻抗变化和信号的反射。其次,如果必须用内层来布设时钟,那么上下层应该使用地平面来减小延迟。再次,如果电源平面上不幸引入时钟噪声会增加PLL抖动,那么在修改PCB设计时可以创建一个

2019-09-11 16:55:26

端接,以缓和对时序与信号完整性的影响。 关于PCB设计中的阻抗匹配问题 问:在高速PCB设计时为了防止反射就要考虑阻抗匹配,但由于PCB的加工工艺限制了阻抗的连续性而仿真又仿不到,在原理图的设计时

2012-07-21 14:42:35

能力,是因为多个时钟负载造成。采用时钟驱动芯片,将一个时钟信号变成几个,采用点到点的连接。选择驱动芯片,除了保证与负载基本匹配,信号沿满足要求(一般时钟为沿有效信号),在计算系统时序时,要算上时钟在驱动

2013-12-27 09:47:22

电流所产生的噪声便会出现在模拟电路区域内。28、在高速PCB设计原理图设计时,如何考虑阻抗匹配问题? 在设计高速PCB电路时,阻抗匹配是设计的要素之一。而阻抗值跟走线方式有绝对的关系,例如是走在表面

2017-01-03 15:10:49

PCB设计相关经验分享及PCB新手在PCB设计中应该注意的问题

2015-03-08 21:25:46

等长是PCB设计的时候经常遇到的问题。存储芯片总线要等长,差分信号要等长。什么时候需要做等长,等长约束条件是什么呢?首先,等长的作用。由于信号在PCB走线上存在延时,正比于信号线的长度。假设PCB

2014-12-01 11:00:33

Ω,差分线控制80Ω~100Ω。 当阻抗数值种类较多时,需要考虑阻抗兼容问题。 DDR3芯片本身可配置内阻为40Ω,某些主芯片的DDR3接口内阻也是按照40Ω设计阻抗的。 那么在PCB设计时

2023-04-12 15:12:13

华秋DFM帮你忙,每日解决一个PCB设计问题【今日问题:孔到线】1、在PCB布局中,孔线之间的间距是极为重要的一环;2、怎么样的间距才是最安全的距离?3、需要注意什么规范才能保证PCB的良好运行?4

2021-05-14 18:00:01

给大家分享一个在快点PCB学院看到的一篇经验总结;非常不错。 应该是一个PCB设计高手的分享。 1、PCB板各层的含义是什么? Topoverlay ----顶层器件名称, 也叫 top

2021-02-05 16:36:39

(芯板)的选择可以是1.2MM也可以是1.0MM,只要层压出来的板厚控制在一定范围内,即可满足成品板厚要求。另外就是板厚公差问题,PCB设计人员在考虑产品装配公差的同时要考虑PCB加工后板厚公差,影响成

2017-06-20 11:08:34

一名程序设计工程师时,我记得,我们花太多的时间在代码设计的检视。但现在回头看,我不得不承认,它们真的是这个过程中非常重要的一部分,这种重要性在PCB设计时也是一样。虽然你可能认为你的设计是完美无瑕的,且犯错

2018-09-17 17:43:59

PCB设计的可制造性分为哪几类?PCB设计时考虑的内容有哪些?

2021-04-21 06:16:30

在pcb设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,,线长匹配的基本原则是:地址,控制/命令信号与时钟做

2018-09-19 16:21:47

在DDR的PCB布线中提到,数据线可以分组等长,各组之间可以不等长,那怎样保证32位数据的时序呢?

2023-04-10 16:49:54

在DDR的PCB布线中提到,数据线可以分组等长,各组之间可以不等长,那怎样保证32位数据的时序呢?

2023-04-11 17:36:23

在PCB设计时,如何设置不同大小的过孔并可以保存,然后在布线放置过孔时能够在之前设置的过孔大小中随意切换?求解,谢谢。

2016-10-13 08:43:45

在进行PCB设计时,需要遵守哪些原则?在设计RF布局时,需要满足哪些原则?

2021-04-21 06:50:45

HDMI接口PCB设计,应该怎么办呢?小编认为,在掌握PCB设计的基础上,你至少需要满足一次具有如下条件的项目实战:l以真实HDMI设计项目的实际案例作为实战对象l该PCB设计项目代表的业务逻辑一定

2019-09-16 14:36:01

LTM4630电源模块在多路并联时在pcb设计时需要注意那些细节

比如在3路或者4路并联时在画pcb时走线需要注意那些地方,要加入对称设计和阻抗匹配吗,

如何才能做到并联均流效果最好,

请大家提出一些建议和指导,谢谢。

2024-01-05 08:07:28

存储器控制器用户指南列出了数据,地址,控制和时钟信号的长度匹配要求。给出的数字是否必须补偿FPGA和DDR2封装内的键合线长度?如果是这样,我在哪里可以找到这些长度?谢谢,TL以上来自于谷歌翻译以下

2019-03-15 10:06:16

我用esp8266 01模块设计了一个电路。在我的最终设计中,我只想使用 esp8266ex 芯片和天线,不包括模块中的闪光灯和晶体。我需要天线设计方面的帮助。天线的阻抗匹配应该怎么做?请帮忙。

2023-05-30 08:10:22

的PCB里,这个就显得不是完全的可行性,由于其信号线是靠近电源平面的,这就使得信号的返回路径是由它们之间的耦合程度来决定的。所以,在4层的PCB设计时,为符合电源完整性(power integrity

2019-07-30 07:00:00

使用Cadence仿真工具进行信号完整性分析获得端接匹配最优方式,通过时序分析获得PCB设计等长约束。进行电源完整性分析优化电源布线布局优化约束。配合热仿真调整优化PCB布局。在板材选型,使用背钻技术等方面让整个系统

2012-04-27 16:01:01

与负载基本匹配,信号沿满足要求(一般时钟为沿有效信号),在计算系统时序时,要算上时钟在驱动芯片内时延。3、2G以上高频PCB设计,走线,排版,应重点注意哪些方面?2G以上高频PCB属于射频电路设计,不在

2018-03-20 21:38:26

在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的。在整个PCB设计中,布线的设计过程限定最高,技巧最细,工作量最大。PCB布线分为单面布线,双面布线以及多层布线3种

2018-12-07 22:50:21

元器件一般情况下尽量集中放置,可以减小线长,降低噪声。但如果是有时序要求限制的信号布线,则需要根据线长和结构进行布局的调整,具体应该通过仿真来确定。旁路电容需要尽量靠近芯片电源引脚放置,尤其是高频电容,在电源接口附近可以放置大容量(如47uF)的电容,以保持电源稳定,降低低频噪声的干扰。

2019-09-12 14:47:17

%-50%的成功率。本次给大家介绍在PCB设计过程中电源平面处理应该考虑的基本要素。1、做电源处理时,首先应该考虑的是其载流能力,其中包含 2 个方面。a)电源线宽或铜皮的...

2021-12-28 06:21:13

电源平面的处理,在PCB设计中占有很重要的地位。在一个完整的设计项目中,通常电源的处理情况能决定此次项目30%-50%的成功率,本次给大家介绍在PCB设计过程中电源平面处理应该考虑的基本要素。 1

2021-12-31 07:17:08

它在时钟触发沿的上、下沿都能进行数据传输,所以即使在133MHz 的总线频率下的带宽也能达到2.128GB/s。它的地址与其它控制介面与SDRAM 相同,DDR不支持3.3V 电压的LVTTL,而是支持

2012-09-17 21:15:33

` 在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的。在整个PCB设计中,布线的设计过程限定最高,技巧最细,工作量最大。PCB布线分为单面布线,双面布线以及多层布线3

2018-11-23 16:07:58

和地层之间的EMC环境较差,应避免布置对干扰敏感的信号。5. 有阻抗控制要求的网络应布置在阻抗控制层上。6. 进行PCB设计时应该遵循的规则1) 地线回路规则:环路最小规则,即信号线与其回路构成的环面

2008-07-08 19:31:09

完整的地和电源平面。

3、为了防止串扰,本组内信号不能和数据信号在同一个电阻排内。

DDR信号等长约束,由于DDR工作频率高,对信号等长有更严格的要求,实际的PCB设计中,对所有信号都进行等长控制是不太

2023-12-25 14:02:58

完整的地和电源平面。

3、为了防止串扰,本组内信号不能和数据信号在同一个电阻排内。

DDR信号等长约束,由于DDR工作频率高,对信号等长有更严格的要求,实际的PCB设计中,对所有信号都进行等长控制是不太

2023-12-25 13:58:55

大家好,我正在研究我的第一个Kintex7 DDR3接口。为了实现RAM,我想在PCB上包含长度匹配的封装走线长度。要获取包延迟信息,我使用了命令(在Vivado中)link_design

2020-08-12 10:17:19

反射、串扰、信号延迟和时序错误。1、反射:信号在传输线上传输时,当高速PCB上传输线的特征阻抗与信号的源端阻抗或负载阻抗不匹配时,信号会发生反射,使信号波形出现过冲、下冲和由此导致的振铃现象。过冲

2018-07-31 17:12:43

在高速PCB设计时为了防止反射就要考虑阻抗匹配,但由于PCB的加工工艺限制了阻抗的连续性而仿真又仿不到,在原理图的设计时怎样来考虑这个问题?另外关于IBIS模型,不知在那里能提供比较准确的IBIS

2012-03-03 12:41:55

的长度数值如最后小结一下,在高速PCB设计中,随着信号速率的逐步提高,时序等长变得尤为重要。这要求快点PCB工程师在设计时不仅仅要考虑到PCB板内信号的走线长度,也要考虑到IC以及连接器(如DIMM

2016-11-09 11:15:00

、Stub、信号匹配(1)时序:总线一般会有传输延时、总线间时序关系(相对延时)的要求,在PCB设计实现时需要考虑:从驱动器到接收器的PCB走线长度、一组总线的PCB布线等长设计;(2)Stub:通俗的说

2016-10-14 16:53:15

我主要感兴趣的方向是单片机,开关电源,还有PCB设计。我应该怎么做来打好基础?我不是电子系出身,但属于工科。

2012-10-16 17:29:11

保持在20 mil以上。组内信号应该与DDR时钟线长度匹配,差距至少控制在25 mil内。串联匹配电阻RS值为O~33 Ω,并联匹配电阻RT值应该在25~68 Ω。本组内的信号不要和数据信号组在同一个

2015-10-21 10:37:10

阻抗匹配阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了。反之则在传输中有能量损失。在高速PCB设计中,阻抗的匹配与否关系到信号

2014-12-01 10:38:55

我看了有些人的板在ddr2地址线加匹配电阻,数据线不加。有的人在数据线加匹配电阻地址线不加,到底应该在那里加的,是参考DDR芯片的手册还是参考TMS320C6748的手册来做?

2019-01-21 13:50:55

我们定义了传输线效应发生的前提条件,但是如何得知线延时是否大于1/2驱动端的信号上升时间? 一般地,信号上升时间的典型值可通过器件手册给出,而信号的传播时间在PCB设计中由实际布线长度决定。下图为信号

2015-05-05 09:30:27

范围,而不是等长。又因为飞行时间的最小时序要求一般都可以满足,也就是第二个公式在很多场合可以忽略不计,带给PCB设计的要求就是符合第一个公式,结论就是走线越短越好。任何因为并不存在时序要求而做的整个总线绕等长,而又为了绕等长而导致这个总线的布线度增加,串扰增加,这样的设计是错误的,失败的例子非常多。

2014-10-21 09:35:50

Ω。信号线宽参考具体设计实施细则。信号组与其他非DDR信号间距至少保持在20 mil以上。组内信号应该与DDR时钟线长度匹配,差距至少控制在25 mil内。串联匹配电阻RS值为O~33 Ω,并联匹配电阻RT

2017-10-27 10:48:26

阻抗匹配阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了。反之则在传输中有能量损失。在高速PCB设计中,阻抗的匹配与否关系到信号的质量优劣。

2019-05-31 08:12:33

。 问:在高速PCB设计中,串扰与信号线的速率、走线的方向等有什么关系?需要注意哪些设计指标来避免出现串扰等问题? 答:串扰会影响边沿速率,一般来说,一组总线传输方向相同时,串扰因素会使边沿速率变慢

2019-01-11 10:55:05

是。给需要的网络赋予该规则,在工作薄顶端就是Match Group组。以上便是PCB设计中约束管理器的匹配群组建立,上图为完整的DDR数据组Match Group。

2017-07-27 11:06:26

数字系统对时序要求严格,为了满足信号时序的要求,对PCB上的信号走线长度进行调整已经成为PCB设计工作的一部分。调整走线长度包括两个方面:相对的和绝对的。 所谓相对的就是要求走线长度保持一致

2018-11-27 15:22:54

PCB设计时,注意控制走线时的阻抗控制,往往可以做到很好的匹配。 对于通常的聚酯胶片PCB 来说,传输线的长度和微带线 Stub 效应是需要考虑的, 在本设计指南里面,主要是针对 4 层的 1080+2116 聚酯胶片PCB 进行相关的阻抗匹配控制。

2019-05-17 10:40:14

挑战。

在高速PCB设计中,阻抗匹配显得尤为重要,为减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗的匹配。

一般而言,单端信号线的阻抗取决于它的线宽以及与参考平面之间

2023-05-26 11:30:36

介绍采用Protel99 SE进行射频电路PCB设计的流程。为保证电路性能,在进行射频电路PCB设计时应考虑电磁兼

2006-04-16 22:17:22 1352

1352 PCB设计时应该遵循的规则

1) 地线回路规则:

环路最小

2007-12-12 14:48:15 1096

1096

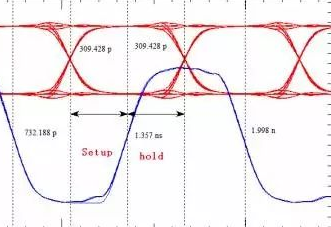

对于广大PCB设计工程师而言,提到时序问题就感觉比较茫然。看到时序图,更是一头雾水,感觉时序问题特别深奥。其实在平常的设计中最常见的是各种等长关系,网上流传的Layout Gu

2012-10-22 11:51:56 4104

4104

PCB设计相关经验分享及PCB新手在PCB设计中应该注意的问题

2013-09-06 14:59:47 0

0 DDR4 PCB设计规范&设计要点,DDR4 PCB设计规范&设计要点

2016-07-26 14:09:33 0

0 详细介绍PCB设计时需要遵守的规则

2017-09-18 14:08:17 0

0 DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制

2017-11-28 11:34:58 0

0 DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制/命令信号与时钟做等长。

2018-09-27 09:56:00 6660

6660

本文档的主要内容详细介绍的是Allegro PCB设计时等长设置的一些方法与技巧解析。以DDR3(4pcs,fly-by 结构)为例,讲述一下在allegro 中如何添加电气约束(时序等长)。

2018-11-27 16:02:57 0

0 时序问题最为重要,目前PCB设计者基本上采用核心芯片厂家现成方案,因此PCB设计中主要一部分工作是如何保证PCB能够符合芯片工作要求时序。,目前国内用户基本没有掌握时序问题。少数SQ用户会采用

2019-04-22 13:54:36 2984

2984 在高速PCB设计时为了防止反射就要考虑阻抗匹配,但由于PCB的加工工艺限制了阻抗的连续性而仿真又仿不到,在原理图的设计时怎样来考虑这个问题?

2019-06-21 17:03:47 6432

6432 安规是产品认证中对产品安全的要求,包括产品从设计到销售到终端用户整个过程。在PCB设计上,布线应该满足爬电距离与电气间隙的要求,布线宽度也应该具备足够的通流能力。以下是PCB设计中的一些安规考虑。

2019-07-06 11:38:04 8346

8346 PCB设计时记住148个检查项目,提升你的效率!

2019-08-20 08:42:08 3177

3177 为了保证线路板设计时的质量问题,在PCB设计的时候,要注意PCB图布线的部分是否符合要求。

2019-09-02 10:12:36 2190

2190 数据信号与DQS做等长。为啥要做等长?大家会说是要让同组信号同时到达接收端,好让接收芯片能够同时处理这些信号。

2020-01-06 15:23:00 1414

1414 DDR布线在pcb设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的裕量。要保证系统的时序,线长又是一个重要的环节。

2020-01-14 14:46:10 1188

1188 如果您阅读了许多PCB设计指南,尤其是有关并行协议和差分对布线的指南,则将看到很多关于走线长度匹配的内容。当您需要进行迹线长度匹配时,您的目标是最大程度地减少串行协议中的差分对,并行协议中的多个

2021-01-05 10:56:22 3656

3656

在高速PCB设计时为了防止反射就要考虑阻抗匹配,但由于PCB的加工工艺限制了阻抗的连续性而仿真又仿不到,在原理图的设计时怎样来考虑这个问题?

2020-11-12 17:09:06 4684

4684 点击上面蓝色字体,关注我们! PCB设计时DDR线宽和阻抗是如何确定下来的呢? 让我们通一个具体的项目来学习一下。

2020-12-07 12:23:02 8681

8681 本文章主要涉及到对DDR2和DDR3在PCB设计时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。 文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中

2021-03-25 14:26:01 3864

3864

为什么PCB设计时要考虑热设计? PCB(Printed Circuit Board)设计是指通过软件将电路图转化为PCB布局图,以导出一个能够输出到电路板的文件。在进行电路设计时,我们需要考虑到

2023-10-24 09:58:27 331

331 什么是阻抗匹配?高速PCB设计为什么要控制阻抗匹配? 阻抗匹配是指在电路传输信号时,控制电路中信号源、传输线和负载之间的阻抗相等的过程,从而确保信号的完整性和可靠性。在高速PCB设计中,阻抗匹配

2023-10-30 10:03:25 924

924 PCB设计时铜箔厚度,走线宽度和电流的关系

2022-12-30 09:20:39 15

15 PCB设计时铜箔厚度,走线宽度和电流的关系

2023-03-01 15:37:46 13

13 pcb板阻抗控制是指什么?pcb怎么做阻抗? PCB板阻抗控制是指在PCB(印刷电路板)设计和制造过程中,通过优化电气特性和信号完整性,确保设计满足特定的阻抗要求。在高速数字和模拟电路中,阻抗控制

2024-01-17 16:38:04 722

722

电子发烧友App

电子发烧友App

评论