引言

对于应用0.18mm及以下工艺的设计而言,二维提取进行Sign-off静态时序分析就显得有些粗略,而且精度不够。这是因为对于0.18mm及以下工艺,毗邻金属连线所产生的耦合电容在设计中已经成为不得不考虑的寄生参数,于是先进的寄生参数提取工具就可以检测到相同层次之间产生耦合电容的影响。因此对0.18mm及以下工艺的设计,通过物理验证,在进行流片之前,需要用专门的寄生参数抽取工具将每一个节点的RC网络信息写成文件传递给设计,即所谓的反标,再用静态时序分析工具做精确的版图时序分析。

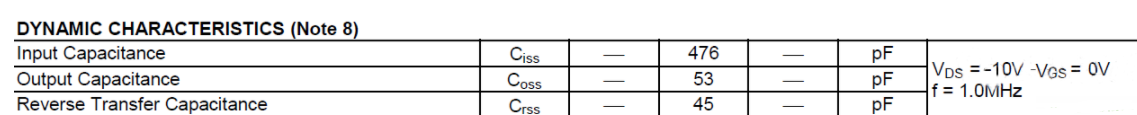

Star-RCXT工具介绍

Star- RCXT以其高精度、友好的用户界面以及和其它工具良好的结合成为目前业界比较流行的一款寄生参数提取工具,是专门针对0.18mm及以下工艺的寄生参数提取所设计的。它采用了二点五维的几何提取技术,达到了三维的提取精度,但比三维的抽取工具速度快很多,能够快速准确地对上百万门的设计进行全局的寄生参数提取。

用Star-RCXT进行寄生参数提取的条件

应用Star-RCXT进行精细寄生参数提取,还需要两个与工艺参数有关的文件:mapping文件和ITF(Interconnect Technology Format)文件。ITF文件是由晶圆代工厂直接提供的,它包含的信息主要有:工艺采用的各个层次(包括电介质、过孔和金属导线等),各个层次在工艺流程中的厚度、宽度等物理尺寸,各个层次的电气参数(如介电常数、方块阻值等)。Star-RCXT不能直接使用ITF格式的文件,它提供grdgenxo 命令将晶圆代工厂提供的ITF格式文件转换成Star-RCXT所需要的.nxtgrd格式文件,Mapping文件用于实现这种转换过程,将目标.nxtgrd文件中各个层次名称与设计数据库中的层名称相对应起来。

Star-RCXT支持的格式

寄生参数提取工具Star-RCXT支持多种格式输入,主要有Milkyway、Lef/Def、Hercules和Calibre格式。也支持多种格式输出,如输出格式为IEEE 1481标准的SPEF(Standard Parastic Exchange Format)格式;输出与PrimeTime静态时序分析工具最有效对接的SBPF(Synopsys Binary Parasitic Format)格式;输出格式包含了每一个节点RC网络信息的DSPF (Detailed Standard Parasitic Format)格式;还有STAR、NETNAME、MW、CONLY等格式。因为寄生电容值与其毗邻的金属连线有密切关系,版图上一个图形有可能会影响到其相邻模块中某一条连线的寄生参数提取,因此寄生参数提取是针对flat版图,提取出来的寄生参数信息是不带有层次的。也正是由于这个原因,寄生参数提取一般需要花费较长的时间,并占用较大的硬件资源。

Primetime工具介绍

PrimeTime 是Synopsys公司提供的一个针对复杂全芯片进行静态时序分析的工具。PrimeTime可以集成于逻辑综合和物理综合的流程,让设计者分析并解决复杂的时序问题,提高时序收敛的速度。它是一种穷尽分析方法,不依赖于激励,分析检查电路或设计对象中的所有时序路径,包括无效路径,能够保证100%的覆盖率。它运行速度快,占用内存少,完全克服了动态时序验证的缺陷,适用于超大规模芯片系统的电路验证。

PrimeTime分析原理

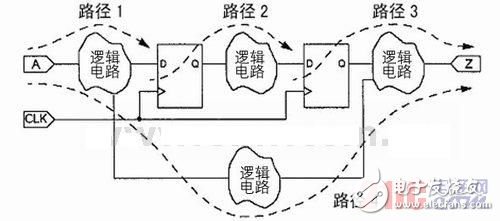

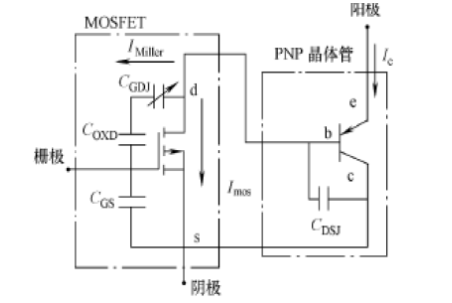

PrimeTime 进行静态时序分析时把整个芯片按照时钟分成许多时序路径。路径的起点是时序单元的输出引脚或是设计的输入端口,路径的终点是时序单元的输入引脚或是设计的输出端口。根据起点和终点的不同,可将逻辑电路分解为图1中用虚线表示的四种路径,分别代表了以下四种类型: 路径1起始于输入端口,终止于时序单元的数据输入端;路径2起始于时序单元的时钟引脚,终止于时序单元的数据输入端;路径3起始于时序单元的时钟引脚,终止于输出端口;路径4起始于输入端口,终止于输出端口。

图1 逻辑电路中的四种时序路径

PrimeTime 工具把设计打散成一系列时序路径之后,沿每条路径计算延时。路径的总延时是该路径中所有单元延时和连线延时的和。单元延时为路径中从逻辑门的输入到输出的延时量,若没有提供反标延时信息,PrimeTime会根据工艺库中提供的此单元延迟表来计算单元延时。典型的单元延迟表是输入传输时间和输出负载电容的函数,基于二维表格来计算每个单元的延时。对于在表格中找不到对应点的情况,可通过内插或外推表格中的值来获得当前条件下的延时值。连线延时是时序路径中从一个单元的输出到下一个单元输入的延时总和。PrimeTime可读取由专门提取工具得到的详细内部互联网络的寄生电容和电阻值,并基于此精确地计算连线延时,以完成精确的版图时序分析。

PrimeTime分析要求

静态时序分析的目的是保证设计中的以上四种类型路径可以满足建立时间和保持时间的要求。即无论其起点是什么,信号都可以被及时地传递到该路径的终点,并且在电路正常工作所必需的时间段内保持恒定。如果建立时间和保持时间不能得到满足,触发器就无法采样到正确的数据。

对FFT处理器进行寄生参数提取和静态时序分析

当 FFT处理器完成版图设计,通过Calibre DRC和LVS进行Sign-off的静态时序分析时,可用专门的寄生参数提取工具Star-RCXT将每一个节点的RC网络信息写成文件传递给设计,再用静态时序分析工具PrimeTime读取由Star-RCXT工具得到的详细内部互联网络的寄生电容和电阻值,并基于此精确地计算连线延迟,做精确的版图时序分析。

对FFT处理器进行寄生参数提取

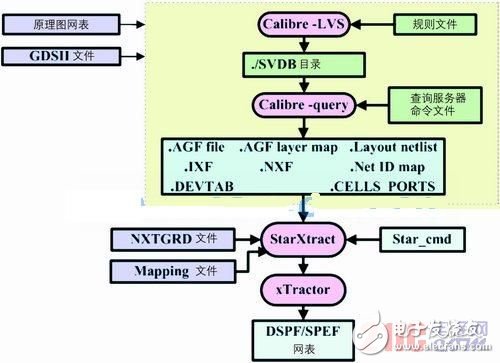

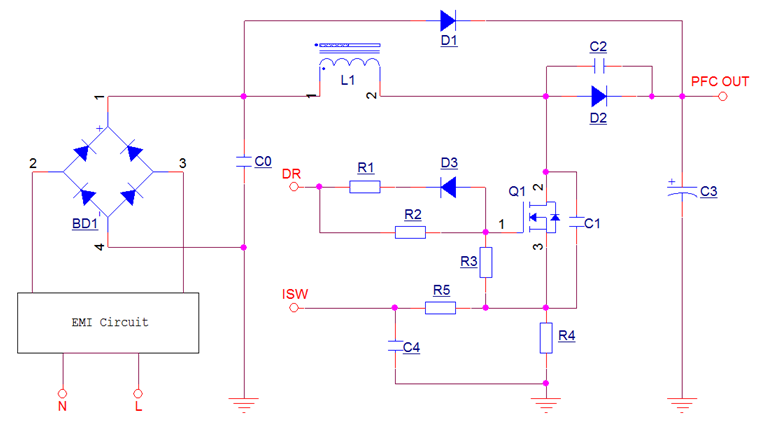

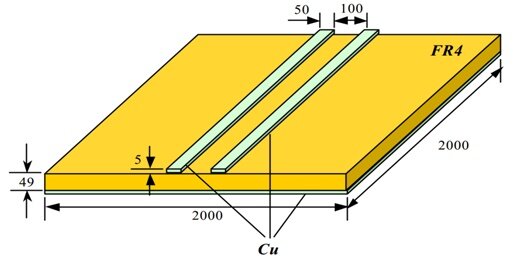

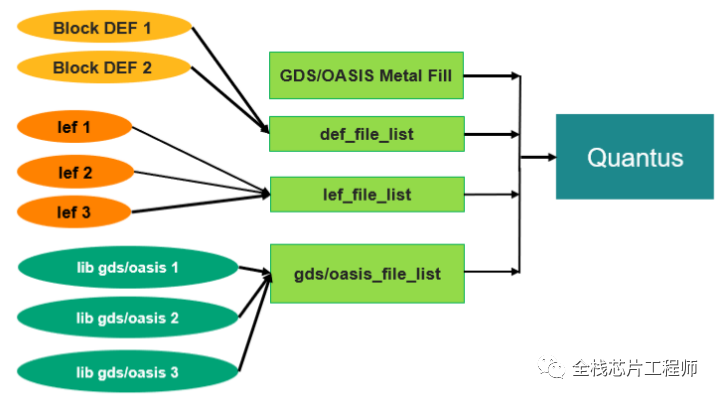

由于FFT项目采用Mentor公司的 Calibre工具进行DRC和LVS,因此寄生参数提取工具Star-RCXT采用的输入格式为Calibre,基于CCI(Calibre Connectiity Interface)的Star-RCXT寄生参数提取流程如图2所示。

图2 基于CCI的寄生参数提取流程

在 Calibre中采用flat方式对FFT处理器进行LVS,通过LVS后自动产生SVDB目录,并将配置LVS运行时设置的内容保存为lvsset文件。然后编写query.cmd文件,该文件指定基于CCI的Star-RCXT寄生参数提取所需文件的位置,如标注的GDSII版图、层映射信息、顶层端口信息、理想版图网表、网络名信息、交互表等。编写好query.cmd文件后,在calibredrv工具的命令行中执行命令:Calibre- query svdb

本设计用运行Star-RCXT命令文件(star.cmd)来进行寄生参数提取,在编写star.cmd命令文件时要输入:模块名称xtalkdetailDRCLVS、层映射文件SmicVTMP_LO_SRAM _MR_MM_HV_LC_018.map、电源/地网络名称VDD和GND、加工工艺文件smic018.nxtgrd、提取参数的输出格式SPEF、提取网络的范围、是否要将耦合电容折算成对地电容、配置LVS运行的设置文件lvsset和指定进行基于CCI寄生参数提取所需文件位置的文件 query.cmd等。然后在Star-RCXT中运行StartXtract -clean star.cmd命令即可完成寄生参数提取,输出文件名为xtalkdetailDRCLVS.spef。

对FFT处理器进行静态时序分析

首先在PrimeTime的启动文件(.synopsys_pt.setup)中设置与库文件相关的信息,如用set_link_library { * smic18_ss.db smic18IO_line_ss.db}命令来设置链接库,用set target_library {* smic18_ss.db smic18_IO_line_ss.db}命令来设置目标库、用set_min_library命令来指定工艺库用于最大延迟和最小延迟分析等。然后用 primetime命令启动PrimeTime的图形用户界面,对FFT处理器进行Sign-off的静态时序分析。具体流程包括:读入设计数据、约束时序、设定环境和分析条件、检查设计数据和分析设置参数,以及执行分析和检查结果5步。

读入设计数据

读入网表文件用read_verilog命令,读入由Star-RCXT提取输出的SPEF格式寄生网表用read_parasitics命令。若要分析建立时间则要读入最坏情况的寄生电容和电阻信息,若要分析保持时间则要读入最好情况的寄生电容和电阻信息。

约束时序

进行Sign-off静态时序分析时,由于现在的网表中已经包括了实际的时钟信息,用create_clock命令来定义一个时钟的基本信息,如周期、波形等,将该时钟信号在实际的时钟树中传播,进而得到实际的时钟延时和偏移。用set_propagated_ clock命令可以根据时钟树,自动计算出时钟信号到达终点的延时和偏移。Sign-off静态时序分析可不设置时钟的确定性,但有时为了提高设计可靠性,用set_clock_uncertainty命令对建立时间和保持时间都设置一个很小时间值。根据设计规范要求用set_input_delay命令直接设置输入延时值,用set_output_delay命令直接设置输出延时值等。

设定环境和分析条件

PrimeTime 中set_operating_conditions命令用来根据工艺库指定工艺、温度和电压的工作条件。分析建立时间时工作条件应当在最坏情况进行,即 set_operating_conditions worst;分析保持时间时工作条件应当在最好情况进行,即set_operating_conditions best。用set_load命令设置输出端口的负载,用set_driving_cell命令指定输入端口的驱动单元等。另外可用 set_case_analysis命令在某个端口设置为固定逻辑常数或逻辑转换限制该信号在设计中传播,如果在时序分析时不考虑扫描链的影响,可执行 set_case_analysis 0 [get_ports scan_en_pad]命令。

检查设计数据和分析设置参数

在进行时序分析前要先检查设计数据,如层次、库、端口、单元等,以及分析设置参数,如时钟、输入延迟约束、输出延迟约束等是否已经设置或设置是否正确。如, 用check_timing命令来检查是否存在未定义的时钟、未定义的输入到达时间和未定义的输出约束等;用report_design命令输出当前设计的一系列属性,如分析类型、所选的工作条件、线负载模型和设计规则等;用report_port命令显示端口名、引脚电容、线电容和输入输出延迟等端口信息。

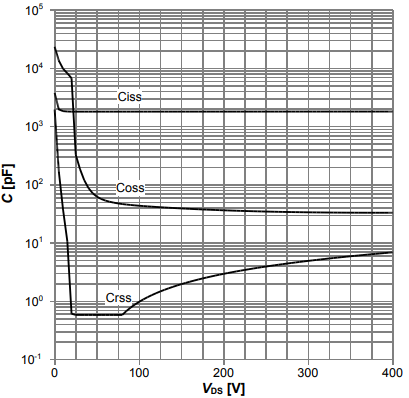

执行分析和检查结果

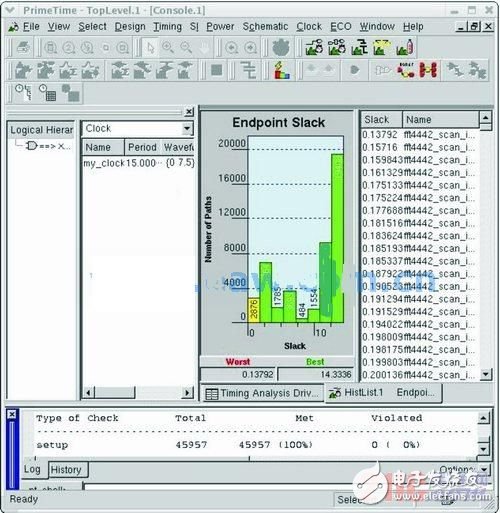

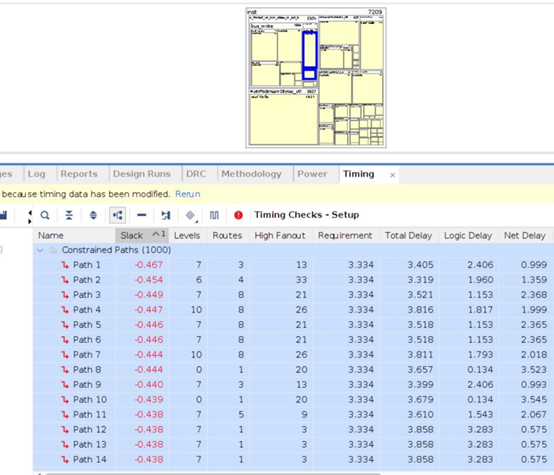

在设计数据和参数设置均正确的情况下进行时序分析,然后查看分析结果,获得设计具体的时间信息。如用report_timing命令产生一条最大时延路径的详细报告,包括路径信息(工作条件、线负载模型的模式、路径起点、路径终止点和路径类型等)、路径延时、路径延时要求和总结部分。用report_constraint-all_violator命令报告所有的建立时间时序违规。为了准确了解FFT处理器所有路径的建立时间情况,可执行菜单命令Timing→Histogram→Endpoint Slack…弹出Endpoint Slack对话框,在Delay type中选择max后按OK可得如图3所示的所有路径建立时间情况,从中可知建立时间最小值为0.13792,满足建立时间要求。再运行命令 report_analysis_coverage得PrimeTime分析的路径条数为45957,分析的覆盖率为100%,建立时间的违规率为0%。

图3 建立时间的分析结果

为了准确了解FFT处理器所有路径的保持时间情况,可进行与分析建立时间过程相同的步骤。

结语

静态时序分析已经成为数字集成电路设计必不可少的环节。本文应用寄生提取工具Star-RCXT基于CCI流程对FFT处理器进行寄生参数提取,再用静态时序分析工具PrimeTime读取由Star-RCXT抽取工具得到的内部互连网络的详细寄生电容和电阻值,进行精确的版图时序分析。它不需要输入测试向量就能覆盖所有的路径,且运行速度很快,占用内存较少,可以对芯片设计进行全面的时序验证。

电子发烧友App

电子发烧友App

评论