在《数字电路之如雷贯耳的“逻辑电路”》、《数字电路之数字集成电路IC》之后,本文是数字电路入门3,将带来「时序电路」的讲解,及其核心部件触发器的工作原理。什么是时序电路?

2016-08-01 10:58:48 18171

18171

时序电路 首先来看两个问题: 1.为什么CPU要用时序电路,时序电路与普通逻辑电路有什么区别。 2.触发器、锁存器以及时钟脉冲对时序电路的作用是什么,它们是如何工作的。 带着这两个问题,我们从头了解

2020-11-20 14:27:09 3998

3998

对于绝大部分的电路来说输出不仅取决于当前的输入值,也取决于原先的输入值,也就是说电路具有记忆功能,这属于同步时序电路。

2020-12-07 15:00:15 6297

6297

数字电路根据逻辑功能的不同特点,可以分成两大类:一类叫做组合逻辑电路,简称组合电路或组合逻辑;另一类叫做时序逻辑电路,简称时序电路或时序逻辑。

2022-12-01 09:04:04 459

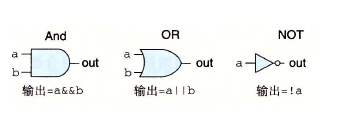

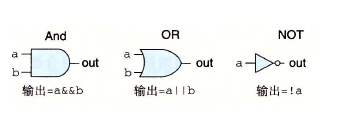

459 数字逻辑电路分为组合逻辑电路和时序逻辑电路。时序逻辑电路是由组合逻辑电路和时序逻辑器件构成(触发器),即数字逻辑电路是由组合逻辑和时序逻辑器件构成。

2023-03-21 09:49:49 476

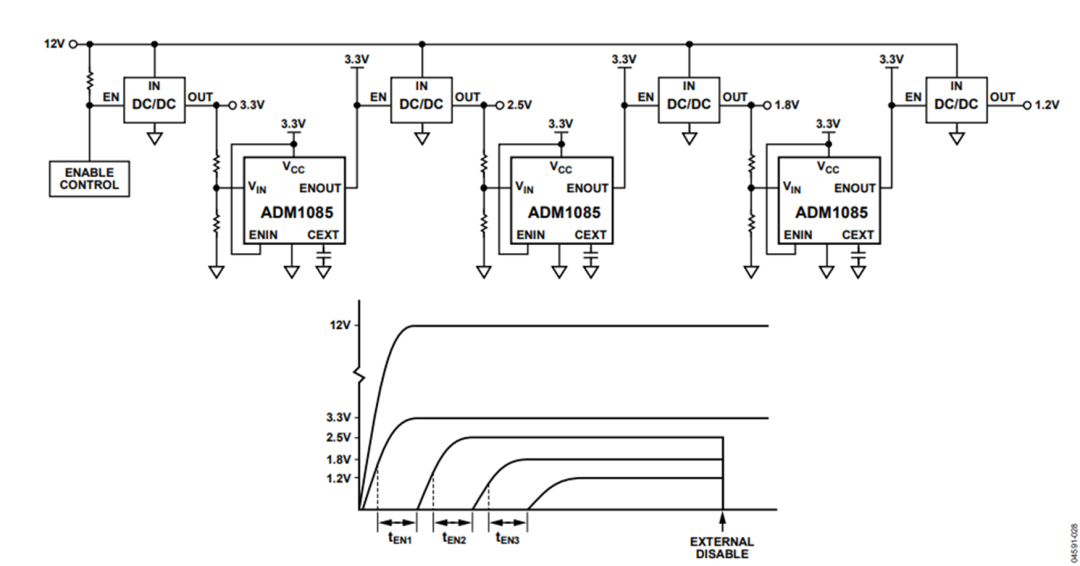

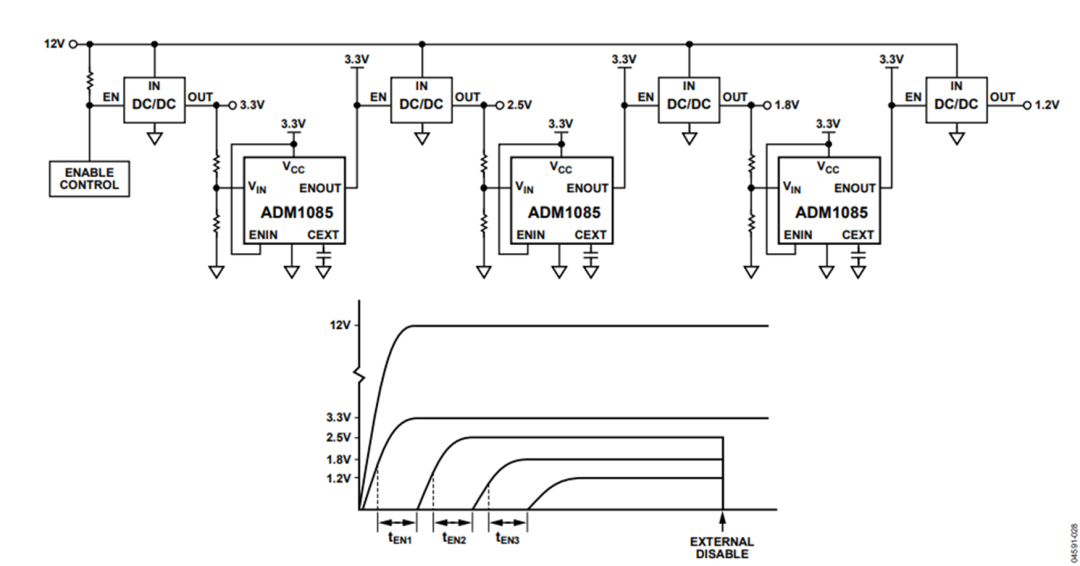

476 上电时序(Power-up Sequeence)是指各电源轨上电的先后关系。 与之对应的是下电时序,但是在电路设计过程中,一般不会去考虑下电时序(特殊的场景除外)。今天,我们主要了解一下上电时序控制相关内容。

2023-12-11 18:17:05 784

784

什么是中断?为什么CPU要用时序电路?时序电路与普通逻辑电路有什么区别呢?

2021-10-29 07:03:45

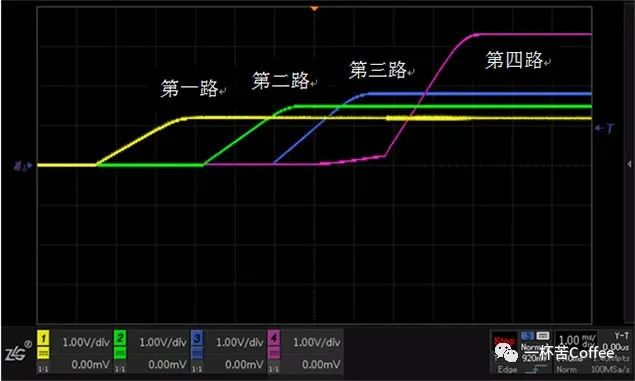

时序电路测试及应用一、实验目的1.掌握常用时序电路分析,设计及测试方法。2.训练独立进行实验的技能.二、实验仪器及材料1.双踪示波器 2.

2009-08-20 18:55:27

逻辑电路分为组合逻辑电路和时序逻辑电路。第四章已经学习了组合逻辑电路的分析与设计的方法,这一章我们来学习时序电路的分析与设计的方法。在学习时序逻辑电路时应注意的重点是常用时序部件的分析与设计这一

2018-08-23 10:28:59

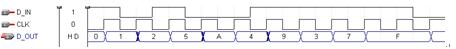

时序逻辑电路设计之计数器实验目的:以计数器为例学会简单的时序逻辑电路设计实验平台:芯航线FPGA核心板实验原理: 时序逻辑电路是指电路任何时刻的稳态输出不仅取决于当前的输入,还与前一时刻输入形成

2019-01-24 06:35:16

要求: 完成占空比(高电平占一个时钟周期的比例)为0.25的8分频电路模块的Verilog设计,并且设计一个仿真测试用的Verilog程序,从时序上验证分频电路模块的正确性。 整数

2018-10-12 16:52:21

时间的重要性不言而喻,加上时间这个维度就如同X-Y的平面加上了一个Z轴,如同打开了一个新的世界。所以今天我们就要来聊聊时序电路。在时序电路中,电路任何时刻的稳定状态输出不仅取决于当前的输入,还与前

2021-07-04 08:00:00

Verilog 设计初学者例程一 时序电路设计 By 上海 无极可米 12/13/2001 ---------基础-----------1. 1/2分频器module halfclk(reset

2018-08-23 13:43:31

什么是时序电路?时序电路核心部件触发器的工作原理

2021-03-04 06:32:49

什么是时序电路?SRAM是触发器构成的吗?

2021-03-17 06:11:32

在传统设计中,所有计算机运算(算法、逻辑和存储进程)都参考时钟同步执行,时钟增加了设计中的时序电路数量。在这个电池供电设备大行其道的移动时代,为了节省每一毫瓦(mW)的功耗,厂商间展开了残酷

2018-09-30 16:00:50

实验二 基本时序电路设计(1)实验目的:熟悉QuartusⅡ的VHDL文本设计过程,学习简单时序电路的设计、仿真和硬件测试。(2)实验内容:Ⅰ.用VHDL设计一个带异步复位的D触发器,并利用

2009-10-11 09:21:16

根据波形图设计异步时序电路 急 求大神

2017-12-08 23:07:44

本文利用CPLD数字控制技术对时序电路进行改进。CPLD(Complex Programmable Logic Device)是新一代的数字逻辑器件,具有速度快、集成度高、可靠性强、用户可重复编程或

2021-05-06 09:44:24

计数器及时序电路原理及实验 一、实验目的1、了解时序电路的经典设计方法(D触发器、JK触发器和一般逻辑门组成的时序逻辑电路)。 &

2009-10-10 11:47:02

设计一个同步时序电路:只有在连续三个或者三个以上时针作用期间两个输入信号相同时,其输出为1,其余情况下输出为0。

2013-03-22 10:44:50

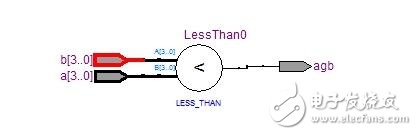

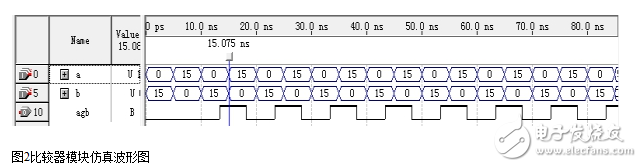

多输入时序电路的基本原理是什么?基于数据选择器和D触发器的多输入时序逻辑电路设计

2021-04-29 07:04:38

PLD练习2(时序电路)

2006-05-26 00:14:19 20

20 [学习要求]可利用简单的VHDL语法进行简单组合逻辑电路和时序逻辑电路的设计。[重点与难点]重点:基于真值表的组合逻辑电路的设计; 基于状态机的时序电路的设计。

2009-03-18 22:04:38 51

51 时序逻辑电路的输出不但和当前输入有关,还与系统的原先状态有关,即时序电路的当前输出由输入变量与电路原先的状态共同决定。为达到这一目的,时序逻辑电路从某一状态

2009-03-18 22:13:04 71

71 组合逻辑电路(简称组合电路)任意时刻的输出信号仅取决于该时刻的输入信号,与信号作用前电路原来的状态无关时序逻辑电路(简称时序电路)任意时刻的输出信号不仅取决

2009-07-15 18:45:58 0

0 时序电路测试生成算法产生的向量存在冗余。针对此问题提出一种压缩算法,减少测试序列的总长度,从而减少了仿真的时间和ATE 设备的测试的时间,加速了测试的流程。实验结果

2009-08-29 11:00:38 8

8 时序电路设计实例 (Sequential-Circuit Design Examples):We noted in previous chapters that we typically deal

2009-09-26 13:01:04 37

37 为解决TDI-CCD 作为遥感相机的图像传感器在使用中所面临的时序电路设计问题,文中较为详细地介绍了TDI-CCD 的结构和工作原理,并根据工程项目所使用的ILE2TDI-CCD 的特性,设

2010-01-12 09:54:50 21

21 摘要:通用教材<数字电子技术>中介绍的传统的时序电路设计方法——状态表及状态图法过于简单,很难满足较复杂电路的设计要求。介绍一种新的方法——MDS图法,该方法具有

2010-04-28 08:38:27 20

20 摘要:分析了“数字电路与逻辑设计”课程中“一般时序电路设计”的内容的地位与作用,指出传统教学方法在设计较复杂电路时的局限性,为此完善了教材对该部分内容的讲解,

2010-05-08 08:42:54 0

0 摘要:针对同步时序电路的初始化问题,提出了一种新的实现方法。当时序电路中有未确定状态的触发器时,就不能顺利完成该电路的测试生成,因此初始化是时序电路测试生成中

2010-05-13 09:36:52 6

6 本文介绍将量子进化算法应用在时序电路测试生成的研究结果。结合时序电路的特点,本文将量子计算中的量子位和叠加态的概念引入传统的测试生成算法中,建立了时序电路的量

2010-08-03 15:29:01 0

0 本章内容:q 镜像电路q 准nMOS电路q 三态电路q 钟控CMOS电路q 动态CMOS电路q 双轨逻辑电路q 时序电路

2010-08-13 14:44:30 0

0 数字电路分为组合逻辑电路(简称组合电路)和时序逻辑电路(简称时序电路)两类。在第三章中讨论的电路为组合电路。组合电路的结构模型如图4.1所示,它的输出函数表达式为

2010-08-13 15:23:02 24

24 在讨论时序逻辑电路的分析与设计之前,让我们先回顾一下在第四章中介绍过的时序电路结构框图和一些相关术语。时序电路的结构框图如图5.1所示.。

2010-08-13 15:24:35 69

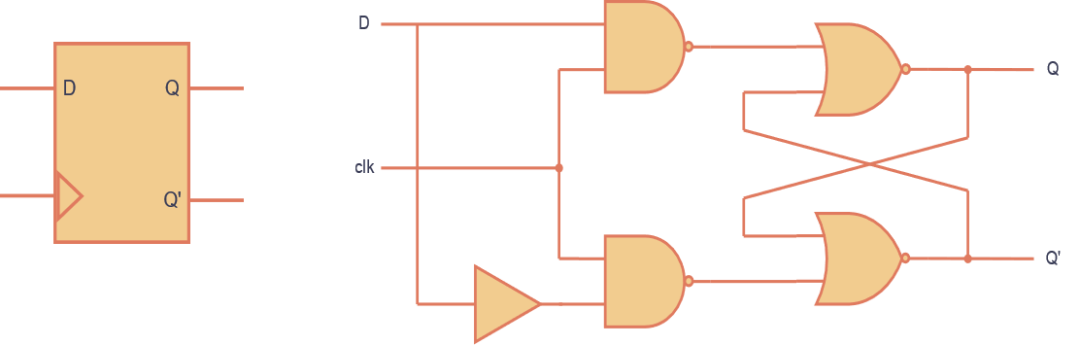

69 组合电路和时序电路是数字电路的两大类。门电路是组合电路的基本单元;触发器是时序电路的基本单元。

2010-08-29 11:29:04 67

67 实验八、VHDL语言的组合电路设计一 实验目的1掌握VHDL语言的基本结构及设计的输入方法。2掌握VHDL语言的组合电路设计方法。二 实验设备与仪器

2009-03-13 19:26:58 2368

2368

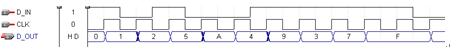

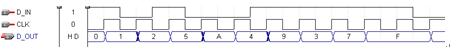

时序电路设计串入/并出移位寄存器一 实验目的1掌握VHDL语言的基本描述语句的使用方法。2掌握使用VHDL语言进行时序电路设计的方法。

2009-03-13 19:29:51 5733

5733

时序电路设计串入/并出移位寄存器一 实验目的1掌握VHDL语言的基本描述语句的使用方法。2掌握使用VHDL语言进行时序电路设计的方法。

2009-03-13 19:29:52 2024

2024

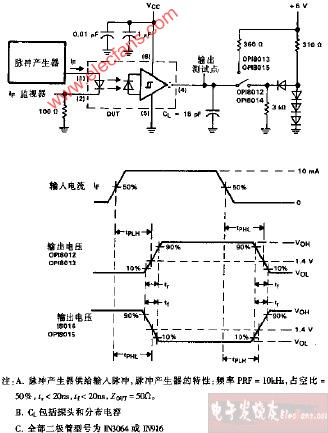

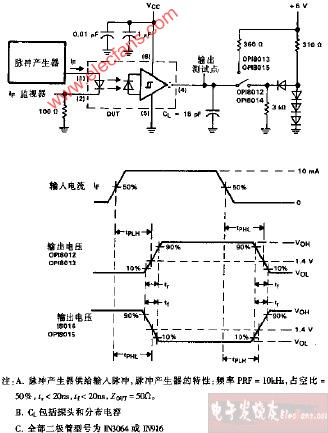

OPI812-OP1815开关时序电路及波形电路图

2009-07-01 11:22:24 962

962

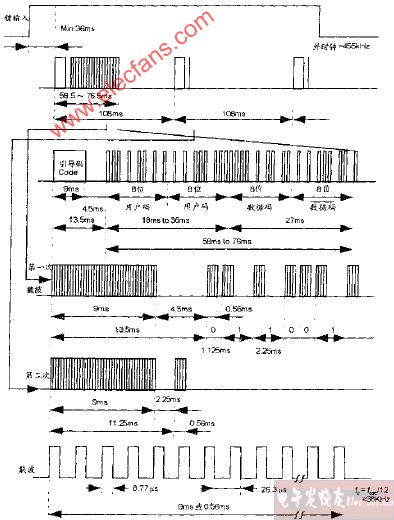

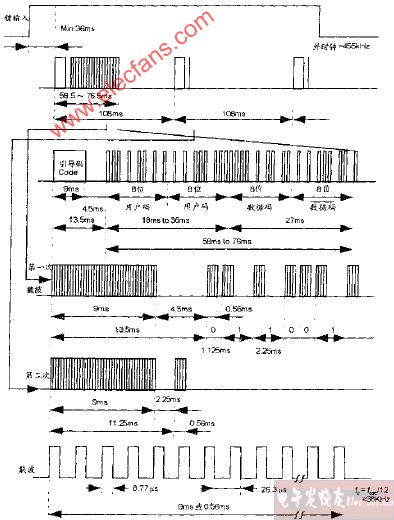

BLO508 A1输出波形,单键操作时序电路图

2009-07-02 10:54:11 542

542

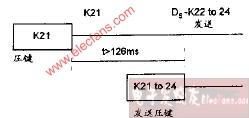

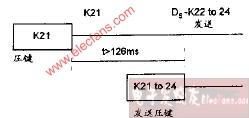

BLO508 A1型双键操作时序电路图

2009-07-02 10:56:00 526

526

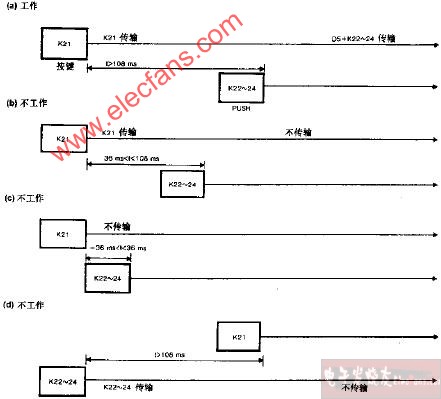

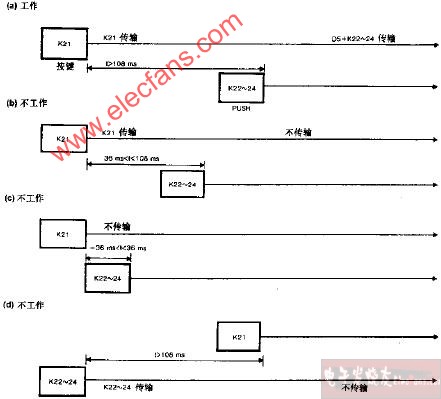

GM3043双键工作时序电路图

2009-07-02 11:07:30 424

424

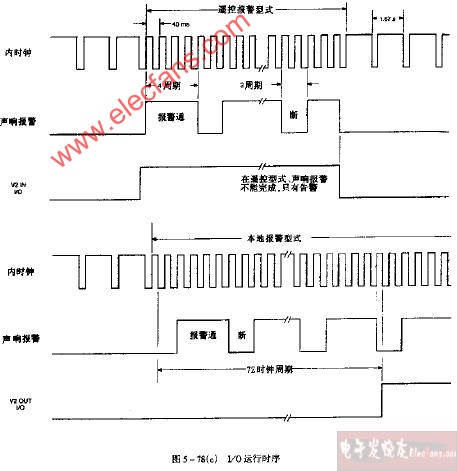

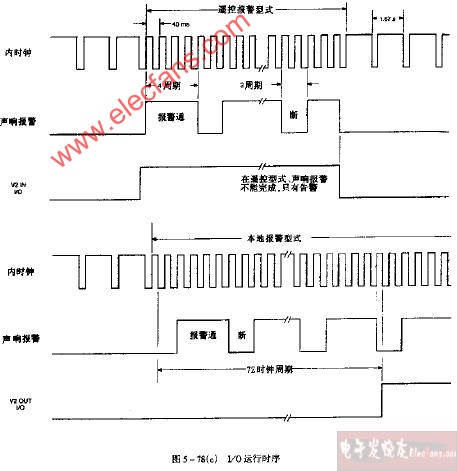

A5347 IO运行时序电路图

2009-07-03 12:03:29 440

440

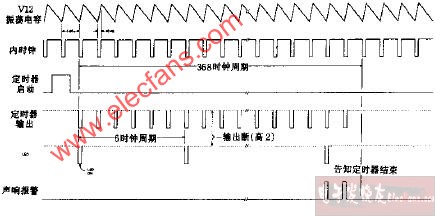

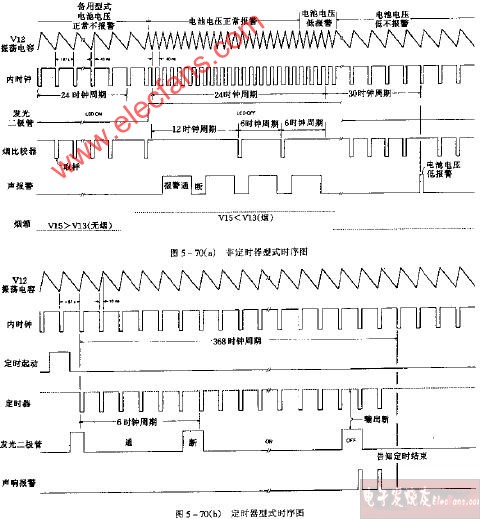

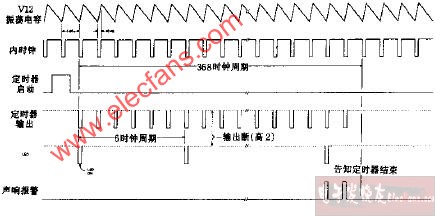

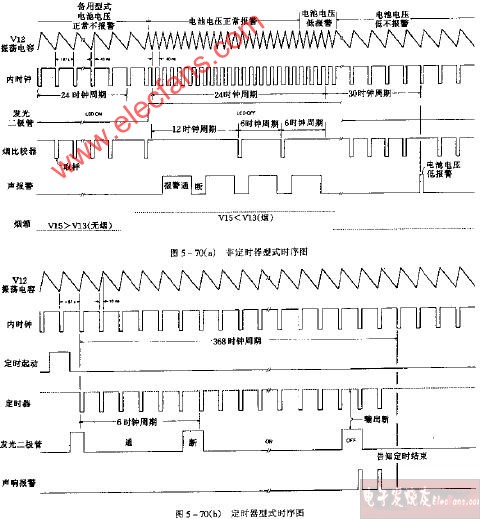

A5347定时器型时序电路图

2009-07-03 12:09:08 546

546

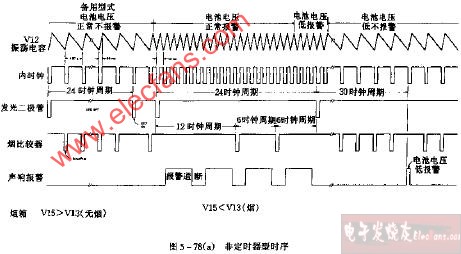

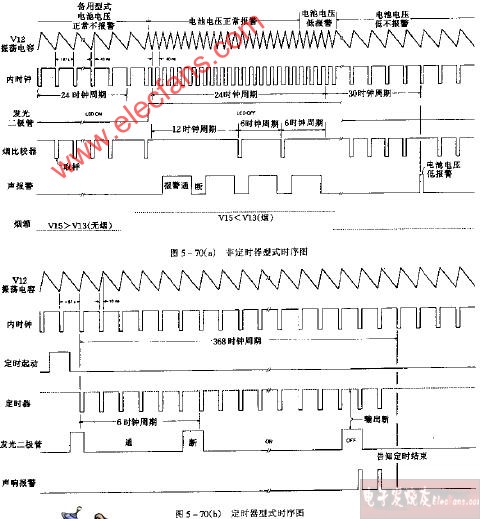

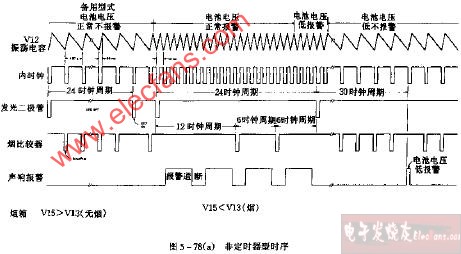

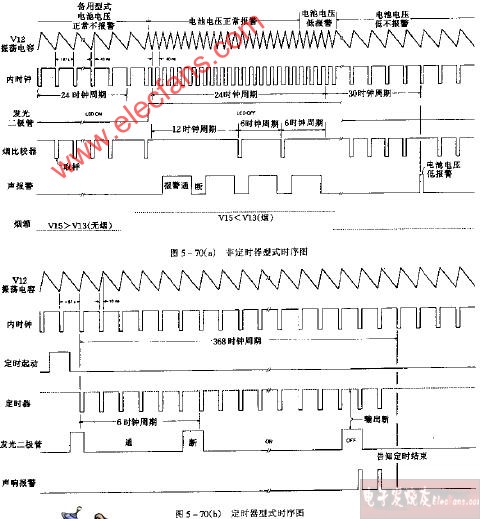

A5347非定时器型时序电路图

2009-07-03 12:09:32 450

450

A5348 IO运行时序电路图

2009-07-03 12:11:10 393

393

0

A5348定时器型时序电路图

2009-07-03 12:12:17 413

413

A5348非定时器型时序电路图

2009-07-03 12:12:59 453

453

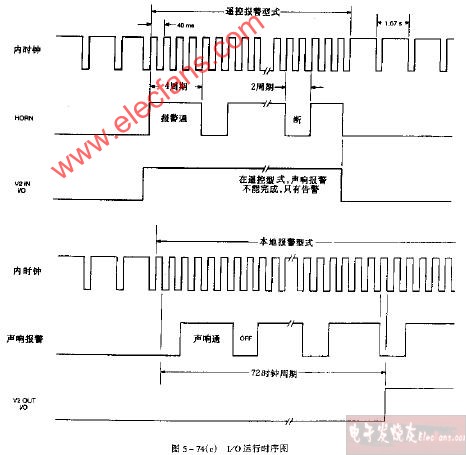

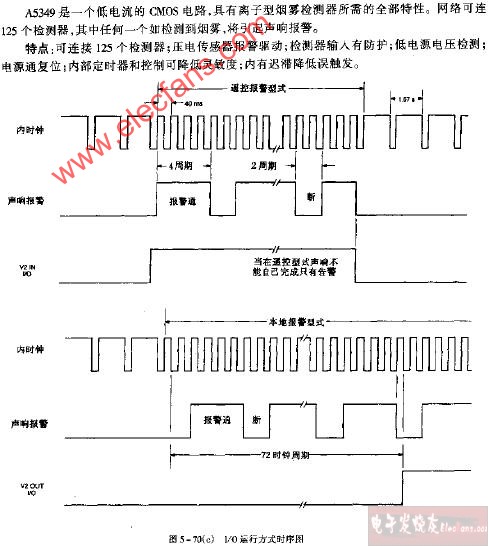

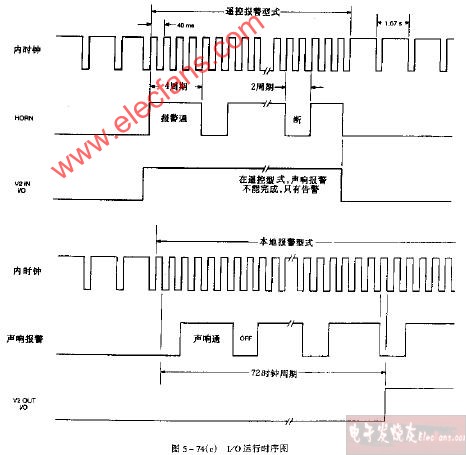

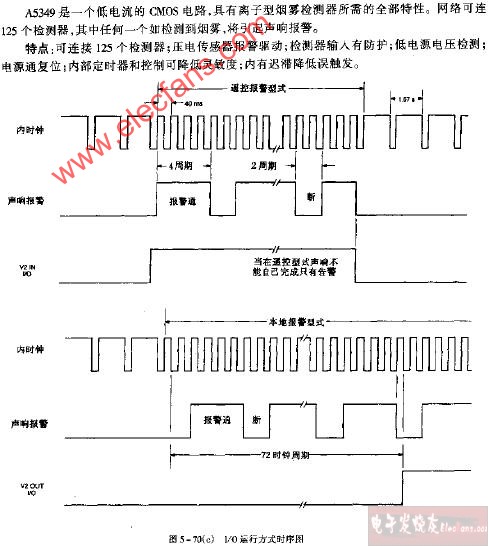

A5349 VO运行方式时序电路图

2009-07-03 12:14:37 603

603

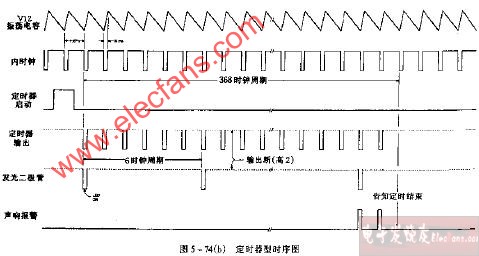

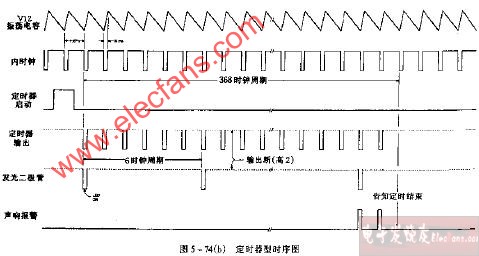

A5349定时器型式时序电路图

2009-07-03 12:18:14 443

443

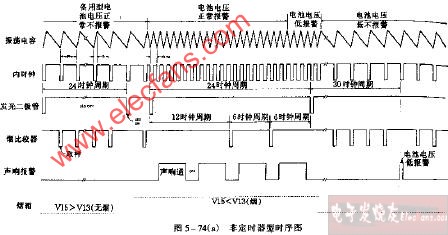

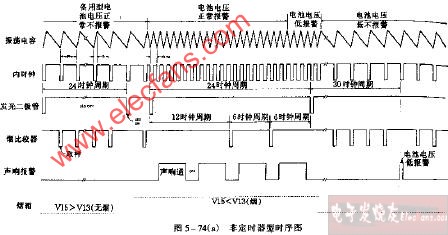

A5349非定时器型式时序电路图

2009-07-03 12:18:51 461

461

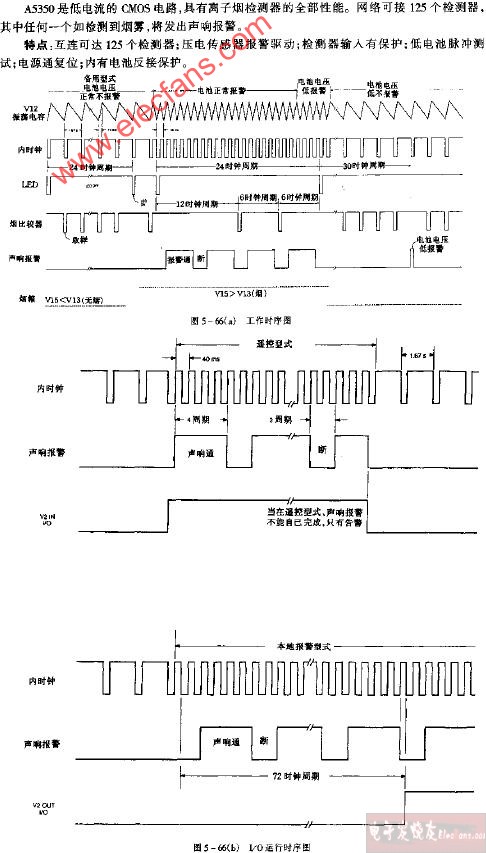

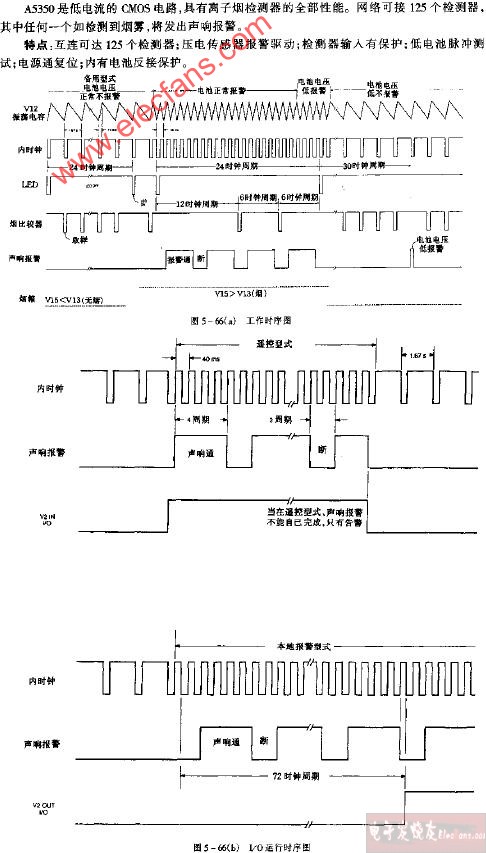

A5350 IO运行时序电路图

2009-07-03 12:20:26 484

484

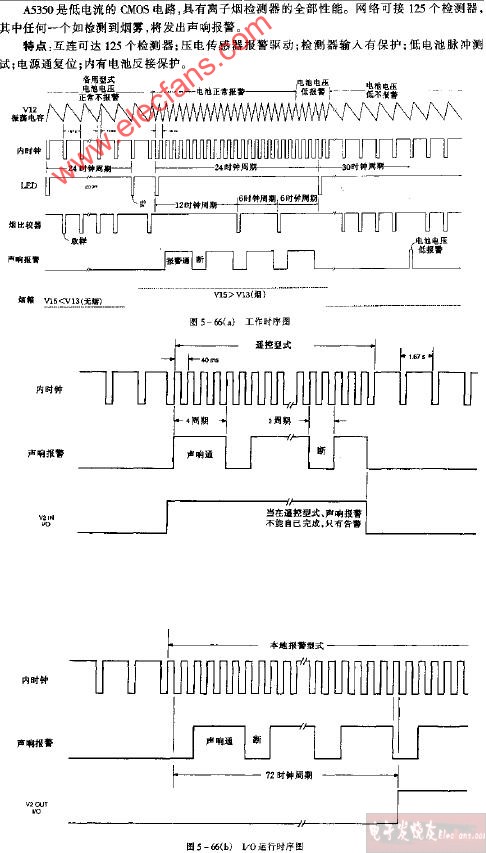

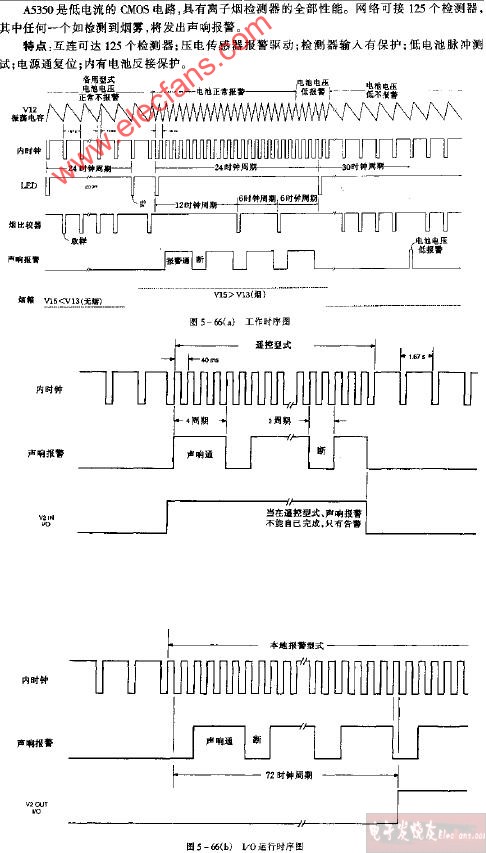

A5350工作时序电路图

2009-07-03 12:22:16 652

652

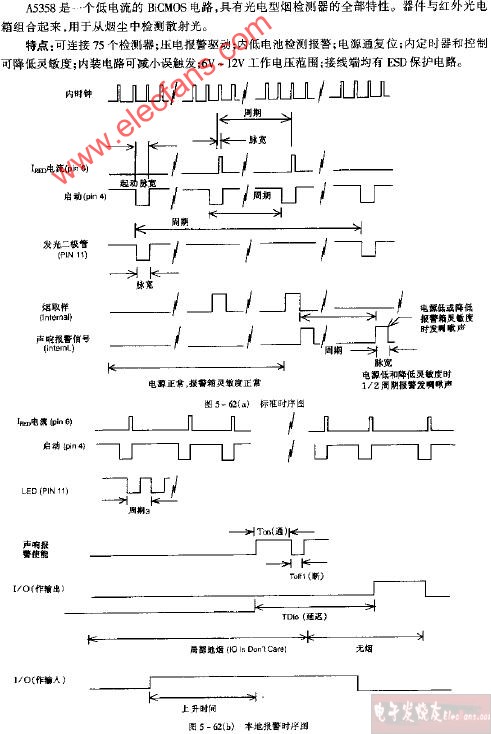

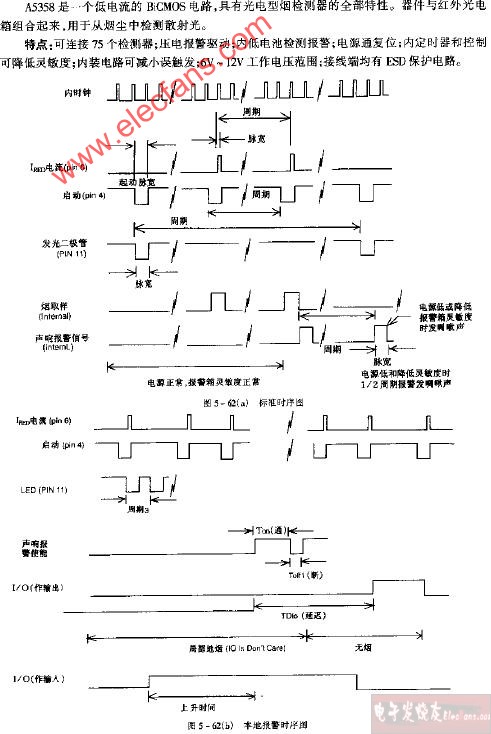

A5358本地报警时序电路图

2009-07-03 12:23:28 944

944

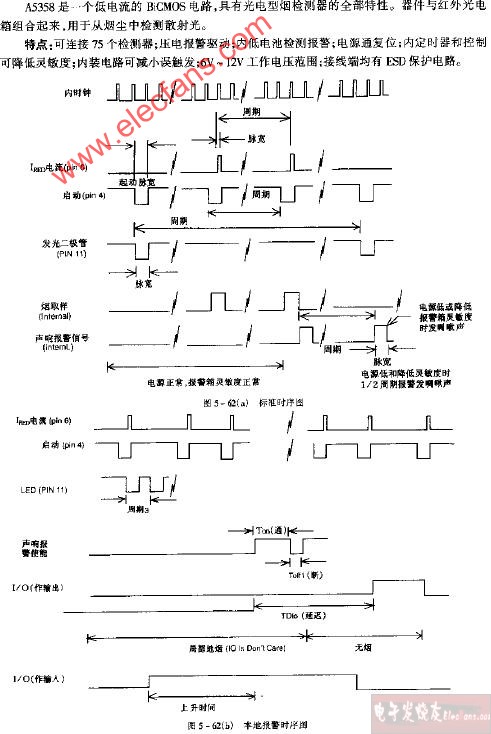

A5358标准时序电路图

2009-07-03 12:30:49 806

806

同步时序电路

4.2.1 同步时序电路的结构和代数法描述

2010-01-12 13:31:55 4672

4672

什么是时序电路

任意时刻的稳定输出,不仅与该时刻的输入有关,而且还

2010-01-12 13:23:14 8109

8109

为了实现时序电路状态验证和故障检测,需要事先设计一个输入测试序列。基于二叉树节点和树枝的特性,建立时序电路状态二叉树,按照电路二叉树节点(状态)与树枝(输入)的层次逻辑

2012-07-12 13:57:40 0

0 FPGA入门,简单的组合和时序电路

2016-12-16 15:46:41 24

24 基于FPGA技术的RS232接口时序电路设计方案

2017-01-26 11:36:55 29

29 1、了解时序电路的经典设计方法(D触发器、JK触发器和一般逻辑门组成的时序逻辑电路)。

2、了解同步计数器,异步计数器的使用方法。

3、了解同步计数器通过清零阻塞法和预显数法得到循环任意进制

2022-07-10 14:37:37 15

15 在传统设计中,所有计算机运算(算法逻辑和存储进程) 都参考时钟同步执行,时钟增加了设计中的时序电路数量。在这个电池供电设备大行其道的移动时代,为了节省每一毫瓦(mW) 的功耗,厂商间展开了残酷的竞争

2017-10-25 15:41:59 25

25 在传统设计中,所有计算机运算(算法、逻辑和存储进程)都参考时钟同步执行,时钟增加了设计中的时序电路数量。在这个电池供电设备大行其道的移动时代,为了节省每一毫瓦(mW)的功耗,厂商间展开了残酷的竞争

2017-11-15 15:40:13 12

12 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2017-11-20 12:26:21 8630

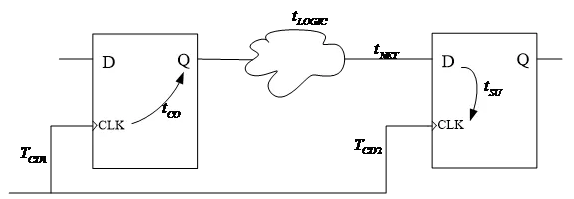

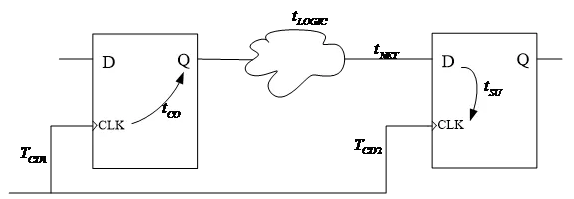

8630 “时钟是时序电路的控制者” 这句话太经典了,可以说是FPGA设计的圣言。FPGA的设计主要是以时序电路为主,因为组合逻辑电路再怎么复杂也变不出太多花样,理解起来也不没太多困难。但是时序电路就不

2018-07-21 10:55:37 4504

4504 组合电路和时序电路是计算机原理的基础课,组合电路描述的是单一的函数功能,函数输出只与当前的函数输入相关;时序电路则引入了时间维度,时序电路在通电的情况下,能够保持状态,电路的输出不仅与当前的输入有关,而且与前一时刻的电路状态相关,如我们个人PC中的内存和CPU中的寄存器,均为时序电路。

2018-09-25 09:50:00 24779

24779 关键词:时序电路 , 同步 同步时序电路设计 1.建立原始状态图. 建立原始状态图的方法是: 确定输入、输出和系统的状态函数(用字母表示). 根据设计要求,确定每一状态在规定条件下的状态迁移方向

2018-10-31 18:14:01 1097

1097 时序逻辑电路对于组合逻辑的毛刺具有容忍度,从而改善电路的时序特性。同时电路的更新由时钟控制。

2018-11-24 11:17:51 3197

3197

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-05-16 18:32:37 7636

7636

时序电路,是由最基本的逻辑门电路加上反馈逻辑回路(输出到输入)或器件组合而成的电路,与组合电路最本质的区别在于时序电路具有记忆功能。

2019-09-27 07:10:00 2169

2169

时序电路,是由最基本的逻辑门电路加上反馈逻辑回路(输出到输入)或器件组合而成的电路,与组合电路最本质的区别在于时序电路具有记忆功能。

2019-12-13 07:07:00 1743

1743

时序电路,是由最基本的逻辑门电路加上反馈逻辑回路(输出到输入)或器件组合而成的电路,与组合电路最本质的区别在于时序电路具有记忆功能。

2019-09-23 07:08:00 2068

2068

一 实验目的 掌握Mealy型时序电路设计方法。验证所设计电路的逻辑功能。体会状态分配对电路复杂性的影响

2019-06-25 08:00:00 1

1 本文档的主要内容详细介绍的是数码管与分析仪的时序电路原理图免费下载。

2019-12-13 15:17:11 8

8 时序电路是数字电路的基本电路,也是FPGA设计中不可缺少的设计模块之一。

2020-09-08 14:21:22 6067

6067

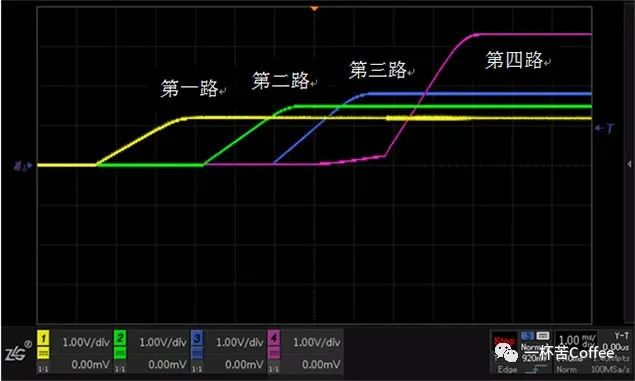

时间的重要性不言而喻,加上时间这个维度就如同X-Y的平面加上了一个Z轴,如同打开了一个新的世界。所以今天我们就要来聊聊时序电路。 在时序电路中,电路任何时刻的稳定状态输出不仅取决于当前的输入,还与

2021-01-06 17:07:22 4371

4371 电子发烧友网为你提供计算机原理基础课:组合电路和时序电路资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-14 08:49:16 3

3 组合逻辑和时序逻辑电路是数字系统设计的奠基石,其中组合电路包括多路复用器、解复用器、编码器、解码器等,而时序电路包括锁存器、触发器、计数器、寄存器等。 在本文中,小编简单介绍关于时序电路的类型和特点等相关内容。

2022-09-12 16:44:00 7234

7234

从今天开始新的一章-Circuits,包括基本逻辑电路、时序电路、组合电路等。

2022-10-10 15:39:01 875

875 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2023-03-14 17:06:50 4816

4816

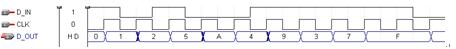

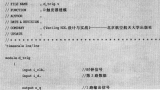

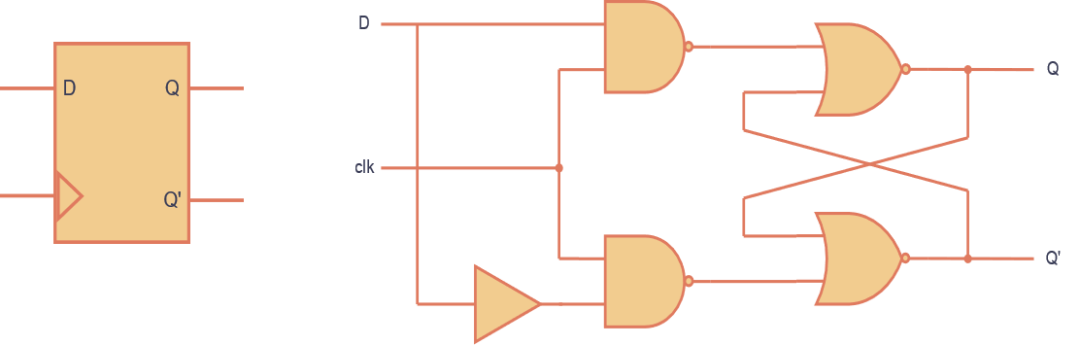

那么,如何才能将过去的输入状态反映到现在的输出上呢?「时序电路」到底需要些什么呢?人类总是根据过去的经验,决定现在的行动,这时我们需要的就是—记忆。同样,「时序电路」也需要这样的功能。这种能够实现人类记忆功能的元器件就是触发器。

2023-03-24 10:48:58 818

818

同步和异步时序电路都是使用反馈来产生下一代输出的时序电路。根据这种反馈的类型,可以区分这两种电路。时序电路的输出取决于当前和过去的输入。时序电路分为同步时序电路和异步时序电路是根据它们的触发器来完成的。

2023-03-25 17:29:52 17511

17511

时序电路的考察主要涉及分析与设计两个部分,上文介绍了时序逻辑电路的一些分析方法,重点介绍了同步时序电路分析的步骤与注意事项。 本文就时序逻辑电路设计的相关问题进行讨论,重点介绍时序逻辑电路的核心部分——计数器。

2023-05-22 17:01:29 1882

1882

时间的重要性不言而喻,加上时间这个维度就如同X-Y的平面加上了一个Z轴,如同打开了一个新的世界。所以今天我们就要来聊聊时序电路。

2023-06-20 16:59:50 252

252

一种基于电流源基准型LDO的放大器供电时序电路的应用

2023-11-23 09:04:52 272

272

时序电路是由触发器等时序元件组成的数字电路,用于处理时序信号,实现时序逻辑功能。根据时序元件的类型和组合方式的不同,时序电路可以分为同步时序电路和异步时序电路。本文将从这两个方面详细介绍时序电路

2024-02-06 11:22:30 291

291 时序电路是一种能够按照特定的顺序进行操作的电路。它以时钟信号为基准,根据输入信号的状态和过去的状态来确定输出信号的状态。时序电路广泛应用于计算机、通信系统、数字信号处理等领域。根据不同的分类标准

2024-02-06 11:25:21 399

399 时序电路基本原理是指电路中的输出信号与输入信号的时间相关性。简单来说,就是电路的输出信号要依赖于其输入信号的顺序和时间间隔。 时序电路由时钟信号、触发器和组合逻辑电路组成。时钟信号是时序电路的重要

2024-02-06 11:30:00 344

344

电子发烧友App

电子发烧友App

评论