为简化和加速复杂IC的开发,Cadence 设计系统公司 (NASDAQ:CDNS) 今天推出Tempus™ 时序签收解决方案。这是一款新的静态时序分析与收敛工具,旨在帮助系统级芯片 (SoC) 开发者加速时序收敛,将芯片设计快速转化为可制造的产品。

2013-05-21 15:37:37 2929

2929 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布,台积电(TSMC)在20纳米制程对全新的Cadence® Tempus™时序签收解决方案提供了认证。该认证

2013-05-24 11:31:17 1345

1345 。除了改善结果质量(QoR)之外,Innovus 设计实现系统容量更高,可支持实现更大的顶层模块,降低 SoC 顶层设计的分割区块和复杂度。

2018-05-07 13:11:28 4035

4035 楷登电子(NASDAQ:CDNS)今日宣布,发布增强型 Cadence® Voltus™IC 电源完整性解决方案,其面向先进工艺节点的电网签核,其大规模并行(XP)算法选项采用了分布式处理技术。

2018-07-26 15:59:22 6981

6981 本文通过介绍多种电源时序控制的实现,简述应对多领域应用的电源时序控制挑战ADI是如何提供易于使用解决方案的。

2022-08-01 09:10:15 552

552

两级转换需要额外的半导体器件,但与单级解决方案相比,对于低至中功率SoC核心轨道来说,总体SoC电源解决方案可能更小、更便宜。系统设计师必须权衡所有因素,例如12V电池化学成分和SoC核心轨道功率规格,以选择设计的最佳电源架构。

2023-10-07 10:43:23 228

228

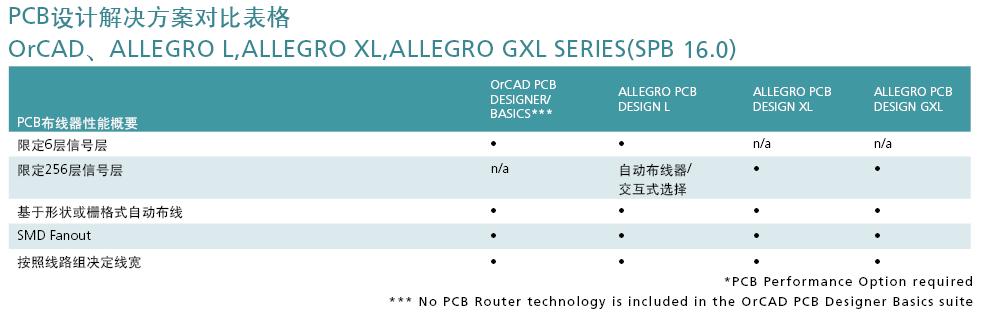

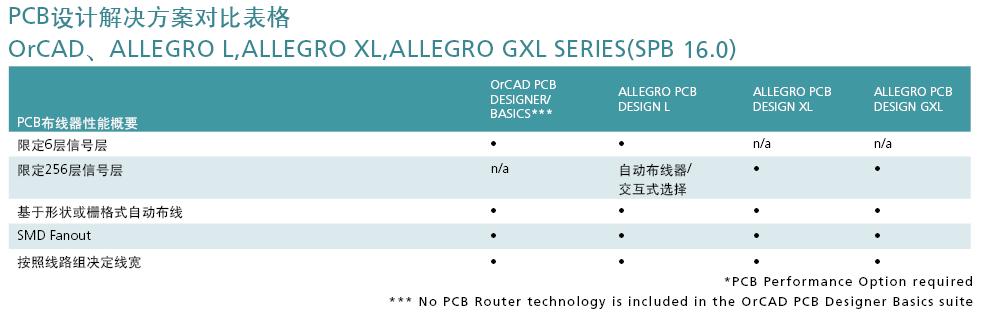

CADENCE PCB设计解决方案能为解决与实现高难度的与制造密切相关的设计提供完整的设计环境,该设计解决方案集成了从设计构想至最终产品所需要的一切设计流程,

2011-12-15 14:14:32 2074

2074 特性 PCB编辑器技术 PCB编辑环境 Cadence PCB设计解决方案的核心是PCB编辑器,这是一种直观的、易于使用的、约束导向型的环境,方便用户创建和编辑从简单到复杂的PCB。它广泛的功能

2018-08-30 10:49:16

和静态时序分析功能实现系统驱动的功耗,性能和芯片面积(PPA,Power, Performance and Area)要求。Cadence 的第三代 三位3D-IC 解决方案支持广泛的应用领域,包括

2021-10-14 11:19:57

cadence公司于2012年9月25日发布了具有一系列新功能的Cadence® OrCAD® 16.6 PCB设计解决方案,用户定制功能增强,模拟性能提高20

2012-12-18 10:18:07

的解决方案形成强烈的对比。” Cadence在开发套件方面的目标是为了推动不同领域产品开发的步伐。Cadence的套件通过将验证方式和流程与IP相结合的方式更好的应对无线、网络和消费电子等不同领域在设计方面的挑战。通过采用Cadence的套件,顾客可以将其宝贵的资源投入在差异化设计而不是基础设计方面。

2008-06-27 10:24:12

SoC FPGA的DSP能力应对新兴的***需求是什么?

2021-05-24 07:05:13

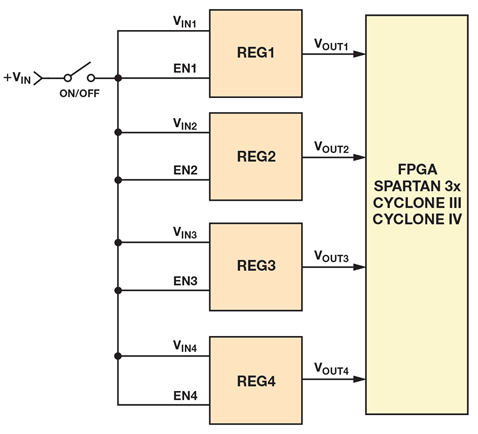

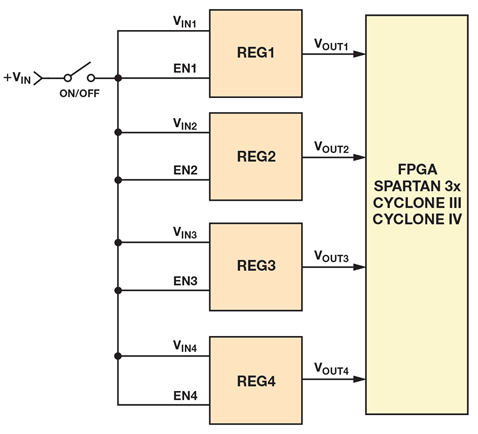

简介 电源时序控制是微控制器、FPGA、DSP、ADC和其他需要多个电压轨供电的器件所必需的一项功能。这些应用通常需要在数字I/O轨上电前对内核和模拟模块上电,但有些设计可能需要采用其他序列

2018-09-30 16:01:35

描述 PMP9353 参考设计是 Altera Cyclone V SoC 器件的完整电源解决方案。此设计使用多个 LMZ3 系列模块、两个 LDO 和一个 DDR 终端稳压器提供为 SoC 芯片

2022-09-26 07:58:34

描述PMP9353 参考设计是 Altera Cyclone V SoC 器件的完整电源解决方案。此设计使用多个 LMZ3 系列模块、两个 LDO 和一个 DDR 终端稳压器提供为 SoC 芯片供电

2018-09-06 09:07:37

描述PMP9353 参考设计是 Altera Cyclone V SoC 器件的完整电源解决方案。此设计使用多个 LMZ3 系列模块、两个 LDO 和一个 DDR 终端稳压器提供为 SoC 芯片供电

2015-05-11 16:45:44

联网(IoT)、医疗、网络和数据中心设备在内的一系列工业和计算应用的供电技术开发。这些即用型参考设计提供了简单可靠的解决方案,在满足所有相关复杂性要求的同时,为整个Xilinx Zynq系列的FPGA

2021-06-01 07:30:00

仿真,提供业界一流的晶体管级精度,以满足在先进制程上复杂的生产工艺要求,它补充了Cadence Voltus IC电源完整性解决方案中全芯片、模块级电源签收工具,完善了公司电源签收的技术方案

2018-09-30 16:11:32

本文介绍一种面向基站平台处理单板的基于融合SoC处理器的平台软件解决方案。

2021-05-17 06:36:12

分享一款不错的Dialog DA145080蓝牙智能SoC解决方案

2021-05-24 06:33:51

本文介绍应对汽车电子控制装置(ECU)开发的最新汽车电子测试解决方案。

2021-05-13 06:18:52

业内首个signoff驱动的PrimeECO解决方案发布

2020-11-23 14:28:15

安捷伦公司数字测试资深技术/市场工程师 冀卫东为满足日益复杂的数字化系统的设计要求,FPGA的密度及复杂性也在急速增长,越来越多的系统或子系统功能在FPGA内部实现,其先进的功能和高集成度使FPGA成为极具吸引力的解决方案,进而也使得基于内核的FPGA测试方案浮出水面。

2019-07-11 06:15:12

工业系统通常由微控制器和FPGA器件等组成,美高森美(Microsemi® )基于 SmartFusion®2 SoC FPGA的马达控制解决方案是使用高集成度器件为工业设计带来更多优势的一个范例。

2019-10-10 07:15:34

篇文章中,我们将探讨由于5纳米技术以及SoC中新的额外功能而带来的新挑战。我们将展示解决floor planning和时序问题的方法,以减少物理实施的迭代。方法大型、复杂的IP集成的实施需要一种

2022-11-16 14:57:43

进行监控。当所有电压建立之后,时序控制器电路产生电源良好信号。模拟时序控制解决方案(如ADM1186-1)很容易使用。它们具备多电压系统所需的全部功能。模拟时序控制器与数字时序控制器的不同之处在于,前者

2021-04-12 07:00:00

寻求AMD R系列与AMD SOC系列嵌入式高效能解决方案

2021-05-10 06:05:01

求一款Cadence的高级可制造性设计解决方案

2021-04-26 06:25:07

求一种应对压电效应失效的电容器解决方案

2021-06-08 06:39:35

我要如何发布我的HarmonyOS组件或解决方案?

2022-06-02 15:55:36

求大佬分享一款应对压电效应失效的电容器解决方案

2021-06-08 06:38:38

适合SoC的20V输入至1V、15A输出解决方案LTC7151S的主要参数

2021-03-11 06:22:28

用于工业和汽车系统的先进SoC(片上系统)解决方案的功率预算不断增加。每个连续的SoC产品都增加了耗电设备并提高了数据处理速度。这些器件需要可靠的电源,包括0.8V的内核,1.2V和1.1V

2018-12-26 09:17:59

启动和关断这些电源轨。此过程称为电源时序控制或电源定序,目前有许多解决方案可以有效实现定序。对于需要电压定序的复杂器件,其内核和模拟模块的电压轨可能需要在数字 I/O 电压轨之前上电。有些设计可能会要求...

2021-11-12 06:01:50

应对日益复杂的网络容量挑战方面发挥着关键作用。小型化的基站主要有城域基站、微微蜂窝基站(Picocell)以及更小一点的毫微微蜂窝基站(Femtocell,又称飞蜂窝基站或家庭基站,相当于在一个公司

2019-07-09 07:25:59

Cadence高速PCB的时序分析:列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,

2009-07-01 17:23:27 0

0 时序计算和Cadence 仿真结果的运用中兴通讯康讯研究所 EDA 设计部 余昌盛 刘忠亮摘要:本文通过对源同步时序公式的推导,结合对SPECCTRAQuest 时序仿真方法的分析,推导出了使

2009-12-21 09:05:39 172

172 Cadence 高速 PCB 的时序分析 1.引言 时序分析,也许是 SI 分析中难度最大的一部分。我怀着满腔的期许给 Cadence 的资深工程师发了一封 e-mail,希望能够得到一份时序分析的案

2010-04-05 06:37:13 0

0 Intel Enpirion®电源解决方案Intel® Enpirion®电源解决方案是高频、高效电源管理器件,用于FPGA(现场可编程门阵列)、SoC(片上系统)、 CPU(中央处理单元

2024-02-27 11:50:19

2009年3月4日,Cadence设计系统公司今天宣布生物指纹安全解决方案领先厂商UPEK®, Inc.已经整合其设计流程,并选择Cadence®作为其全芯片数字、模拟与混合信号设计的

2009-03-05 12:14:18 519

519 Cadence推出首个TLM驱动式设计与验证解决方案

Cadence设计系统公司今天推出首个TLM驱动式协同设计与验证解决方案和方法学,使SoC设计师们可以尽享事务级建模(TLM)的好处。

2009-08-07 07:32:00 674

674 Cadence推出首个TLM驱动式设计与验证解决方案提升基于RTL流程的开发效率

Cadence设计系统公司推出首个TLM驱动式协同设计与验证解决方案和方法学,使SoC设计师们可以尽

2009-08-11 09:12:18 499

499 中芯国际采用Cadence DFM解决方案用于65和45纳米 IP/库开发和全芯片生产

Cadence 模型化的 Litho Physical 和 Litho Electrical

2009-10-19 17:48:11 461

461 Cadence 模型化的 Litho Physical 和 Litho Electrical AnalyzerLitho Physical 与 Litho Electrical Analyzer 解决方案提供了快速、精确硅认证的全芯片电气 DFM 验证流程

2009-10-20 09:54:02 990

990 Magma推出面向大型SoC的增强版层次化设计规划解决方案

微捷码(Magma)日前发布了面向大型片上系统(SoC)的增强版层次化设计规划解决方案Hydra 1.1。新版产品提供了通道

2009-12-09 08:31:53 888

888 CADENCE PCB设计技术方案

CADENCE PCB设计解决方案能为解决与实现高难度的与制造密切相关的设计提供完整的设计环境,该设计解决方案集成了从设计构

2010-04-29 08:53:19 3756

3756

ARM公司近日宣布针对复杂片上系统(SoC)设计推出高度可配置的调试和追踪解决方案ARM CoreSight SoC-400

2011-05-09 09:15:11 965

965 根据源同步的一些基本问题,在Cadence仿真环境下,对源同步时序进行仿真,仿真结果表明,设计能满足噪声容限和过冲,仿真后的可知数据线和时间的延时约为0.3ns,满足源同步系统设

2012-05-29 15:26:26 0

0 电子发烧友网核心提示 :全球电子设计创新领先企业Cadence设计系统公司于日前发布了具有一系列新功能的Cadence OrCAD 16.6 PCB设计解决方案,用户定制功能增强,模拟性能提高20%, 使用户

2012-10-16 08:44:25 1192

1192 全球电子设计创新领先企业Cadence设计系统公司日前宣布TSMC已选择Cadence解决方案作为其20纳米的设计架构。Cadence解决方案包括Virtuoso定制/模拟以及Encounter RTL-to-Signoff平台。

2012-10-22 16:48:03 909

909 全球电子软硬件设计解决方案提供商Mentor Graphics日前先后在上海和北京成功举办了Mentor Forum 2012设计技术论坛。此次论坛主旨为突破十亿逻辑门设计藩篱克服SoC设计的复杂性(Break the

2012-11-19 09:04:04 680

680 光刻物理分析器成功完成20纳米系统级芯片(SoC)测试芯片流片。双方工程师通过紧密合作,运用Cadence解决方案克服实施和可制造性设计(DFM)验证挑战,并最终完成设计。

2013-07-09 15:53:24 769

769 中芯国际新款40纳米 Reference Flow5.1结合了最先进的Cadence CCOpt和GigaOpt工艺以及Tempus 时序签收解决方案, 新款RTL-to-GDSII数字流程支持Cadence的分层低功耗流程和最新版本的通用功率格式(CPF).

2013-09-05 10:45:03 1839

1839 署Cadence Encounter® 数字设计工具,智原科技的设计团队在短短的七个月内,就完成了这个复杂SoC从输入数据到流片的工作。

2013-11-19 10:30:13 886

886 全球知名电子设计创新领先公司Cadence设计系统公司 (NASDAQ: CDNS),今日宣布台积电采用了Cadence®16纳米FinFET单元库特性分析解决方案。

2014-10-08 19:03:22 1594

1594 泰克应对电源测试种种挑战解决方案

2016-12-25 00:38:41 0

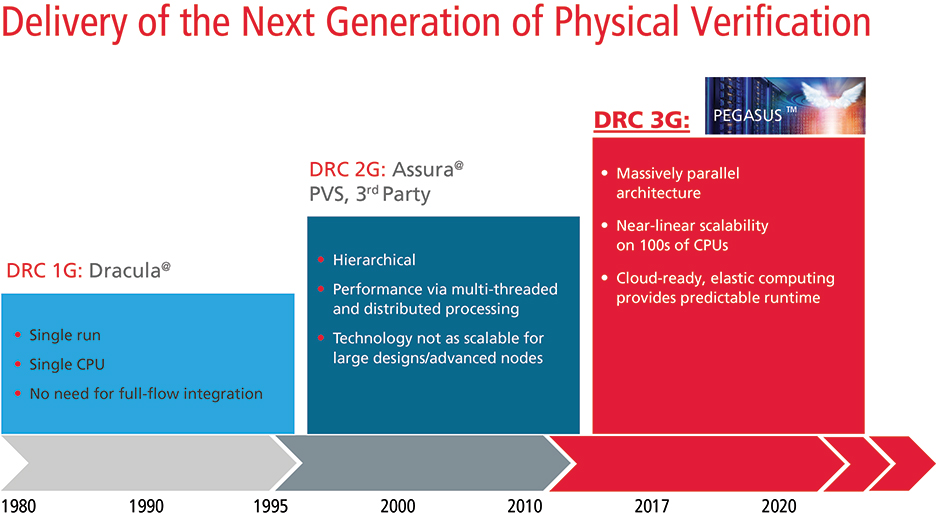

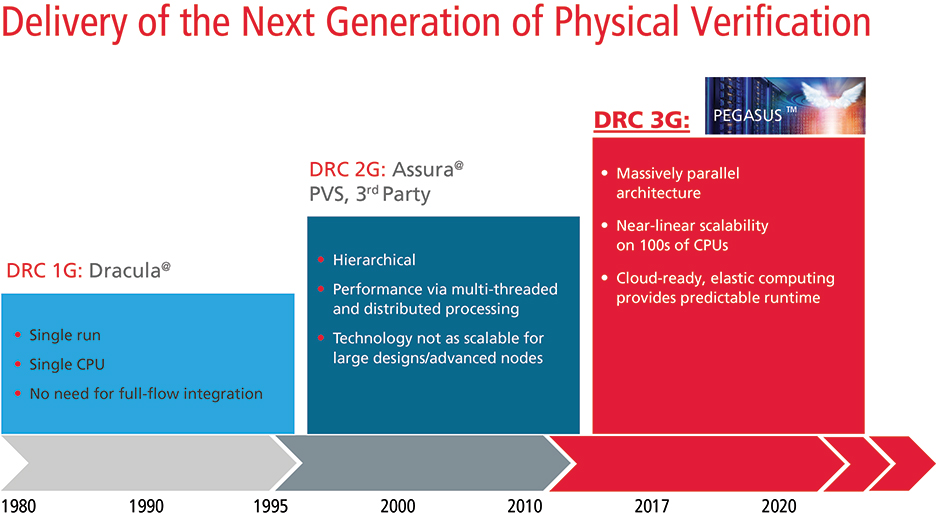

0 2017年4月14日,中国上海 - 楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日正式发布Pegasus™验证系统,该云计算(cloud-ready)大规模并行物理签核解决方案

2017-04-14 15:42:44 1294

1294

之签收与验证部门,公司副总裁Anirudh Devgan看来,传统的签收流程却没能跟上这种需求的步伐。为帮助系统级芯片(SoC)开发者加速时序收敛,将芯片设计快速转化为可制造的产品,Cadence于近期宣布推出划时代时序签收解决方案Tempus。它有何过人之处?让我们一睹为快。 时序签收目前在整个

2017-12-04 10:30:45 0

0 为了充分利用系统级芯片(SoC)设计带来的优点,业界需要一种可以扩展的验证解决方案,解决设计周期中各个阶段的问题,缩短验证鸿沟。本文将探讨可扩展验证解决方案为何能够以及如何解决SoC设计目前面临的功能方面的严峻挑战,以达到提高设计生产力、保证设计质量、缩短产品上市时间以及提高投资回报率的目的。

2018-06-04 03:13:00 743

743

Fujisoft公司在Altera SoC合作伙伴研讨会上演讲的主题:Fujisoft Android SoC FPGA解决方案

2018-06-26 11:57:00 2643

2643 CC2431.cc2430及Zigbee应用的片上系统(SOC)解决方案

2018-06-26 15:25:00 5460

5460 7月24号,华为云中国行第三站北京站,华为云发布国内首个完整的公有云容灾备份解决方案——华为云Multi cloud混合云灾备解决方案。 华为云EI产品部总经理贾永利现场发布华为云Multi

2018-07-29 09:31:00 8095

8095 新思科技宣布,推出适用于下一代架构探索、分析和设计的解决方案Platform Architect™Ultra,以应对人工智能(AI)系统级芯片(SoC)的系统挑战。

2018-11-01 11:51:38 6809

6809 可见,我们的物理解决方案比以往任何时候都面临更高的风险。随着当今数字环境的不断发展以及物理和网络攻击的日益复杂,我们必须采取特殊的预防措施来应对这些威胁。

2020-09-22 10:54:18 1353

1353 Cadence拥有最完整的IP与SoC验证、硬件与软件回归测试及早期软件开发的全系列解决方案。

2021-04-06 13:48:53 2431

2431 电子发烧友网为你提供复杂电源时序控制如何轻易实现?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-25 08:47:52 7

7 俗话说,一画胜千言;由此推算,一段视频足以洞若观火。 Cadence 发布了面向 PCI Express (PCIe) 5.0 系统的 SoC 硅芯片演示视频,这个视频将向您介绍我们如何把最前

2021-05-14 10:33:55 1787

1787 调试中常见复杂问题和TRACE32相应的解决方案(13005开关电源启动电阻)-调试中常见复杂问题和TRACE32®相应的解决方案

2021-07-26 10:44:28 15

15 Paper”的殊荣。 此外,在今天下午举行的各个技术分论坛上,燧原科技分别在“数字设计与Signoff”和“PCB、封装和系统分析”会议上发表了演讲。 Tempus-PI 仿真和实测关键时序路径的一致性

2021-10-19 14:17:23 1387

1387 Cadence Safety Solution 包括新的 Midas Safety Platform,为模拟和数字流程提供基于 FMEDA 功能安全设计和验证的统一方案 该安全流程方案为汽车、工业

2021-10-26 14:24:34 4050

4050 Liberate Characterization 和 Tempus 解决方案已经通过 Samsung Foundry 老化模型验证,使客户能够快速、安心地完成高可靠性的设计签核 Tempus 解决方案的全新

2021-11-19 11:00:13 2967

2967 GlobalFoundries 在 AWS 上完成了对 Cadence 数字解决方案的认证,可用于其专有的差异化 22FDX 平台。

2022-03-28 11:17:46 1812

1812 Cadence Stylus Common UI 可在 Genus Synthesis、Innovus Implementation 和 Tempus Signoff 工具之间实现连续且易于

2022-04-08 09:26:03 3162

3162 Cadence Conformal ECO Designer 使用形式验证引擎提供经过硅验证的自动化 ECO 解决方案。它利用 Cadence 的物理逻辑综合技术来映射和优化 ECO 逻辑,从而支持考虑时序和拥塞的 pre-mask 和 post-mask 流程。

2022-04-12 09:59:49 912

912 High-Speed Ethernet Controller IP 系列和集成子系统解决方案扩展了 Cadence 的以太网 IP 组合,支持 Cadence 的智能系统设计™ (Intelligent System Design™) 战略,旨在实现 SoC 的卓越设计。

2022-04-13 15:28:46 1209

1209 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布推出 15 种新的验证 IP(VIP)解决方案,助力工程师迅速有效地验证设计,以满足最新标准协议的要求。

2022-06-06 11:18:21 2665

2665 内存和存储解决方案领先供应商 Micron Technology, Inc.(美光科技股份有限公司,纳斯达克代码:MU)近日宣布扩展旗下嵌入式产品组合与生态系统合作伙伴阵容,推出一系列功能强大的优化解决方案,以应对智能边缘复杂的内存与存储需求。

2022-06-27 15:31:16 1055

1055

电子发烧友网站提供《Altera Cyclone V SoC电源解决方案.zip》资料免费下载

2022-09-07 11:14:48 2

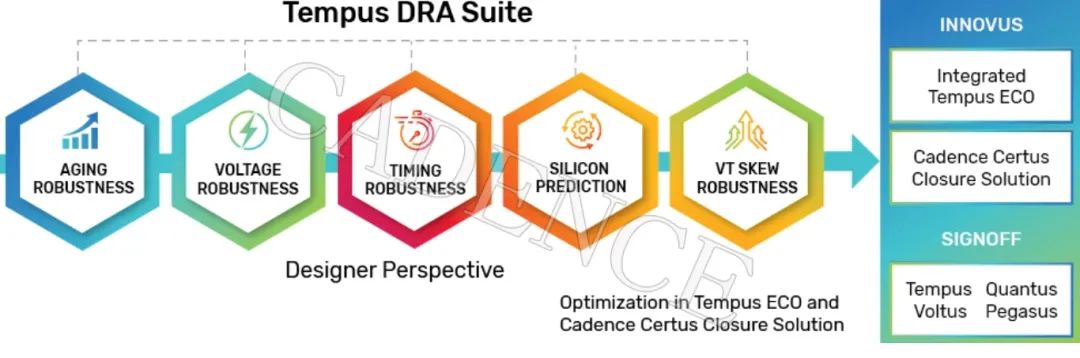

2 因此,通过与 Cadence Innovus Implementation System 和 Tempus Timing Signoff Solution 共享同一个引擎,并行全芯片优化得以实现,模块所有者无需进行反复迭代,设计师也可以快速做出优化和签核决定。

2022-10-12 15:59:04 672

672 上述流程会用到两个主要工具,分别是用于模块层次优化的 Tempus ECO,以及用于 SoC 层面静态时序分析的 Tempus STA。这里缺失了全芯片(或子系统)优化与签核。至于分区间功耗恢复等则只能忽略,因为实在没时间处理。

2022-11-01 14:18:14 698

698 Cadence 射频集成电路解决方案支持 Cadence 智能系统设计(Intelligent System Design)战略,助力实现系统级芯片(SoC)的卓越设计。

2022-11-03 14:18:50 835

835 本文介绍Cadence Tempus电源完整性解决方案如何为燧原科技(Enflame)面向数据中心而开发的先进节点人工智能(AI)芯片提供电源完整性(Power Integrity, PI)和信号完整性(Signal Integrity, SI)保障。

2023-07-12 11:12:16 208

208 双方的共同客户可获取 Cadence 的全流程系统级设计验证和实现解决方案以及接口 IP,依托 Neoverse CSS 加速开发基于 Arm 的定制 SoC 中国上海,2023 年 10 月 25

2023-10-25 10:40:02 197

197

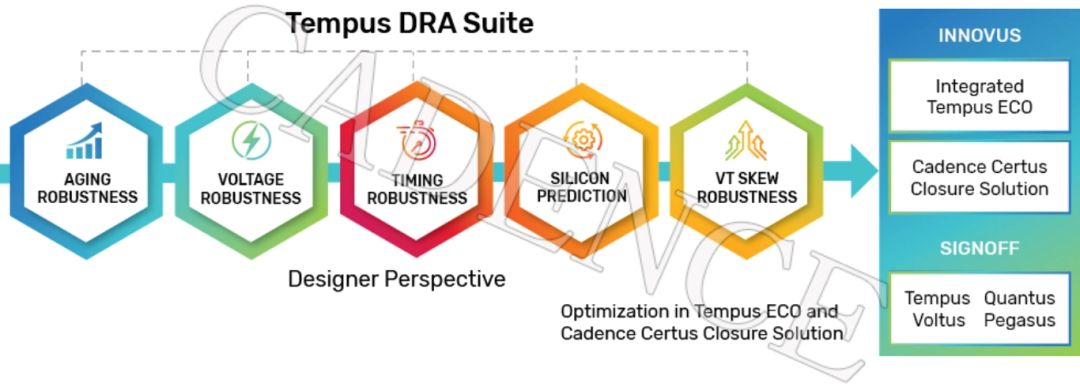

Innovus 设计实现系统中的 Tempus ECO 选项进行模块级的收敛,并使用 Cadence Certus 收敛解决方案进

2023-11-01 14:50:03 210

210

公司,NASDAQ:CDNS )近日宣布,Realtek 成功使用 Cadence Tempus Timing Solution 签核 N12 高性能 CPU 内核,同时显著改善了功率、性能和面

2023-11-06 10:10:01 206

206 设计签核,并取得了更好的 PPA 结果 2 首次部署 Cadence 签核解决方案后,Samsung Foundry 实现了两倍的生产力提升,加速了设计收敛 中国上海,2023 年 12

2023-12-04 10:15:01 244

244 今天想聊一聊STA相关的RC corner的问题。我先简单介绍一些什么是signoff的corner,然后重点聊一聊RC corner。

2023-12-05 14:11:12 379

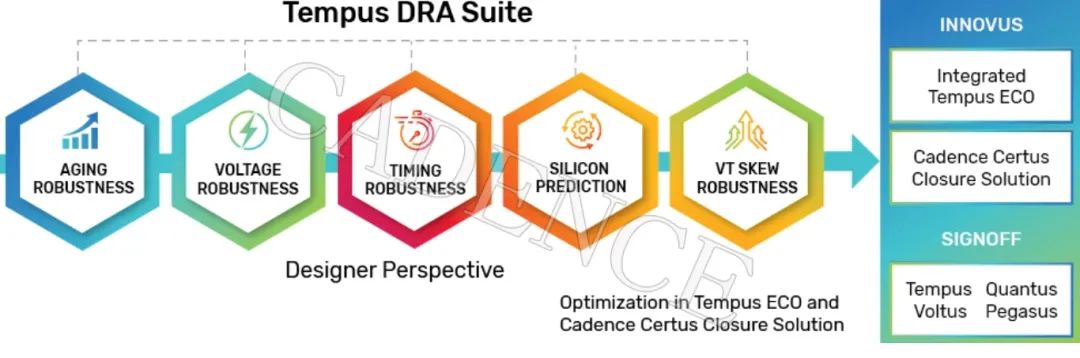

379 及其影响的分析,客户才能实现较现行设计方法更优秀的 PPA 目标。例如,全局额定值或全局的裕度会造成性能和功耗的显著浪费。 为了应对类似挑战,Cadence 持续创新并开发了 Cadence Tempus 设计稳健性分析(DRA)套件,提供解决上述问题所需要的分析能力。该套

2023-12-12 10:10:02 215

215

要应对恶劣环境,工程师必须仔细评估应对不同恶劣环境的不同要求,兼顾材料选择、设计考量和测试协议等,并定制相应的互连解决方案,以确保连接器在延长使用寿命的同时具有强大而可靠的性能。

2024-01-25 11:21:36 166

166

电子发烧友App

电子发烧友App

评论