dds技术是什么

dds简介:

DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写,是一项关键的数字化技术。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

DDS芯片中主要包括频率控制寄存器、高速相位累加器和正弦计算器三个部分(如Q2220)。频率控制寄存器可以串行或并行的方式装载并寄存用户输入的频率控制码;而相位累加器根据dds频率控制码在每个时钟周期内进行相位累加,得到一个相位值;正弦计算器则对该相位值计算数字化正弦波幅度(芯片一般通过查表得到)。DDS芯片输出的一般是数字化的正弦波,因此还需经过高速D/A转换器和低通滤波器才能得到一个可用的模拟频率信号。

另外,有些DDS芯片还具有调幅、调频和调相等调制功能及片内D/A变换器(如AD7008)。

dds优点:

频率分辨率高、输出频点多、可达2的N次方个频点(N为相位累加器位数);

频率切换速度快,DDS是一个开环系统,无任何反馈环节,因而频率转换时间极短,可达ns量级;

频率切换时相位连续;

可以输出宽带正交信号;

输出相位噪声低,对参考频率源的相位噪声有改善作用;

可以产生任意波形;全数字化实现、便于集成、体积小、重量轻。

在各行各业的测试应用中,信号源扮演着极为重要的作用。但信号源具有许多不同的类型,不同类型的信号源在功能和特性上各不相同,分别适用于许多不同的应用。波形发生器,函数发生器,RF信号源,以及基本的模拟输出模块。信号源中采用DDS技术在当前的测试测量行业已经逐渐称为一种主流的做法。

DDS工作原理

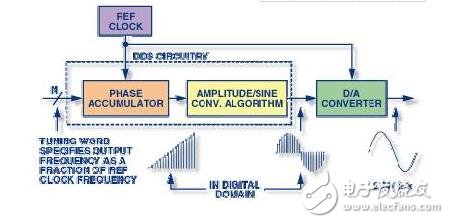

Error! Reference source not found. 是DDS 的内部结构图,它主要分成3 部分:相位累加器,相位幅度转换,数模转换器(DAC)。

相位累加器

一个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。

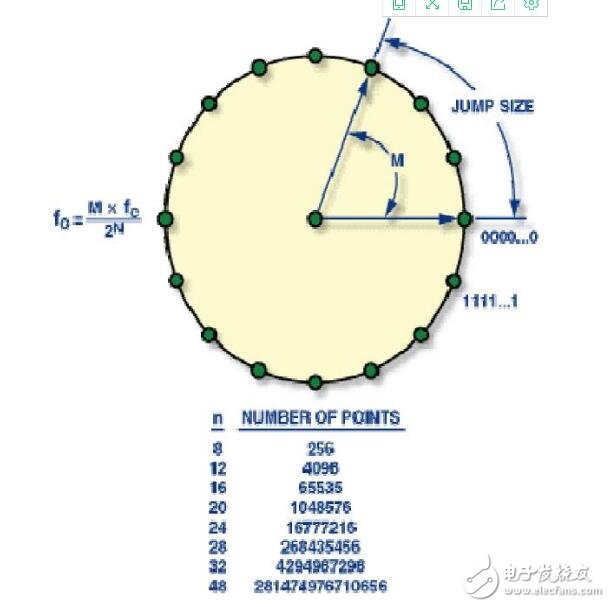

DDS 正是利用了这一特点来产生正弦信号。如图 2,根据DDS 的频率控制字的位数N,把360° 平均分成了2的N次等份。

图2,相位累加器原理

假设系统时钟为Fc,输出频率为Fout。每次转动一个角度360°/2N, 则可以产生一个频率为Fc/2N 的正弦波的相位递增量。那么只要选择恰当的频率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的输出频率Fout,

Fout = Fc*M / 2N,相位幅度转换通过相位累加器,我们已经得到了合成Fout 频率所对应的相位信息,然后相位幅度转换器把0°~360°的相位转换成相应相位的幅度值。比如当DDS 选择为2V p-p 的输出时,45°对应的幅度值为0.707V,这个数值以二进制的形式被送入DAC。这个相位到幅度的转换是通过查表完成的。

DAC 输出代表幅度的二进制数字信号被送入DAC 中,并转换成为模拟信号输出。注意DAC 的位数并不影响输出频率的分辨率。输出频率的分辨率是由频率控制字的位数决定的。

直接数字式频率合成技术(DDS)是一种先进的全数字频率合成技术,它具有多种数字式调制能力(如相位调制、频率调制、幅度调制以及I/Q正交调制等),在通信、导航、雷达、电子战等领域获得了广泛的应用。在项目中光栅传感系统高频并行解调算法的FPGA实现我们的光纤通信模块用到DDS。我们通过FPGA 实现了DDS的功能。

1971年,美国学者J.Tierney等人撰写的《A Digital Frequency

Synthesizer》一文首次提出了以全数字技术,从相位概念出发直接合成所需波形的一种新的频率合成原理。限于当时的技术和器件水平,它的性能指标尚不能与已有的技术相比,故未受到重视。近10年间,随着微电子技术的迅速发展,直接数字频率合成器(Direct Digital Frequency Synthesis简称DDS或DDFS)得到了飞速的发展,它以有别于其它频率合成方法的优越性能和特点成为现代频率合成技术中的佼佼者。具体体现在相对带宽宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程和全数字化、控制灵活方便等方面,并具有极高的性价比。

DDS基本原理及性能特点

DDS的基本原理是利用采样定理,通过查表法产生波形。DDS的结构有很多种,其基本的电路原理如图所示。

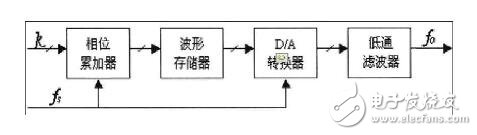

相位累加器由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲fs,加法器将频率控制字k与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字k相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。

用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

DDS在相对带宽、频率转换时间、高分辨力、相位连续性、正交输出以及集成化等一系列性能指标方面远远超过了传统频

非常好我支持^.^

(317) 99.1%

不好我反对

(3) 0.90000000000001%

相关阅读:

- [电子说] 为什么DDR3/4不需要设置input delay呢? 2023-09-11

- [电子说] XILINX FPGA IP之DDS Compiler_ip例化仿真 2023-09-07

- [电子说] 如何判定杂散来源? 2023-09-04

- [电子说] 直接数字合成技术(DDS)是什么?DDS又是如何工作的? 2023-08-24

- [电子说] DDS-IP核的理论知识和应用案例 2023-08-22

- [电子说] FPGA和DDS在信号源中的应用 2023-07-24

- [电子说] Xilinx Vivado DDS IP使用方法 2023-07-24

- [汽车电子] 基于ADAS自动泊车功能的DDS协议的系统设计 2023-07-14

( 发表人:姚远香-老账号 )