电平转换器,电平转换器原理和相关电路分析

在新一代电子电路设计中, 随着低电压逻辑的引入,系统内部常常出现输入/ 输出逻辑不协调的问题, 从而提高了系统设计的复杂性。例如, 当1. 8V的数字电路与工作在3. 3V 的模拟电路进行通信时,需要首先解决两种电平的转换问题,这时就需要电平转换器。

随着不同工作电压的数字IC 的不断涌现,逻辑电平转换的必要性更加突出, 电平转换方式也将随逻辑电压、数据总线的形式(例如4 线SPI、32 位并行数据总线等) 以及数据传输速率的不同而改变。现在虽然许多逻辑芯片都能实现较高的逻辑电平至较低逻辑电平的转换(如将5V 电平转换至3V 电平) ,但极少有逻辑电路芯片能够将较低的逻辑电平转换成较高的逻辑电平(如将3V逻辑转换至5V逻辑) 。另外,电平转换器虽然也可以用晶体管甚至电阻———二极管的组合来实现, 但因受寄生电容的影响,这些方法大大限制了数据的传输速率。尽管宽字节的电平转换器已经商用化, 但这些产品不是针对数据速率低于20Mbps 的串行总线(SPITM、I2CTM、USB 等) 优化的, 这些器件具有较大的封装尺寸、较多的引脚数和I/ O 方向控制引脚,因而不适合小型串行或外设接口和更高速率的总线(如以太网、LVDS、SCSI 等) 。

[编辑]发展状况

很多电子系统继续向更低的电压信号水平转移。这个发展潮流背后的动力是对减少功耗的需求。更快的整流速度和降低信号噪声等方面的进步既方便了设计者,也向他们提出了新的挑战。 微处理器在向较低的电压水平进军的过程中一马当先。处理器I/O电压正从1.8V转移到1.5V,而内核电压能够低于1V。下一代微处理器甚至将采用更低的电压。外围设备组件的电压虽然也在降低,但水平通常落后于处理器一代左右。电压降低方面的发展不均带来了系统设计者必须解决的关键性难题——如何在信号电平之间进行可靠的转换。正确的信号电平可以保证系统的可靠工作,它们能够防止敏感IC因过高或者过低的电压条件而受损。目前电平转换分为单向转换和双向转换,还有单电源和双电源转换,双电源转换采用双轨方案具有满足各方面性能的要求。

[编辑]相关理论

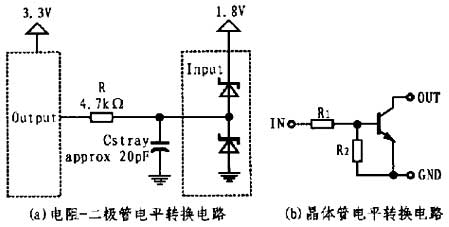

串行外设接口一般由单向控制线、数据输入、数据输出、时钟和片选组成,数据输入/ 输出还可以是MISO(主机输入、从机输出) 和MOSI(主机输出、从机输入) 。SPI 的时钟速率可超出20Mbps ,并由CMOS 推挽式逻辑输出级驱动。数据传输的单向性简化了转换器的设计。由于不必考虑数据在单条信号线上的双向传输问题,因此,可以利用图示的简单电阻———二极管方案或晶体管方案。

双向总线电平转换需要考虑在单条信号线上实现数据的双向传输,这在具体实施时比较困难,电阻———二极管结构或单晶体管由于受其固有的单向传输特性的制约而无法胜任这项工作。I2C、SMBus、Dallas 半导体公司的1 - wire 均为双向传输总线, 同时都是漏极开路I/ O 拓扑。其中I2C具有三种速率范围,分别为低于100kbps 的标准模式、低于400kbps的快速模式和低于3. 4Mbps 的高速模式。

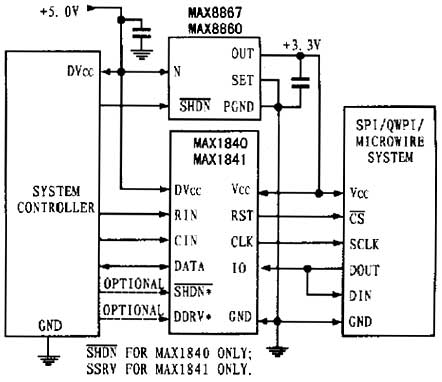

在单向电平转换器件中, 对于那些能够将较高逻辑电平转换成较低逻辑电平的器件, IC制造商规定了器件所允许的输入范围,在规定的输入范围内,器件能够将其输入嵌位在过压容限内。由于具有输入过压保护的逻辑器件能够承受的输入电压高于其供电电压,因此,这些器件简化了高逻辑电平至较低逻辑电平(Vcc 逻辑电平) 的转换方案。而在高扇出或高容性负载连接器的设计中, 任何逻辑器件在降低电源电压的同时,其输出驱动能力也随之降低,只有3. 3V CMOS/ TTL 与5V标准TTL 之间的转换是一个特例。因为3. 3V 逻辑与5V 逻辑的门限是相同的。SPI 总线既需要较高逻辑电平至较低逻辑电平的转换, 也需要将较低逻辑电平转换到较高的逻辑电平。例如在处理器采用1. 8V 逻辑而外设逻辑为3. 3V时。当然, 利用上述分立方案也可以实现这种转换, 但MAX1840/ MAX1841 或MAX3390 等单片方案则可大大简化设计过程,如图所示:

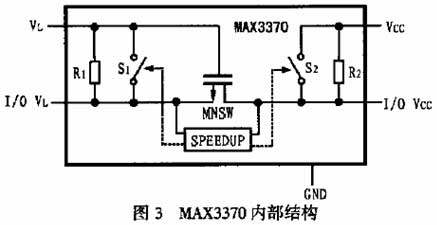

在通过并行总线进行电平转换时, 由于通常已存在WR 和RD 信号, 因而可以采用总线开关(如74CBTB3384) 来实现不同逻辑电平之间的数据连接。对于单总线或2 线接口,一般需要考虑两个问题:一是要有单独的使能控制引脚来控制数据流向(占用有效的控制端口) ,二是芯片尺寸较大(占据较大的线路板尺寸) 。任何设计都存在正、反两个方面的影响,但设计人员通常希望其能够工作在任何逻辑电平,也就是希望其是一个既可实现由高电压逻辑至低电压逻辑的转换,也可实现低电压逻辑至高电压逻辑的转换, 既可完成单向电平转换, 也能完成双向电平转换的通用器件。新一代双向电平转换器MAX3370 即可胜任上述工作, 无论它工作在低电压逻辑, 还是工作在高电压逻辑,均可依靠外部输出驱动吸入电流来实现电平转换的栅极传输(图3) 。这种结构使该器件既可工作于漏极开路输出级, 也可工作于推挽式输出级。而且,MAX3370 具有相当低的导通电阻(低于135Ω) ,对数据传输速率的影响很小。下图是MAX3770 的内部结构, 该器件具有两个优点: 首先对于漏级开路拓扑, MAX3370 内部的10kΩ 上拉电阻与“加速”开关的并联电路既省去了外部上拉元件, 也减小了由于RC 时间常数造成的纹波。在大多数漏极开路输出电路中,数据速率受RC 时间常数的影响较大。而采用独特“加速”结构的MAX3770 则大大提高了数据上升沿的上拉速,减小了容性负载的影响, 其允许数据速率高达2Mbps ,因而大大改善了传统设计的性能; 其次, 由于MAX3370 器件采用的是微型SC70 封装,因此可有效节省线路板的空间。

MAX3370 可以实现最低1. 2V、最高5. 5V 逻辑电平的转换, 能够满足绝大多数设备对电平转换的要求。需要说明的是: MAX3370 仅提供单线通用逻辑电平转换。如果设计中存在多个I/ O 口线,则应参照表1 选择其它芯片。随着系统I/ O 电压数量的增多, 电平转换的设计也更加复杂。设计时需要综合考虑容性负载、Vcc压差的幅度和数据速率等问题。对于从较高逻辑电平至较低逻辑电平的转换, 只要保证电平转换中的Vcc 压差符合器件所允许的容限即可。而在处理低电压逻辑至高电压逻辑的转换, 且同时存在较大的Vcc 压差时,问题将变得非常棘手。双向电平转换或漏极开路输出结构都对数据速率的制约较大, 而Maxim的电平转换器则利用其独特的电路结构简化了电平转换的设计。它能够在较宽的电压范围实现单向、双向电平转换,并可提供漏极开路或推挽式输出。这些器件采用微小的封装形式, 不需要任何外部元件,同时可大大节省线路板空间。

非常好我支持^.^

(105) 99.1%

不好我反对

(1) 0.90000000000001%

相关阅读:

- [电子说] 一种用于高精度测量应用的低功耗模数转换器(ADC)解决方案 2023-10-24

- [电子说] 振弦传感器和信号转换器在桥梁安全监测中的重要性 2023-10-24

- [电子说] 既然ODR能控制管脚高低电平,为什么还需要BSRR寄存器呢? 2023-10-24

- [电子说] ARM系列-P Channel简析 2023-10-24

- [电子说] 川土微电子发布CA-IS3115AW-Q1 DC-DC转换器芯片 2023-10-24

- [电子说] 失调误差是如何影响单极性ADC传递函数的? 2023-10-24

- [电子说] 电流模式升压DC-DC转换器FP6296介绍 2023-10-24

- [电子说] 对于波形和电平不标准的时钟信号一般应进行怎样的处理? 2023-10-24

( 发表人:admin )