Mentor Graphics的PCB设计复用方法

引言 随着科技的不断发展,PCB板趋向小型化、多层化与复杂化。特别是高速印制板,需要

2008-03-22 17:49:24 1770

1770

Mentor Graphics应用之PCB设计复用

引言 随PCB板趋向小型化、多层化与复杂化。特别是高速印制板,需要经过很长时间的反复调试才可以定型

2010-04-28 18:04:23 1538

1538

Cadence宣布业内首个DDR4 Design IP解决方案在28纳米级芯片上得到验证

2012-09-10 09:53:24 1403

1403 Mentor Graphics公司(纳斯达克代码:MENT)今天宣布支持低功率逐步求精方法,通过采用 Questa Power Aware Simulation 和 Visualizer Debug Environment 的新功能以显著提升采用 ARM® 技术的低功率设计的验证复用和生产率。

2015-09-11 15:25:20 1090

1090 Mentor Graphics公司(纳斯达克代码:MENT)今日宣布,即将推出可兼容 AMD 嵌入式 R 系列处理器的 Mentor® Embedded Linux®运行软件和开发工具。第二代

2015-11-06 11:02:16 1060

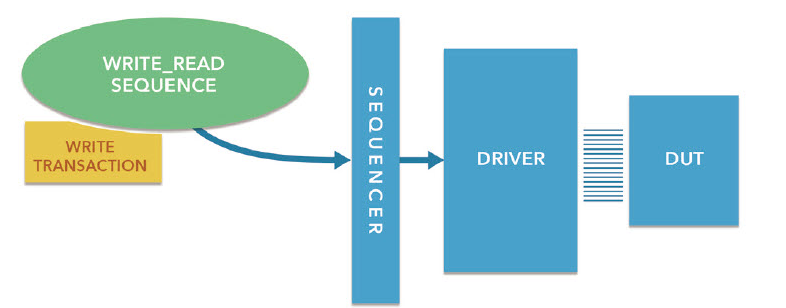

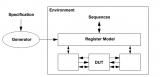

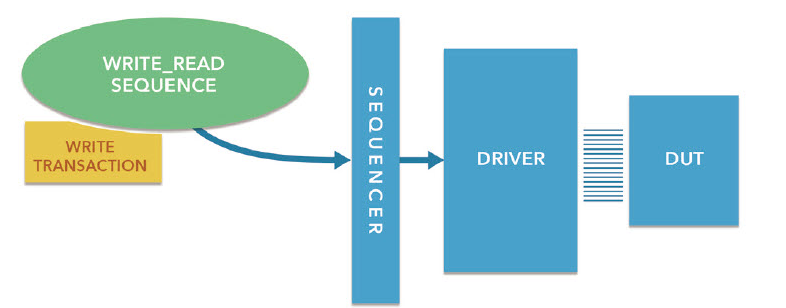

1060 SystemVerilog通用验证方法(UVM)是一种生成测试和检查结果以进行功能验证的有效方法,最适合用于块级IC或FPGA或其他“小型”系统。在UVM测试台中,大多数活动是通过编写序列来生

2021-04-09 16:09:11 3584

3584

Calibre物理验证系列〓 Calibre DRC 作为工作在展平模式下的设计规则检查(DRC)工具,Calibre DRC先展平输入数据库,然后对展平的几何结果进行操作。〓 Calibre

2018-08-28 11:58:29

SystemVerilog 的VMM 验证方法学教程教材包含大量经典的VMM源代码,可以实际操作练习的例子,更是ic从业人员的绝佳学习资料。SystemVerilog 的VMM 验证方法学教程教材[hide][/hide]

2012-01-11 11:21:38

什么是UVM交互式调试库

2020-12-17 07:34:46

各位请问谁有mentor graphics HyperLynx V7.0或者mentor graphics HyperLynx V8.0,可否发一份给我或者发个资源链接,包括破解文件的,谢谢了!邮箱shuaigogo@yeat.net。

2014-03-15 09:51:16

2006 年创建的验证方法和基类库,它是 OVM 和 UVM 的前身。它为组件层次结构和 TLM 通信提供了一个框架,为 SystemVerilog 验证环境提供了标准化的使用模型。不建议将 AVM 用于

2022-02-13 17:03:49

的加数和被加数中分别输入1,即输入1+1时,期望DUT输出2。当DUT在计算1+1的结果时,验证平台也必须相应完成同样 的过程,也计算一次1+1。在验证平台中,完成这个过程的是参考模型(reference

2020-12-02 15:21:34

加入factory机制 上一节《IC验证"一个简单的UVM验证平台"是如何搭建的(五)》给出了一个只有driver、使用UVM搭建的验证平台。严格来说这根本就不算是UVM验证

2020-12-08 12:07:21

通过new()来通知SystemVerilog的仿真器:请创建一个A的实例。仿真器接到new的指令 后,就会在内存中划分一块空间,在划分前,会首先检查是否已经预先定义过这个类,在已经定义过的情况下

2020-12-04 15:48:19

什么?验证工程师验证工程师能够从本书学会如下内容:如何用UVM搭建验证平台,包括如何使用sequence机制、factory机制、callback机制、寄存器模型(register model)等。一些

2020-12-01 15:09:14

在上一节中,**《IC验证"UVM验证平台加入factory机制"(六)》**虽然输出了“main_phase is called”,但是“data is drived”并没有

2020-12-09 18:28:15

: +define+MACRO 或者: +define+MACRO=100扩展寄存器模型中的数据位宽:`define UVM_REG_DATA_WIDTH 128扩展寄存器模型中的地址位宽:`define

2020-12-02 15:24:35

& IP Core Verification)”卷。 本章介绍了 IC 和 IP 核设计过程验证中涉及的一些关键 Python 方法、工具、包和库,包括以下章节: 纯 Python

2022-11-03 13:07:24

:· 验证平台架构:以UVM验证平台为例。实际上,现在IC行业内,很多公司的验证环境都不尽相同,比如有纯C/C++的环境,有纯UVM的环境,有UVM+C++的环境,甚至还有systemc的环境。总的来说

2017-05-17 12:50:39

大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源?本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的uvm测试平台的结构。我们一个

2022-02-14 06:46:33

Systemverilog [1]和 UVM [2]为验证团队提供结构和规则。它使得在许多测试中能获得一致的结果,并可以在团队之间共享验证。许多验证团队都在使用由C代码编写的验证套件。本文将讨论将基于C的测试和验证套件集成到常规UVM测试平台的各种方法。

2020-12-11 07:59:44

Systemverilog [1]和 UVM [2]为验证团队提供结构和规则。它使得在许多测试中能获得一致的结果,并可以在团队之间共享验证。许多验证团队都在使用由C代码编写的验证套件。本文将讨论将基于C的测试和验证套件集成到常规UVM测试平台的各种方法。

2020-12-15 07:38:34

请教各位大佬,UVM是基于sv的验证方法学,如果采用systemc语言编程,如何实现?

2019-11-07 15:30:16

Text/Graphics内存,从而在没有图形缺陷的情况下完成这项工作。我最初的(工作没有故障)内存设置如下:0x0000->0x07FF:Text Memory0x0800->0x0FFF

2019-07-25 11:38:28

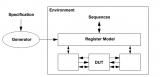

),通常也叫寄存器模型,顾名思义就是对寄存器这个部件的建模。本文要介绍的内容,包括对UVM寄存器模型的概述,如何构建寄存器模型,以及如何将寄存器模型集成到验证环境中。篇幅原因,将在下一篇文章再给出寄存器

2022-09-23 14:29:03

的软件模拟器作为验证的第一站。Mentor Graphics验证IP(VIP)是一个可复用组件库,无缝集成到使用UVM、OVM、Verilog、VHDL和SystemC构建的测试平台,也可与第三方软件

2017-04-05 14:17:46

有条理,我们要在验证计划当中明确要搭建什么样的验证平台,目前主流的验证平台有基于verilog的印证平台,基于systemverilog的验证平台,以及适用uvm方法学建立的验证平台,据uvm验证方法

2021-01-21 15:59:03

?uvm的特点以及uvm为用户提供了哪些资源?什么是uvm呢?uvm是通用验证方法学的缩写,是为验证服务的,uvm是基于systemverilog语言来实现的,因此,在学习uvm之前,应当

2021-01-21 16:00:16

大家好,我是一哥,上章内容我们介绍什么是uvm?uvm的特点以及uvm为用户提供了哪些资源? 本章内容我们来看一看一个典型的uvm验证平台应该是什么样子的,来看一个典型的uvm测试平台的结构

2021-01-22 15:32:04

的transaction,以及创建用于产生事物的事物发生器sequence。 在uvm验证平台中穿梭各个组件之间的基本信息单元是一个被称为transaction的数据对象,也就是我们前面所说的事物

2021-01-26 10:05:37

测试案例中完成的。因此在构建env的时候,需要事先定义好配置接口,是env具有可配置性。 uvm不仅为验证工程师提供了测试平台的结构,而且在uvm的资源库当中。对于平台中的每一个组件啊都有一个对应

2021-01-22 15:33:26

新增加和更新下面的ASIC IP cores,需要的可以联系:williamnk8@gmail.com1. Synopsys Superspeed

2010-05-24 15:25:53

新手学习SystemVerilog & UVM指南 从刚接触System Verilog以及后来的VMM,OVM,UVM已经有很多年了,随着电子工业的逐步发展,国内对验证人才的需求也会急剧增加

2015-03-11 16:24:35

` 2014年6月2日-4日,海基科技应邀前往意大利“汽车城”都灵,参加合作伙伴MentorGraphics全球代理商大会。大会上,海基科技再一次蝉联Mentor Graphics全球铂金代理的称号

2014-07-02 13:51:24

、包和库,特别是半导体知识产权 (IP) 核心设计过程,包括以下章节:验证方法——概述验证方法——简介验证 IP - 方法论的作用如何选择验证方法基于标准的 IP 和 SoC 的验证方法功能验证方法

2022-11-26 20:43:20

HDL 编写)来验证我们的设计。我们的门数每天都在增加,因此它们的验证成了严峻的挑战。过去,验证是使用设计语言完成的。我们创建了“测试台”,将预定的输入应用于我们的设计模型,并将生成的输出与设计人

2022-02-16 13:36:53

猎头职位:IC验证工程师【北京】岗位职责:1.根据芯片架构文档和设计要点,制定验证方案,拟定验证计划;2.根据验证方案和计划,实施验证,包括编写参考模型、搭建仿真验证平台与迭代改进、编写完备的验证

2017-02-15 13:39:33

uvm_object基类扩展得到。UVM sequences不是在仿真的开始,而是在仿真的过程中生成并分配内存的,也没有类似uvm_component的层次结构。随着仿真的进行,将创建一个或多个UVM

2022-04-11 16:43:42

2BA4 Mentor Graphics Tutorial V1.0

1.1 Library ManagerOpen the Library Manager shown in Fig. 1.1

2009-03-28 16:09:55 34

34 Mentor Graphics 公司线缆线束设计解决方案CHS明导(上海)电子科技有限公司供稿CHS(Capital Harness System)是国际著名EDA 厂商Mentor Graphics 公司专为航空、航天、车辆等领域开发

2009-12-21 10:12:24 0

0 我们在工作中涉及到对Audio Circuit (ADC, DAC 等)的设计验证,主要用到Mentor Graphics 的仿真工具。这里是一些使用经验与大家分享与讨论:我们先用ADVance MS (ADMS)进行混合仿真,后

2010-07-04 11:34:24 79

79 Open Verification Methodology(OVM)是Mentor Graphics 和Cadence 共同推出的,业界第一个基于SystemVerilog、通用开放的验证方法学;其基于事务交易级的方法学,基于Factory Pattern 的对象生

2010-07-04 11:43:22 7

7 印刷电路板(PCB)设计解决方案市场和技术领军企业Mentor Graphics(Mentor Graphics)宣布推出HyperLynx® PI(电源完整性)产品,满足业内高端设计者对于高性能电子产品的需求。HyperLynx

2010-10-07 12:11:36 0

0 这些术语支持Mentor Graphics PCB产品文档在术语表当中,一些是Mentor Graphics PCB产品独有的,另外一些是PCB行业标准。

2010-11-24 15:56:30 0

0 Mentor Graphics, 全球电子软硬件设计解决方案的领先企业, 近日宣布TATA汽车系统公司( TACO)采用了Mentor Graphics CHS电子线束设计工具。TACO是印度TATA集团旗下企业,

2009-04-04 10:53:18 1113

1113 德国控创集团采用Mentor Graphics的电源完整性解决方案获

Mentor Graphics宣布,德国控创集团(Kontron)已将该公司所部署的Expedition EnterprisePCB,扩展到Mentor对于信号和电源完整

2010-01-14 08:46:04 1225

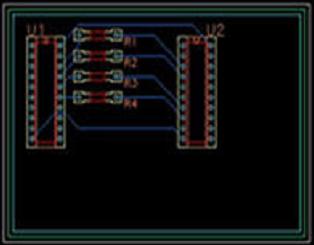

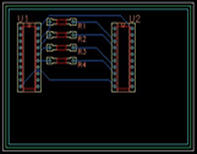

1225 Mentor Graphics Board Station PCB设计复用方法

本文介绍了一种 PCB 设计复用方法,它是基于 Mentor Graphics 的印制电路板设计工具 Board Station 进行的。一个设

2010-03-21 18:33:10 2747

2747

参考流程 8.0 版(Reference Flow 8.0)提供高级DFM 性能WILSONVILLE, Ore. and HSINCHU, Taiwan – 2007 年6 月5 日 –明导公司 (Mentor Graphics 纳斯达克代号: MENT) 与台湾半导体制造

2010-06-20 11:14:03 1112

1112 Mentor Graphics(Mentor Graphics)推出HyperLynx PI(电源完整性)产品,满足业内高端设计者对于高性能电子产品的需求。HyperLynx PI产品不仅提供简单易学、

2010-09-20 00:03:29 464

464 文章主要介绍《VMM for SystemVerilog》一书描述的如何利用SystemVerilog语言,采用验证方法学以及验证库开发出先进验证环境。文章分为四部分,第一部分概述了用SystemVerilog语言验证复杂S

2011-05-09 15:22:02 52

52 飞思卡尔半导体公司 (NYSE:FSL) 选择 Mentor Graphics Corporation (NASDAQ:MENT) 开发包含高级算法和信号处理功能的软件库,该软件库专门针对最新版飞思卡尔AltiVec处理引擎进行优化。面向飞思卡尔

2011-09-15 18:37:27 1079

1079 文中分析了基于Systemverilog验证环境的结构,并在介绍I 2 C总线协议的基础上,重点论述了验证环境中事务产生器及驱动器的设计。

2011-12-22 17:20:21 27

27 以创建6位D/A转换器和TTL7458原理图模型为例,论述创建Proteus原理图仿真模型的思路与方法、模型存库与从库中调用他的方法和对创建模型进行验证的方法。经验证证明所建模型和建模方

2012-03-28 15:10:25 95

95 Mentor Graphics 公司(纳斯达克代码:MENT)今天宣布推出最新 Xpedition® Package Integrator 流程,这是业内用于集成电路 (IC)、封装和印刷电路板 (PCB) 协同设计与优化的最广泛的解决方案。

2015-03-24 12:03:16 1684

1684 俄勒冈州威尔逊维尔,2015 年 4 月 6 日—Mentor Graphics公司(纳斯达克代码:MENT )今天宣布,TSMC和Mentor Graphics已经达到在10nm EDA认证合作的第一个里程碑

2015-04-20 14:18:06 1658

1658 Mentor Graphics 公司(纳斯达克代码:MENT)今天宣布,Mellanox Technologies 已将全新的 Mentor® Tessent® 阶层化 ATPG 解决方案标准化

2015-05-19 17:12:05 1762

1762 Mentor Graphics公司(纳斯达克代码:MENT)今天正式发出第 26 届年度技术领导奖 (TLA) 大赛的参赛邀请,这一大赛延续了该公司一直以来表彰卓越印刷电路板 (PCB) 设计的传统

2015-09-15 10:39:28 857

857 Mentor Graphics公司(纳斯达克代码:MENT)今天宣布推出支持 25G、50G 和 100G 以太网的 Veloce® VirtuaLAB 以太网环境。这种支持可为目前基于大规模以太网的设计提供高效、基于硬件仿真的验证。

2015-10-30 14:49:27 777

777 Mentor Graphics 公司(纳斯达克代码:MENT)今日宣布推出面向 ARM AMBA 5 AHB 片上互连规范的验证 IP (VIP)。该新 VIP 在 Mentor® 企业验证平台

2015-11-12 11:28:11 1132

1132 俄勒冈州威尔逊维尔,2016 年 2 月 23 日 — Mentor Graphics公司(纳斯达克代码:MENT)今日宣布,美国联邦巡回上诉法院支持以下主张:Mentor Graphics® 开发的硬件仿真技术(美国专利号为: 6,240,376 号)由Mentor Graphics享有专利权。

2016-02-23 11:10:05 1178

1178 美国俄勒冈州威尔逊维尔和英国剑桥,2016 年 2 月 25 日 - Mentor Graphics 公司(纳斯达克代码:MENT)已与 ARM(伦敦证券交易所代码:ARM;纳斯达克代码:ARMH)签订一份多年订购协议,以尽早获得各种 ARM IP 和相关技术。

2016-02-26 10:54:49 457

457 WILSONVILLE, Ore., 2016年3月15日— Mentor Graphics公司(纳斯达克代码:MENT)今天发布了一款结合设计、版图布局和验证的解决方案,为TSMC集成扇出型 (InFO) 晶圆级封装技术的设计应用提供支持。

2016-03-15 14:06:02 988

988 Mentor Graphics公司(纳斯达克代码:MENT)今天宣布,借由完成 TSMC 10 纳米 FinFET V1.0 认证,进一步增强和优化Calibre® 平台和 Analog

2016-03-24 11:13:19 816

816 俄勒冈州威尔逊维尔,2016 年 4 月 5 日—Mentor Graphics公司(纳斯达克代码:MENT)今日宣布推出最新版 HyperLynx®,该版本将信号和电源完整性分析、三维电磁解析和快速规则检查集成到一个统一的环境中。

2016-04-05 09:49:41 2282

2282 俄勒冈州威尔逊维尔,2016 年 4 月 13 日 – Mentor Graphics公司(纳斯达克代码:MENT)今天宣布,将与网络测试、可见性和安全解决方案的领先提供商 Ixia 携手合作

2016-04-13 11:05:07 1299

1299 俄勒冈州威尔逊维尔,2016 年 4 月 20 日 — Mentor Graphics公司(纳斯达克代码:MENT)今日宣布,Mentor® 硬件加速仿真服务采用具有专业服务和 IP 的 Veloce® 硬件加速仿真平台 ,借此加速仿真验证并降低与片上系统 (SoC) 设计相关的风险。

2016-04-20 11:22:08 2307

2307 Mentor Graphics 公司(纳斯达克代码:MENT)为 Verification Academy 增加全新的 SystemVerilog 课程和模式库以帮助验证工程师提高专业技能、生产率及设计质量。

2016-08-10 11:20:24 1878

1878 基于UVM的CPU卡芯片验证平台_钱一文

2017-01-07 19:00:39 4

4 基于UVM的验证平台设计研究_王国军

2017-01-07 19:00:39 4

4 基于UVM的CAN模块自验证方法_熊涛

2017-01-08 14:47:53 3

3 一种基于UVM的混合信号验证环境_耿睿

2017-01-07 21:39:44 1

1 UVM使得验证测试平台的结构得以标准化,各种复用策略及标准对于提高验证质量、缩短项目周期都非常有效。垂直重用是常见的复用策略之一,即同一项目测试平台复用于不同验证层次。验证中常将最底层的IP级验证平台向更高的集成层复用,而UVM寄存器模型则是验证平台复用的一个关键部分。

2017-09-15 11:49:08 15

15 的连接、驱动器、监视器、仿真序列以及功能覆盖率的建立。 本文呈现出了一种使用UVM验证方法学构建基于高可配置性的高级微处理器总线架构(AMBA)的IP验证环境,其中会使用到Synopsys公司的AMBA VIP和Ruby脚本。该验证环境可以支持通过使用AMBA设计参数进行自

2017-09-15 14:37:34 6

6 UVM已经成为了一种高效率的、从模块级到系统级完整验证环境开发标准,其中一个关键的原则是UVM可以开发出可重用的验证组件。获得重用动力的一个方面表现为标准的仿真器和硬件加速之间的验证组件和环境的复用

2017-09-15 17:08:11 14

14 解决方案的全球主导厂商,采用Mentor Graphics Eldo电路仿真器来进行其首次CMOS 32nm元件库特性分析。在数字和模拟IP特性分析的先进电路仿真技术领域,两家公司是长期的合作伙伴。这一

2017-12-04 11:55:38 385

385 Wallace说,“ARM一直使用在Questa和Veloce上运行的Mentor PCIe VIP库来帮助验证PCIe与ARM AMBA接口域之间的关键交互,以实现快速部署和准确的协议检查。”

2018-06-05 14:19:00 4313

4313 电子设计自动化技术的领导厂商 Mentor Graphics 近日发布一份《让你的工程师自由创新》的研究报告。中文版的报告全文可在Mentor Graphics的官方网站阅读和下载。

2018-03-20 15:07:00 678

678

Mentor Graphics的Tanner EDA软件是一套针对定制集成电路(IC)、模拟/混合信号(AMS)和MEMS设计的产品。对物联网(IoT)需求的突然上升使全流程混合信号设计环境面临独特的要求:经济实惠且易于使用,但功能强大,可创建部署物联网所需的各类产品。

2018-05-29 14:46:00 6644

6644

2011 ARM Techcon上,Mentor Graphics总监Mark为我们介绍了Mentor Graphics的产品线。

2018-06-26 10:59:00 4429

4429 2011ARM Techcon上,Mentor Graphics的商业战略部总监Dennis为我们介绍了近一年来Mentor Graphics与ARM的合作。

2018-06-26 10:40:00 2693

2693 新思科技(Synopsys,Inc.纳斯达克股票代码:SNPS)近日宣布为DDR5/4非易失性双列直插式内存模块(NVDIMM-P),推出业内首个验证IP (VIP)。NVDIMM-P是新一代存储

2019-05-17 09:43:48 3182

3182 本文描述了一个符合验证方法手册(VMM)的基于SystemVerilog事务的测试平台,并通过实例说明了使用基于事务的方法创建一个全面的约束随机验证环境中的VMM方法。这包括交易的生成和通过交易

2019-05-28 08:00:00 2

2 验证IP旨在通过为常见接口、协议和架构提供可复用构建模块来帮助工程师减少构建测试平台所花费的时间。Mentor的内存验证IP模型库所包含的内存配置软件允许客户根据供应商、协议和元件编号,即时生成快速

2019-10-12 09:25:50 2435

2435 读者思考UVM为什么要引入这些机制,从而使读者知其然,更知其所以然。本书以一个完整的示例开篇,使得读者一开始就对如何使用UVM搭建验证平台有总体的概念。针对没有面向对象编程基础的用户,本书在附录中简要介绍了面向对象的概念及SystemVerilog中区别于其他编程语言的一些特殊语法。

2019-11-29 08:00:00 28

28 明导国际(Mentor Graphics,纳斯达克代码:MENT)推出了Eldo® Premier工具,这是目前业内最快的SPICE仿真解决方案之一。

2019-12-02 14:40:25 2830

2830 Mentor Graphics是电子设计自动化(EDA)技术的领导产商,它提供完整的软件和硬件设计解决方案,是全球三大EDA大佬之一。Mentor 除EDA工具外,还具备非常多助力汽车电子厂商的产品,包括嵌入式软件等。

2020-07-02 13:20:00 2141

2141 Express 5.0的物理层和电气接口。 新思科技CXL验证IP基于新一代SystemVerilog的 Universal Verification Methodology(UVM)架构,使验证IP的集成

2020-12-26 11:04:10 2456

2456 手册的这一部分探讨了使用SystemVerilog进行验证,然后查看了使用SystemVerilog的优点和缺点。

2021-03-29 10:32:46 23

23 利用Systemverilog+UVM搭建soc验证环境

2022-08-08 14:35:05 5

5 class,是面向对象编程(object-oriented programming (OOP))的基础,而OOP可以让你创建更高抽象级别的验证环境(如UVM)。

2022-11-14 09:11:49 1334

1334 class,是面向对象编程(object-oriented programming (OOP))的基础,而OOP可以让你创建更高抽象级别的验证环境(如UVM)。

2022-11-14 09:11:07 692

692 百度百科对UVM的释义如下:通用验证方法学(Universal Verification Methodology, UVM)是一个以SystemVerilog类库为主体的验证平台开发框架,验证工程师可以利用其可重用组件构建具有标准化层次结构和接口的功能验证环境。

2022-11-30 12:47:00 1060

1060 因为DUT是一个静态的内容,所以testbench理应也是静态的,其作为uvm验证环境和DUT的全局根结点。

2023-03-21 11:33:02 982

982 本文使用Easier UVM Code Generator生成包含多个agent和interface的uvm验证环境。

2023-06-06 09:13:02 584

584 UVM register layer classes用于为DUV中的memory-mapped寄存器和内存的read/write操作创建一个 high-level 和 object-oriented

2023-06-23 21:30:28 211

211

FPGA验证和UVM验证在芯片设计和验证过程中都扮演着重要的角色,但它们之间存在明显的区别。

2024-03-15 15:00:41 94

94

电子发烧友App

电子发烧友App

评论