。静态时序分析工具很好地解决了这两个问题。它不需要激励向量,可以报出芯片中所有的时序违例,并且速度很快。 通过静态时序分析,可以检查设计中的关键路径分布;检查电路中的路径延时是否会导致setup违例;检查电路中是否由

2020-11-25 11:03:09 8918

8918

在fpga工程中加入时序约束的目的: 1、给quartusii 提出时序要求; 2、quartusii 在布局布线时会尽量优先去满足给出的时序要求; 3、STA静态时序分析工具根据你提出的约束去判断

2020-11-25 11:39:35 5320

5320

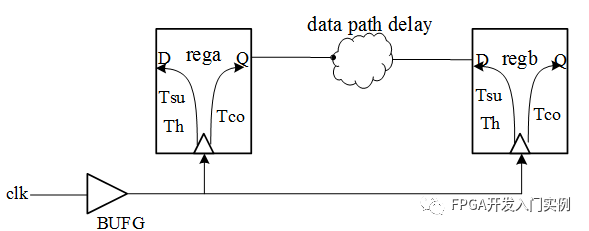

静态时序分析包括建立时间分析和保持时间分析。建立时间设置不正确可以通过降低芯片工作频率解决,保持时间设置不正确芯片无法正常工作。

2022-08-22 10:38:24 3289

3289 同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

2023-06-28 09:35:37 490

490

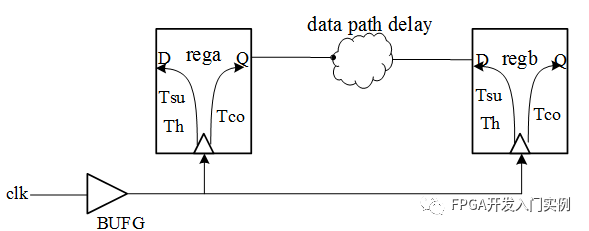

下图是一个经典时序分析模型,无论寄存器A与寄存器B是否在同一个芯片中,下列概念均适用。

2023-07-03 15:37:08 656

656

互通性测试,向商用迈出了坚实的一步。 然而对于手机芯片企业来说,仅仅克服多频段兼容和多模兼容还远远不够,一颗5G基带芯片的研发还需要攻克包括系统散热、架构和高速率低时延等在内的多个难关。5G终端的处理

2019-09-17 09:05:06

AD6900是一款低功耗无线数字基带芯片,它的高级电源管理系统满足了GSM、GPRS和EDGE终端的严格要求,还支持对计算量要求很大的多媒体功能。集成了BlackfinDSP处理

2021-04-13 07:30:36

数字基带信号处理实验 一、实验目的 1、熟悉该系统的时钟信号与各种定时信号的产生方法。 &

2009-10-11 08:54:51

数字芯片设计流程:功能验证之前与工艺库没多大联系,验证芯片设计的功能是否正确,针对抽象的代码进行功能验证理想值。一致性验证确保生成的网表和代码设计功能一致;DFT之后是数字后端。静态时序分析,从逻辑

2021-11-10 06:14:28

芯片要求如图片中的时序,通过数组生成如图数字波形后,芯片不能输出,数字时钟为默认的1k左右,感觉这个地方可能有问题,请大神指点

2016-05-06 11:51:28

数字信号时序分析装置毕业设计,本人来自中国地质大学通信工程专业,2020学年大二上的通信与信号处理的实习题目便是参考2018年TI杯G题——数字信号时序分析装置,此实习需要自学stm32单片机,具有

2021-08-09 08:33:45

在进行数字电路系统的设计时,时序是否能够满足要求直接影响着电路的功能和性能。本文首先讲解了时序分析中重要的概念,并将这些概念同数字系统的性能联系起来,最后结合FPGA的设计指出时序约束的内容和时序

2020-08-16 07:25:02

(path groups):时序路径可以根据与路径终点相关的时钟进行分类,因此每个时钟都有一组与之相关的 时序路径 。静态时序分析和报告通常分别在每个时序路径组中单独执行。注意: 除了上述与时钟相关的时序

2023-04-20 16:17:54

静态时序分析STA是什么?静态时序分析STA的优点以及缺点分别有哪些呢?

2021-11-02 07:51:00

静态时序分析与逻辑设计

2017-12-08 14:49:57

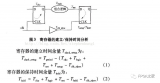

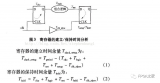

本文提出新的Π模型方法,结合了门的等效电容来计算门的延时,我们的方法结合门的互连线负载的拓扑结构和门负载三阶矩求解的方法,采用中提出的等效电容的求解公式,求出门延时计算模型,相比上述两种方法,在静态时序分析中更为合理。

2021-04-23 07:04:07

不能保证100%的覆盖率。如果到了门级的仿真将非常消耗时间。 静态时序分析静态时序分析只能分析时序要求而不能进行功能验证。不需要测试向量,能比动态时序分析快地多的完成分析。静态时序分析只能对同步电路

2021-09-04 14:26:52

某16K x 4的存储体由16个字长为1的 DRAM芯片在位方向和字方向同时扩展而成,DRAM芯片中所有的记忆单元排列成行列相等的存储矩阵。分析:由题得,16个DRAM芯片需要先在位方向扩展为4位得

2022-03-02 06:18:45

1. 适用范围 本文档理论适用于Actel FPGA并且采用Libero软件进行静态时序分析(寄存器到寄存器)。2. 应用背景 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计

2012-01-11 11:43:06

基本的时序分析理论1本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 何谓静态时序分析(STA,Static

2015-07-09 21:54:41

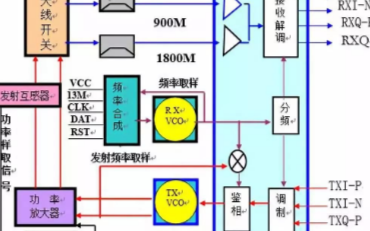

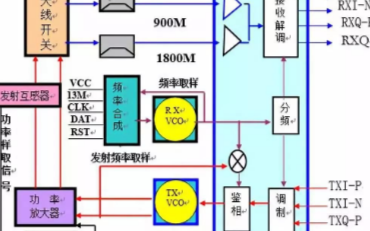

MTK手机基带各种电路的分析和介绍

2012-08-16 15:24:10

MTK手机基带各种电路的分析和介绍

2014-04-10 10:37:16

,SX1301动态数据速率(DDR),SX1308动态数据速率调整(ADR)。SX1308数字基带芯片是一个巨大的数字信号处理引擎,专门设计用于在ISM全球范围内提供突破性网关功能,集成了LoRa集中器IP

2021-04-03 10:07:30

自己做了一个工程,静态时序分析的结果CLK信号的SLACK是负值(-7.399ns),书上说该值是负值时说明时序不对,但是我感觉时序仿真的结果是对的。是不是时序仿真波形正确就不用管静态时序分析的结果了?请高手指点

2010-03-03 23:22:24

iphone高通基带和英特尔基带,声明:针对苹果与高通基带芯片专利纠纷,来了兴致,收集一波信息.以下信息对百度百科的基带芯片进行整理;维基百科没有基带芯片介绍;1 简介基带芯片是用来合成即将发射

2021-07-28 06:42:24

静态时序分析与逻辑设计

2015-05-27 12:28:46

为什么静态时序分析受组件(符号)名称的影响?我在示意图中有一个ISR,当我把它称为“CuttIsIr”时,静态时序分析返回一个警告“设置时间违反”,但是当我称之为“UTHISISR”时,一切都

2019-07-30 10:42:26

挑战。这些收发器可为模拟RF信号链提供数字接口,允许轻松集成到ASIC或FPGA,进行基带处理。基带处理器(BBP)允许在终端应用和收发器设备之间的数字域中处理用户数据。

2019-09-19 06:20:59

摘要:介绍了静态时序分析在数字集成电路设计中的应用,并以100M以太网卡芯片设计为例,具体描述了以太网卡芯片设计中的静态时序分析流程及其时序问题。 关键词:静态时序分析 100M以太网卡 数字

2018-08-28 11:58:31

各位好,初次使用pt对fpga进行静态时序分析,想请教下需要哪些文件。是不是需要:1、在ise或qutartus生成的网表2、SDC文件3、.db文件.db文件必须且只能从dc生成吗,要是从.lib转化而来,这个lib文件在fpga设计时又从哪里得到问题貌似比较多,谢谢回答

2014-12-18 16:15:12

关于静态分析和时序约束的文章

2014-07-17 12:12:35

华为静态时序分析与逻辑设计

2014-05-20 22:55:09

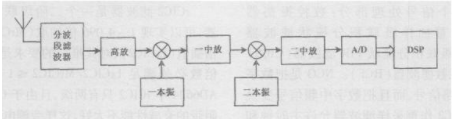

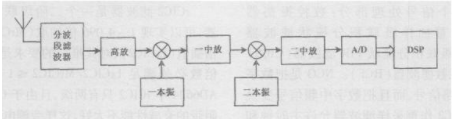

随着数字技术的进步,高速、超大规模集成电路广泛使用,3G移动终端基带信号处理系统正朝着灵活、高度集成化、模块化、通用化的方向发展。基带信号处理器是数字技术与通信技术相结合的产物,它能灵活处理数字基带

2019-07-03 06:18:48

毕业设计题目,毫无头绪,求指导。主要内容:通信原理》课程中,数字基带信号传输码型是最重要的教学内容之一。在传输系统中,需要各种不同的传输码型及其相互变换。该设计要求分析通信系统基带传输的常用码型

2015-02-28 18:09:14

对基带信号进行数字化处理时为什么需使用输入滤波器?

2023-12-21 06:55:35

来至网友的提问:对基带信号进行数字化处理时为什么需使用输入滤波器?

2018-12-12 09:07:39

以下针对目前项目所用到的SRAM时序进行分析,同时也对SRAM应用在STM32F4上进行详细解说。以此也可以类推出NAND/PSRAM等时序的应用技巧。时序当前用到的是模式A,其中读时序如下。图片截

2022-01-07 07:20:20

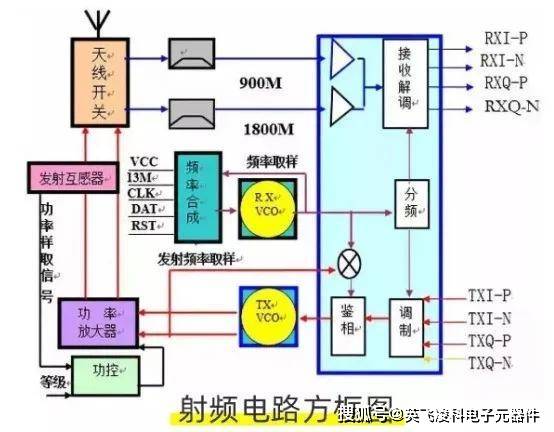

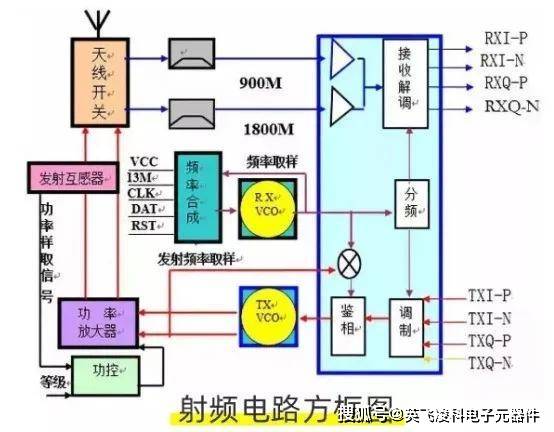

射频芯片和基带芯片的关系是什么?射频芯片是什么工作原理?

2021-06-15 09:16:25

静态时序分析(Static Timing Analysis,STA)是流程成功的关键环节,验证设计在时序上的正确性。STA过程中设计环境和时序约束的设定、时序结果的分析和问题解决都需要设计工程师具有

2020-09-01 16:51:01

而又美好,那么我们这么多学费就没白交哈~ 下面我们进入正题,今天我们讲时序一、从静态时序分析说起 我理解的静态时序分析,就是我们在不加激励的情况下,通过对电路进行时序的延迟计算,预计电路的工作流

2015-03-31 10:20:00

高速电路信号完整性分析与设计—时序计算引入:在数字电路中,从一个芯片发信息A到另一个芯片变成信息B,那么这个数字系统失败;如何保证信息不变?关键点,就是在传输过程的任意点都保持时序的正确性。时序概念

2009-09-12 10:28:42

同步时序数字电路的分析二进制同步计数器 分析步骤: 1.确定电路是否是同步时序数字电路 2.确定触发器的驱动方程 3.做出状态转换表 4.做出分析结论 BC

2008-10-20 10:10:43 30

30 时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 静态时序概念,目的

静态时序分析路径,方法

静态时序分析工具及逻辑设计优化

2010-07-09 18:28:18 129

129 本文首先以Synopsys公司的工具Prime Time SI为基础,介绍了ASIC设计中主流的时序分析方法:静态时序分析及其基本原理和操作流程;接着分析了它与门级仿真之间的关系,提出了几个在T

2010-08-02 16:44:16 10

10

AD6900数字基带处理器在多媒体的设计与应用

多媒体处理,

2010-03-11 15:08:45 901

901

摘要

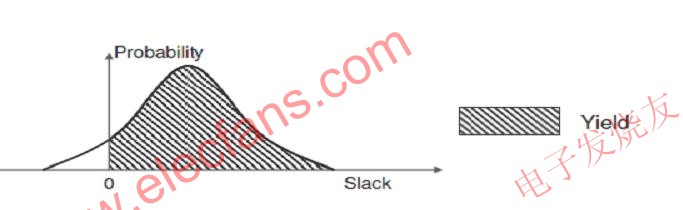

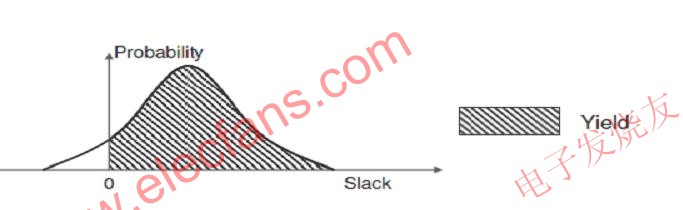

是否曾想过为什么一个设计能够以高于设计团队承诺的频率工作?为何该设计团队不能将这个更高的频率当作要实现的目标?

过去,静态时序分

2010-09-25 09:37:15 4313

4313

在制程进入深次微米世代之后,芯片(IC)设计的高复杂度及系统单芯片(SOC)设计方式兴起。此一趋势使得如何确保IC质量成为今日所有设计从业人员不得不面临之重大课题。静态时序

2011-05-11 16:53:43 0

0 介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对时序不满足的情况,提出了几种常用的促进 时序收敛的方

2011-05-27 08:58:50 70

70 在制程进入深次微米世代之后,芯片(IC)设计的高复杂度及系统单芯片(SOC)设计方式兴起。此一趋势使得如何确保IC质量成为今日所有设计从业人员不得不面临之重大课题。静态时序

2011-05-27 09:02:19 90

90 讨论了静态时序分析算法及其在IC 设计中的应用。首先,文章讨论了静态时序分析中的伪路径问题以及路径敏化算法,分析了影响逻辑门和互连线延时的因素。最后通过一个完整的IC 设计

2011-12-20 11:03:16 95

95 本内容介绍了手机基带相关内容,手机基带是什么,手机基带版本等

2012-05-24 14:48:32 5527

5527 _静态时序分析(Static_Timing_Analysis)基础及应用[1]。

2016-05-09 10:59:26 31

31 华为静态时序分析与逻辑设计,基础的资料,快来下载吧

2016-09-01 15:44:10 56

56 静态时序分析基础及应用

2017-01-24 16:54:24 7

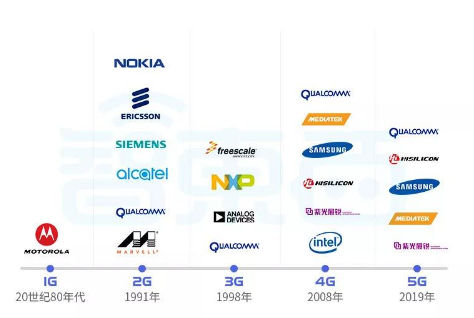

7 目前基带芯片在我们生活中已经得到广泛的运用,本文主要详细介绍了基带芯片的定义与组成,其次也罗列出了基带芯片的六大产商。

2017-12-16 11:54:55 42090

42090 STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。以分析的方式区分,可分为Path-Based及Block-Based两种。

2018-04-03 15:56:16 10

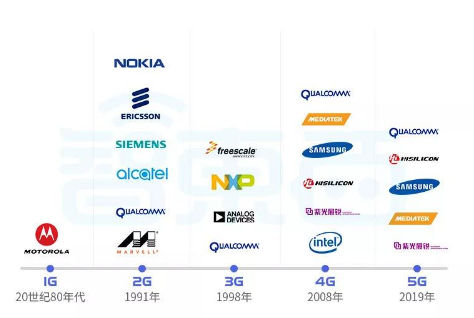

10 随着5G网络的即将商用,手机芯片厂商纷纷抢先推出了自家的5G芯片。手机芯片可以分为射频芯片、基带调制解调器以及核心应用处理器,此前高通、英特尔、三星、华为先后展示了自家的5G基带芯片,并宣布预计将在2019年商用。

2019-01-11 10:09:06 3992

3992 静态时序分析中的“静态”一词,暗示了这种时序分析是一种与输入激励无关的方式进行的,并且其目的是通过遍历所有传输路径,寻找所有输入组合下电路的最坏延迟情况。这种方法的计算效率使得它有着广泛的应用,尽管它也存在一些限制。

2019-11-22 07:11:00 2088

2088 静态时序或称静态时序验证,是电子工程中,对数字电路的时序进行计算、预计的工作流程,该流程不需要通过输入激励的方式进行仿真。

2019-11-22 07:09:00 2103

2103 静态时序分析是一种验证方法,其基本前提是同步逻辑设计(异步逻辑设计需要制定时钟相对关系和最大路径延时等,这个后面会说)。静态时序分析仅关注时序间的相对关系,而不是评估逻辑功能(这是仿真和逻辑分析

2019-11-22 07:07:00 3179

3179 20 X 5G版也将在本周五正式上市。在期待了半年时间后,5G手机终于来了!

5G手机与4G手机相比,在硬件上最大的区别在于5G基带芯片。当下,5G基带芯片领域的第一战已经打响!头部的五家大厂凭借

2019-07-24 08:54:37 9869

9869

德克萨斯州AUSTIN-IC表征提供商Silicon Metrics Corp.将推出基于SiliconSmart Models的产品线。该系列产品包括该公司为逻辑设计人员提供的首个产品 - 一种可延长静态时序分析仪精度的时序签核工具。

2019-08-13 11:37:41 2870

2870 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。

2019-09-01 10:45:27 2942

2942

传统来说,一部可支持打电话、发短信、网络服务、APP应用的手机,一般包含五个部分部分:射频部分、基带部分、电源管理、外设、软件。 射频部分:一般是信息发送和接收的部分; 基带部分:一般是信息处理

2020-06-29 10:54:19 19965

19965

在手机终端中,最重要的核心就是射频芯片和基带芯片。射频芯片负责射频收发、频率合成、功率放大;基带芯片负责信号处理和协议处理。那么射频芯片和基带芯片是什么关系?

2020-07-08 10:17:40 5315

5315 静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58 在手机终端中,最重要的核心就是射频芯片和基带芯片。射频芯片负责射频收发、频率合成、功率放大;基带芯片负责信号处理和协议处理。那么射频芯片和基带芯片是什么关系?

2020-11-20 09:42:16 18653

18653

传统来说,一部可支持打电话、发短信、网络服务、APP 应用的手机,一般包含五个部分部分:射频部分、基带部分、电源管理、外设、软件。射频部分:一般是信息发送和接收的部分;基带部分:一般是信息处理的部分

2020-12-29 04:37:00 65

65 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 18

18 进行静态时序分析,主要目的就是为了提高系统工作主频以及增加系统的稳定性。对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。通过附加约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。

2021-01-08 16:47:25 15

15 任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,我研究了一天,终于找到了一种很简单的解读办法,可以看透它的本质,而且不需要再记复杂的公式了。

2021-01-12 17:48:08 19

19 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告。

进行静态时序分析,主要目的就是为了提高系统工作主频以及增加系统的稳定性。对很多数字

2021-01-12 17:48:07 15

15 在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。此一趋势使得如何确保IC品质成为今日所有设计从业人员不得不面临之重大课题。静态时序分析(Static

2021-01-14 16:04:02 3

3 本文档的主要内容详细介绍的是时序分析的静态分析基础教程。

2021-01-14 16:04:00 14

14 近日,市场研究机构Strategy Analytics在其官方微信公众号发布的最新研究报告指出,2020年Q3,5G基带芯片出货量增长了十倍以上。5G基带芯片处理器收益首次超过4G,并占总基带收益的50%以上。

2021-02-01 15:09:42 1639

1639 AD6528:用于智能手机和无线的GSM/GPRS数字基带处理器初步数据表

2021-04-25 13:40:06 7

7 本文在分析软件无线电的宽带数字中频和数字下变频的基本模型基础上,结合ADI公司推出的接收信号处理器芯片AD6624的工作原理,提出CDMA基站反向链路中基带信号处理的设计方案,并详细讨论了基带滤波器的设计方法,同时给出了仿真结果。

2021-05-25 10:14:02 2708

2708

片内时序约束,要想实现高速信号的有效传输就必须进行片外静态时序分析。本文作为在高速信号处理时信号输入输出的理论参考,之所以说作为理论参考是因为由于高速信号处理,具体的一些参数无法实际计算出来,只能在理论参考的方向

2021-06-18 16:22:26 1183

1183

一、前言 无论是FPGA应用开发还是数字IC设计,时序约束和静态时序分析(STA)都是十分重要的设计环节。在FPGA设计中,可以在综合后和实现后进行STA来查看设计是否能满足时序上的要求。

2021-08-10 09:33:10 4767

4767

知名苹果产业链研究员、天风国际分析师郭明錤透露,苹果为 iPhone 自研的 5G 基带芯片或遭遇失败。

2022-07-18 16:13:02 12383

12383 另一种是手动的方式,在大型设计中,设计人员一般会采用手动方式进行静态时序分析。手动分析方式既可以通过菜单操作(个人理解:通过鼠标点击和键盘输入)进行分析,也可以采用Tcl脚本(工具控制语言,个人理解运用代码控制)进行约束和分析。

2022-08-19 17:10:25 1354

1354 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。STA作为

2022-09-27 14:45:13 1808

1808 对于建立时间和保持时间本文就不再过多叙述,可参考【FPGA】几种时序问题的常见解决方法-------3,可以说在数字高速信号处理中最基本的概念就是建立时间和保持时间,而我们要做的就是解决亚稳态问题和传输稳定问题。

2022-12-13 11:03:58 225

225 任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,终于找到了一种很简单的解读办法,可以看透

2023-03-14 19:10:03 443

443 任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,我研究了一天,终于找到了一种很简单的解读办法,可以看透它的本质,而且不需要再记复杂的公式了。

2023-05-29 10:24:29 348

348

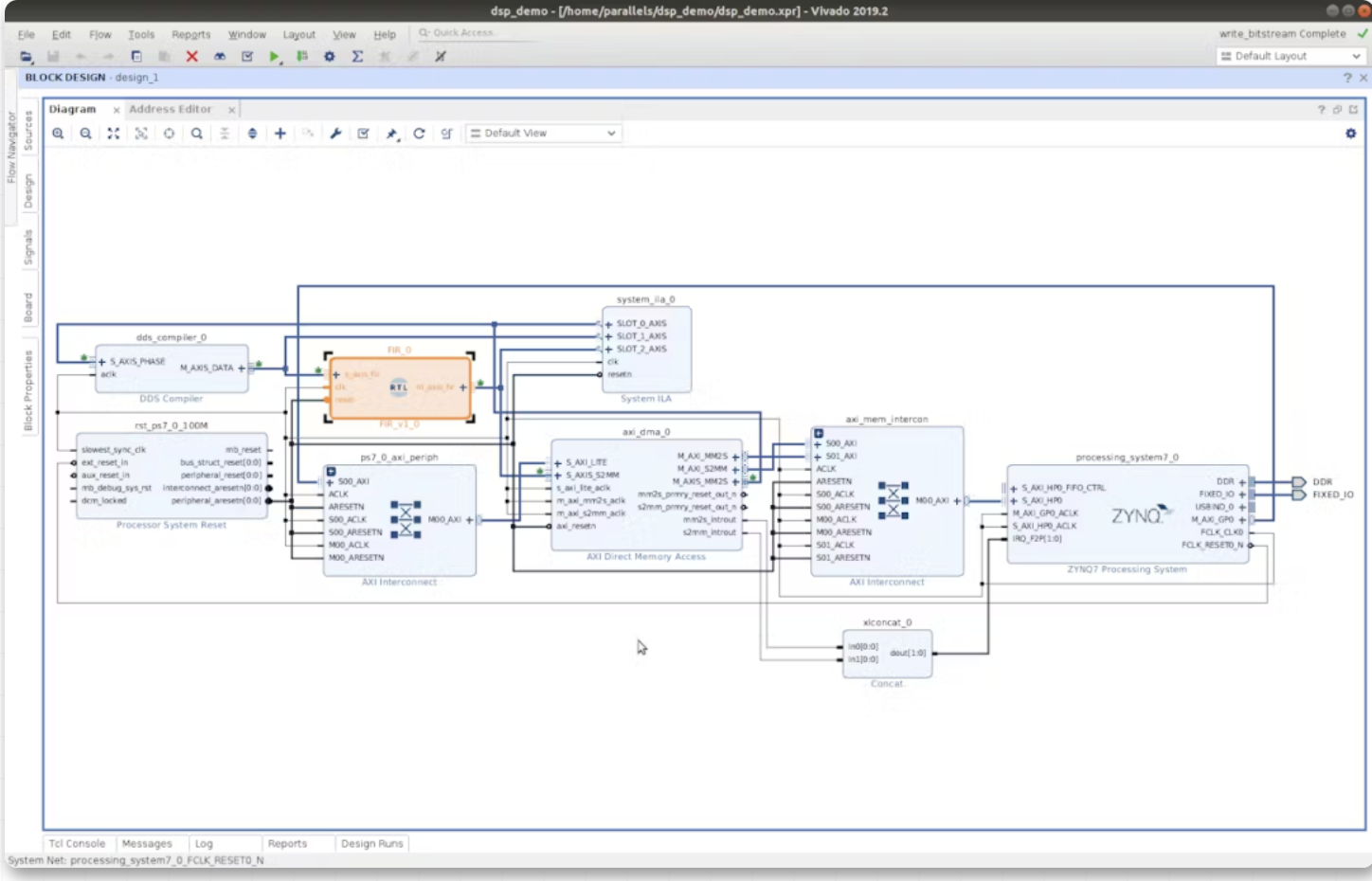

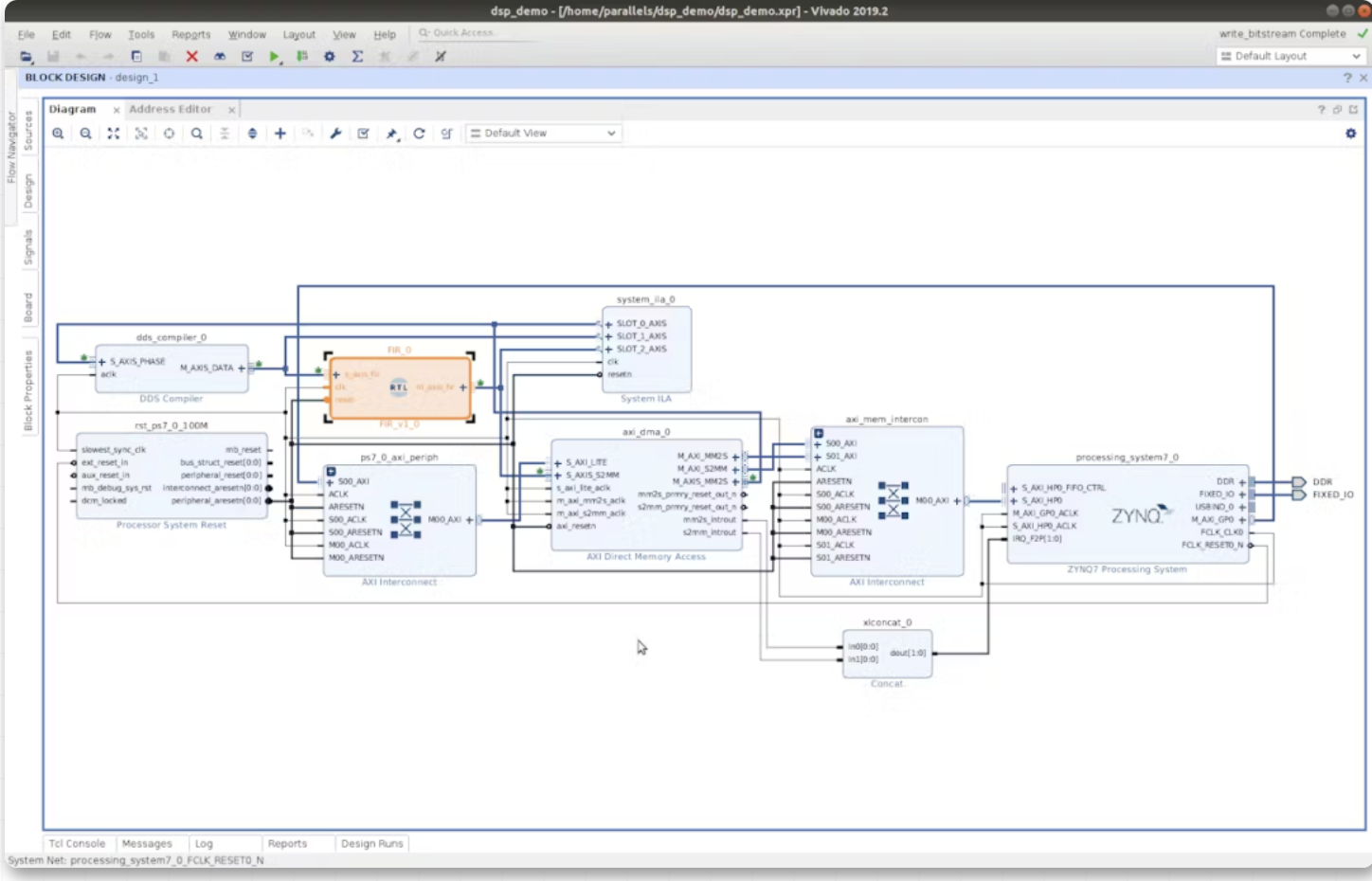

当在目标 FPGA 芯片中布局和布线时,首先在 Vivado 中确定时序要求.

2023-06-20 17:31:27 389

389

静态时序分析(Static Timing Analysis, 以下统一简称 **STA** )是验证数字集成电路时序是否合格的一种方法,其中需要进行大量的数字计算,需要依靠工具进行,但是我们必须了解其中的原理。

2023-06-27 11:43:22 523

523

引言 在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行 静态时序分析 ,即 在最坏情况下检查所有可能的时序违规路径,而不需要测试

2023-06-28 09:38:57 714

714

本文主要介绍了静态时序分析 STA。

2023-07-04 14:40:06 528

528

正如“聚合”的意思(字典)“两个或多个事物聚集在一起的发生”。所以我们可以假设它也与 2 个时钟路径聚集在一起有关。 (了解时钟路径请参考另一篇博客-静态时序分析基础:第1部分“时序路径”)

2023-08-08 10:31:44 524

524

。用通俗的话来说,射频相当于话筒,基带则相当于发出的声音。 射频芯片是专门负责处理高频信号的芯片。在无线通信系统中,原始的电信号(基带信号)首先经过数字信号处理器(DSP)的处理,然后经过数字模拟转换器(DAC)转换

2023-10-25 15:02:29 1748

1748 在手机终端中,最重要的核心就是射频芯片和基带芯片。射频芯片负责射频收发、频率合成、功率放大;基带芯片负责信号处理和协议处理。那么射频芯片和基带芯片是什么关系?

射频芯片和基带芯片的区别主要

2024-01-06 16:16:17 1506

1506

电子发烧友App

电子发烧友App

评论