一、简介 RapidIO是由Motorola和Mercury等公司率先倡导的一种高性能、 低引脚数、 基于数据包交换的互连体系结构,是为满足和未来高性能嵌入式系统需求而设计的一种开放式互连技术标准

2020-11-26 10:42:37 3561

3561

`xilinx公司的rapidio接口定义具体的核引脚定义,比如什么用,时序等。接口见附件图1~图4.`

2016-10-28 22:01:48

有哪些方法能提高2.4G 单面板的性能, 增强抗干扰能力和传输距离等?

2016-11-11 13:51:47

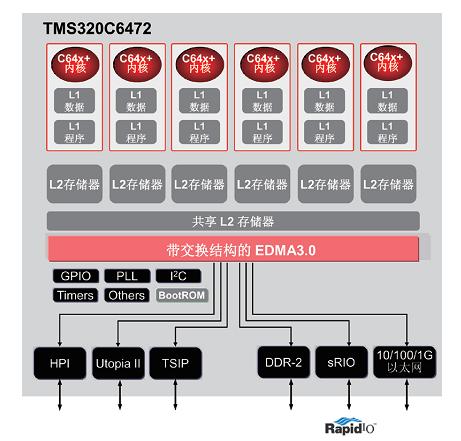

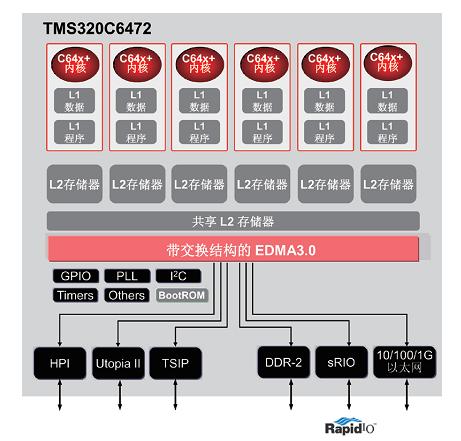

可能隐含BUG)如何充分使用八核的性能?如何对八核进行调试、监控?复杂的系统中,几十个DSP核如何进行简单、高效的通信C6678 多核 DSP 软件 开发难点共享外设:与C64x单核DSP相比,芯片

2018-06-20 01:39:59

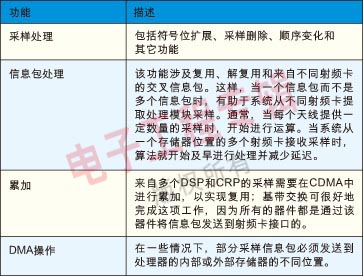

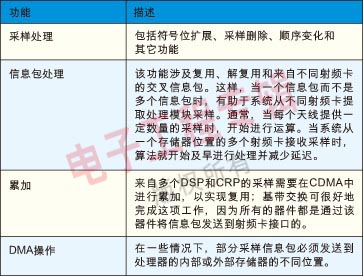

FPGA在高性能数字信号处理领域越来越受关注,如无线基站。在这些应用中, FPGAs通常被用来和DSP处理器并行工作。有更多的选择当然是好的,但这也意味着系统设计师需要一个确切的FPGAs及高端DSP信号处理器性能参数图。不幸的是,常用的参数图在这种情况下都是不可靠的。

2019-09-25 08:17:27

为设计提供可编程逻辑解决方案所固有的灵活性特点,以及定制门阵列(如ASIC)解决方案所具有的高性能及集成度。 增强DSP处理能力的传统方法是采用多个处理器。选择此类方案的缺点是成本昂贵,需要众多附加

2011-02-17 11:21:37

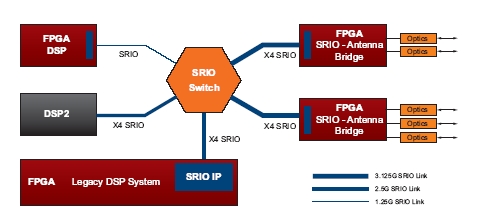

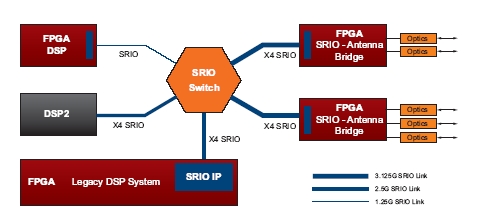

多;主从模式接口,不支持对等传输。另外,DSP不能直接进行背板传输。使用SRIO(Serial RapidIO)则可有效的解决这些问题,大大提高无线基站的互连性能。图8显示了一种无线基站基带互连框图

2016-12-09 11:24:30

本人在北京工作7年以上,从事FPGA外围接口设计,非常熟悉Serial RapidIO协议,设计调试了多个基于Serial RapidIO接口的DSP和PowerPC信号处理卡.本人非常

2014-08-23 13:27:47

性能中传输研究和对速度快速提高所致。而且主动减振系统和VoIP也伴随DSP性能提高而开发出来。DSP架构中性能提高也促进了蜂窝电话和DSL发展。这些发展进一步降低了便携系统设备功耗,同时也为多信道系统

2011-05-27 10:18:02

`Spartan-3ADSP现场可编程门阵列系列(FPGA)解决了大多数高容量的设计难题,成本敏感的高性能DSP应用。这两人家庭提供的密度从1.8到3.4百万系统门,如表1所示。Spartan-3A

2021-04-26 15:07:49

最先进的高性能逻辑架构之外,Virtex-5 FPGA包含许多硬IP系统级块,包括功能强大的36 Kb块RAM / FIFO,第二代25 x 18 DSP片,具有内置数字控制阻抗的SelectIO

2021-04-26 15:41:14

(HKMG)工艺技术之上,可实现I / O带宽2.9 Tb / s,200万逻辑单元容量和5.3 TMAC / s DSP极大地提高了系统性能,而功耗却降低了50%7系列FPGA功能摘要•基于可配置为

2021-04-13 14:27:32

fpga+dsp 4路ad采集系统,you尝,rapidio pcieddr3 各种高速外围接口 代码有偿。qq2715957785

2018-02-24 08:34:21

定的绑定。由于有两种 Rapidio 发射器类型(长跑和短跑),我们猜测将发射器配置为长跑可能会提高信号质量,但不幸的是我们没有找到合适的寄存器,顺便说一句,我们使用 MPC8569。我的问题:是否有配置 Rapidio 变送器类型的寄存器?或者是否有一些与硬件设计相关的问题可能会导致我们的问题?

2023-03-16 08:37:11

关于FPGAs的DSP性能分析

2021-05-07 06:12:50

多核处理器是最近快速发展的电子器件,单个芯片内集成了多个同构或者异构的处理器,使得其计算处理能力得到较大幅度的提高。DSP处理器由于其具有较高的数字处理能力,得到较广泛的应用。多核DSP芯片以目前

2021-02-02 07:53:47

通过阵列天线后产生不同的阵列响应,智能天线接收系统可采取一定的算法(可在射频、中频或基带实现)把不同方向的信号区分开来,从而降低干扰,提高系统性能。因此阵列结构对智能天线系统性能起着重要的影响。[hide][/hide]

2009-07-29 08:54:14

提高48V配电性能的方法有哪些分比式电源架构

2020-11-23 14:29:09

提高 48V 配电性能

2021-03-16 06:36:28

如何提高FATFS SD性能?

2022-02-11 06:28:46

本文基于Viitex-5 LX110验证平台的设计,探索了高性能FPGA硬件系统设计的一般性方法及流程,以提高FPGA的系统性能。

2021-04-26 06:43:55

如何提高VMMK器件的性能?

2021-05-21 06:35:39

无论您的系统是用于无线通信、雷达,还是 EMI/EMC 测试,系统的性能水平都是由其中的天线决定的。系统天线的性能决定了系统的整体质量,最终可能会影响整个程序或应用软件的效率。本文介绍了 5 个旨在帮助您提高天线性能的关键要点。

2021-02-24 07:24:14

元器件的合理布局提高敏感器件的抗干扰性能

2021-02-19 07:05:29

自适应电缆均衡器是什么?自适应均衡器设计面临哪些技术挑战?如何提高自适应均衡器的性能?

2021-05-18 06:04:25

我正在使用 iMX8mmini 并尝试提高 GPU 性能。使用下面的命令我发现当前 GPU 以 500 MHz 的频率运行。根据数据表或设备树节点,GPU 以 800 MHz 的标称频率运行(最大

2023-04-18 07:17:15

要跟上日益提高的性能需求,还得注意保持成本低廉有效利用基于串行RapidIO的FPGA作为DSP协处理器就能达到这些目的。那么,我们该怎么做呢?

2019-08-07 06:47:06

如何去提高语音引擎设计的质量和性能?

2021-05-31 06:35:46

随着通讯系统的数据处理量日益增大,过去总线形式的体系结构逐渐成为约束处理能力进一步提升的瓶颈。本文首先简单介绍了嵌入式设计中总线结构的演化过程,从而引出新一代点对点串行交换结构RapidIO。

2019-11-01 06:05:21

最大限度提高Σ-Δ ADC驱动器的性能

2021-01-06 07:05:10

我用ise产生了rapidio的核,然后做功能仿真没有问题,我把自己的逻辑与核结合起来后做功能仿真,却发现端口不能初始化了,具体情况是port_initialized变成了不定值。求帮忙!!

2019-05-16 09:39:16

怎么使用PlanAhead Design工具提高设计性能?

2021-04-26 06:00:22

您可以显著提高无线系统中信号处理功能的性能。怎样提高呢?有效方法是利用FPGA结构的灵活性和目前受益于并行处理的FPGA架构中的嵌入式DSP模块。

2019-08-15 07:51:10

随着通讯系统的数据处理量日益增大,过去总线形式的体系结构逐渐成为约束处理能力进一步提升的瓶颈。本文首先简单介绍了嵌入式设计中总线结构的演化过程,从而引出新一代点对点串行交换结构RapidIO。

2019-09-02 07:10:22

本文设计了一套基于DSP的阵列声波信号采集与处理系统,此系统将作为正在研制的阵列声波测井仪中的一部分,应用于油田勘探中。

2021-05-31 06:26:35

嗨,我有一个ML605板和一块使用RapidIO协议的DSP板。该板有两个FMC连接器(HPC和LPC)和一个PCIe接口,我需要4个万兆收发器(MGT),PCIe和FMC HPC都有8个(LPC

2019-08-29 10:33:02

之前做ARM软件开发,现在转DSP软件开发,特别对DSP性能,内存利用难以把控,论坛上硬件资料偏多,谁有软件方面资料,特别关于性能优化的,多谢。

2013-08-17 21:33:47

热量是如何产生并影响LED的?如何提高LED性能?

2021-06-15 09:02:39

近来,Altera公司推出业界首款浮点FPGA,它集成了硬核IEEE754兼容浮点运算功能,提高了DSP性能、设计人员的效能和逻辑效率。据悉,硬核浮点DSP模块集成在

2019-07-03 07:56:05

实验。本文提出了一种新型的碳纳米管天线阵列研究方法,即采用传统微带天线和印刷八木天线分别加载碳纳米管束的方法对纳米管阵列进行空间馈电并进行了实验测试,测试结果表明加载碳纳米管阵列后微带天线辐射性能有明显改变。

2019-05-28 07:58:57

如何提高系统的ADC的性能?

2019-09-06 05:55:37

讨论一下编程风格与技巧是怎样提高设计性能的?

2021-05-07 06:31:21

的时候用的是默认32位地址。我想请问一下,如果要利用srio收发34位地址,DSP端keystone_srio的程序要做什么改进?我看了keystone_srio初始化代码,它的PE_LL_CTL

2018-12-28 11:08:14

在布板时,如果线密,过孔就可能要多,当然就会影响板子的电气性能,请问怎样提高板子的电气性能?

2019-06-25 04:08:22

在可编程逻辑中实现可配置软核处理器有哪些好处?怎样建立起处理器和主机pc之间的通信?怎样用DSP功能去提高图像处理?

2021-04-14 06:52:33

请问有什么策略可以提高芯片的性能?

2021-06-23 13:08:50

调试并行RapidIO设计

2019-07-17 09:11:20

路LED的智能控制,提高车用LED的工作效率和可靠性,可以广泛应用于车用LED控制领域。【关键词】:传感器阵列;;LED;;智能控制【DOI】:CNKI:SUN:GGYT.0.2010-08-009【正文

2010-05-28 13:39:17

近年来变频控制因其节能、静音及低颤动而得到广泛的关注和应用,基于ARM/DSP 的高性能驱动方案为中大功率三相电机提供了高性能、多控制方式的解决方案,其主要应用于对电机控制的性能、实时性方面要求比较

2019-07-09 08:24:02

有哪些新型可用于基带处理的高性能DSP?性能参数如何?

2018-06-24 05:20:19

高级处理器特性能否提高编码效率?

2021-04-26 06:41:08

阵列通道幅相不一致性严重影响测向性能。基于辅助源的相关校正理论,研究了通过在天线馈电口输入辅助信号,再对信号求相关来实现对阵列通道不一致性的校正;并分析了基

2009-03-04 22:23:07 21

21 针对传统总线PCI存在的问题,提出异步FIFO存储转发模式的串行RapidIO-PCI转接桥方案,介绍RapidIO高速总线的体系结构及其性能优势,根据PCI和RapidIO协议,给出转接桥关键部分结构的设

2009-04-01 09:34:02 33

33 基于DSP的多传感器阵列数据采集与处理试验平台

2009-05-08 17:10:52 17

17 赛灵思宣布开始向市场交付针对高性能数字信号处理(DSP)而优化的65 nm Virtex-5 SXT现场可编程门阵列(FPGA)器件的首批产品。SXT平台创造了DSP性能的行业新纪录--550MHz下性能达352 GMAC

2009-11-28 14:08:02 23

23 为了在实验室中获得短波天线阵列信号,应用DSP芯片和DUC芯片(数字上变频器)设计了一个实用电路短波阵列信号发生器,模拟实现了短波九元天线阵的多种阵型、不同来波方向及存在

2009-12-03 16:44:08 17

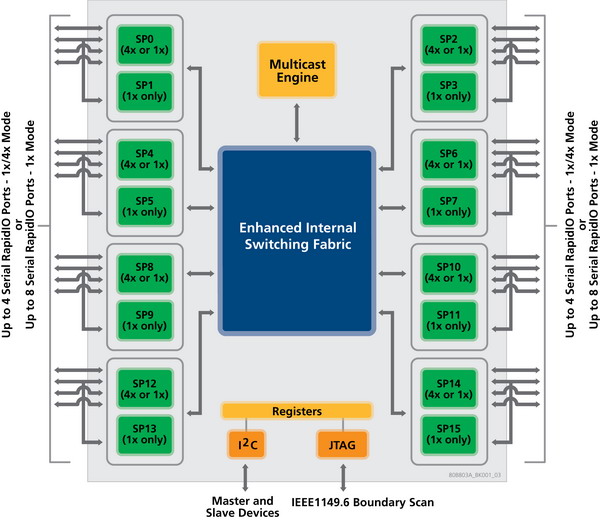

17 RapidIO 互连构架是一个开放的标准,可应用于连接多处理器、存储器和通用计算平台。本文简要介绍了基于Tundra 公司TSI568 芯片的RapidIO 交换模块的设计原理和实现方法,并对一些

2010-01-06 16:47:48 40

40 本文首先简单的介绍了总线的发展,从而引出一种新型的串行点对点交换结构RapidIO。DSP 在高性能处理系统中的重要性毋庸置疑,但是目前的很多DSP 并没有RapidIO接口。本文提出了

2010-01-25 14:25:19 32

32 前言 声源定位追踪模组AR-1105是德宇科创采用最新的DSP音频处理器集成麦克风阵列声源定位追踪技术进行研发,模组具有全硬件集成.体积小巧,外围电路简洁,无需软件调试,易上手等优点的情况下同时保持反应灵敏,定位准确等特性. 总结

2023-09-02 09:32:13

分析当前高速互连网络中同时存在的TCP/IP, GAMMA, InfiniBand, SCI 等技术的实现机制,介绍RapidIO 高性能总线技术。研究RapidIO 协议和MPC8548 处理器的相关技术,提出在RapidIO 高速互连网

2010-09-22 08:35:11 20

20 传统嵌入式应用设计通常是将程序直接固化到DSP内部的Flash存储器运行,程序运行效率较低,不能充分发挥DSP的性能。为克服这些缺点,解决嵌入式应用程序在Flash存储器直接运行所

2010-12-27 15:34:48 25

25 首款串行RapidIO 2.1 IP 解决方案(Altera)

Altera 公司 宣布推出业界首款支持 RapidIO® 2.1 规范的知识产权 (IP) 内核。Altera 的串行 RapidIO IP 内核可支持多达四条通道,每条通

2009-11-18 15:50:59 890

890 光伏阵列的性能测试

1.组装工艺质1检查

对于光伏电池板和光伏阵列的组装工艺检查主要是检查其外观质量

2009-12-19 08:54:58 3711

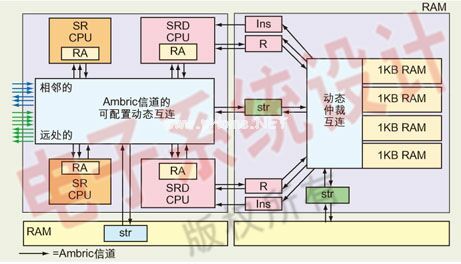

3711 6核片上DSP阵列提高平台整体性能

DSP的新走向是业界十分关心的问题。曾经对DSP的需求是强调性能和频率。目前时钟频率已经向1G以上突破,这样的情况下如何保持产

2010-01-06 14:12:49 570

570

串行 RapidI 高性能嵌入式互连技术

摘要

串行RapidIO针对高性能嵌入式系统芯片间和板间互连而设计,它将是未来十几年中嵌入式系统互连的最佳选择。

2010-02-25 16:45:04 1022

1022

基于FPGA实现DSP与RapidIO网络互联

1. 引言

随着通讯系统的数据处理量日益增大,过去总线形式的体系结构逐渐成为约束处理能力进一步提升的瓶颈。本文首

2010-02-25 16:46:46 868

868

全球首屈一指的RapidIO IP解决方案

RapidIO最早是由美国Mercury Computer systems公司(美国水星计算机系统公司www.mc.com)为它的计算密集型信号处理系统自行开发的总

2010-03-01 11:05:21 882

882 串行RapidIO交换器的应用优势

EMIF6? 是由 Texas Instruments 开发的一款专利接口,在业内应用多年,反响良好。但是,EMIF6? 现正用于从未尝试的 DSP 至 DSP 连接等应用。本文

2010-03-03 15:54:10 795

795

采用串行RapidIO连接功能增强DSP协处理能力

目前,对高速通信与超快计算的需求正与日俱增。有线和无线通信标准的应用随处可见,数据处理架构每天都在扩展。较为普

2010-03-03 16:01:25 1134

1134

利用串行RapidIO交换机设计模块化无线基础系统

无线服务提供商期望引进的无线基础系统具有更高的性能以及更低的成本,这将推动对标准的或现成元件不断提高的

2010-03-09 12:05:10 1033

1033

IDT公司宣布,推出基于其业界领先Serial RapidIO 1.3交换器的全新Serial RapidIO Gen2交换器系列。这些新的交换器支持Serial RapidIO 2.1标准,利用了来自IDT CPS和TSI产品线的一流技术。

2010-06-28 08:33:31 1721

1721 RapidIO总线的出现及其体系结构和应用

传统总线多采用并线总线的工作方式,这类总线一般分为三

2010-12-06 10:16:37 2069

2069 摘要:从应用角度介绍了ADSP21160 DSP芯片的基本性能,并用ADSP21160实现了基本的阵列信号测向算法-MUSIC算法着重讨论了如何利用ADSP 21160的结构和开发环境来提高程序的执行效率,满足系统设计的要求。 关键词:SHARC DSP;阵列信号处理;MUSIC;测向算法

2011-02-28 23:59:15 33

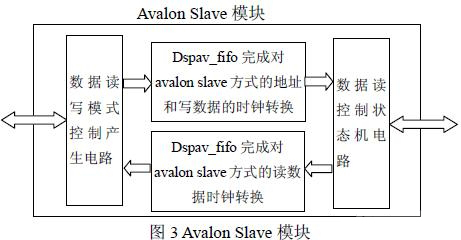

33 该方案采用Altera公司的IP核和Cyclone系列FPGA,建立了串行RapidIO(SRIO)接口通信系统,并对其功能进行验证。详细分析了RapidIO应用系统及其验证模型的功能结构和运行原理,为提高嵌入式

2011-12-23 14:47:22 38

38 介绍了RapidIo总线的特点,以及RapidIo总线初始化过程中面临的系统网络结构探测和最短路径路由选择问题。针对该问题,本文研究了深度优先(DFS)网络拓扑探测方法在RapidIo总线枚举过

2013-03-13 16:15:14 74

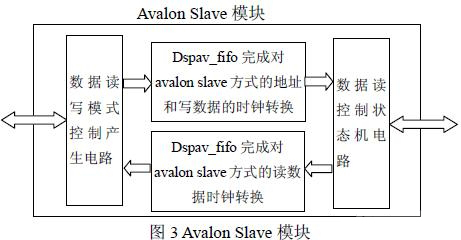

74 基于串行RapidIO的Buffer层设计_任雪倩

2017-01-07 21:28:58 0

0 威世-用薄膜电阻阵列提高反馈电路和分压器的精度

2017-01-24 16:00:51 8

8 基于EP2C35的DSP阵列板通信接口设计与实现

2017-10-19 14:12:34 14

14 摘 要:本文分析了传统的多个DSP 的各种互联的方法,提出将串行RapidIO 协议,这种基于开关的、点对点的互连方法作为基带数据处理中的互连方案,可以减少成本,并且提供高带宽下低延时的双向通信

2017-10-21 09:29:51 1

1 您可以显著提高无线系统中信号处理功能的性能。怎样提高呢?有效方法是利用FPGA结构的灵活性和目前受益于并行处理的FPGA架构中的嵌入式DSP模块。

2018-07-17 11:48:00 710

710

高性能 DSP 上的串行 RapidIO 接口

2018-06-12 03:44:00 3784

3784 运行。这种运行方式在传统嵌入式应用设计中很有效,但在一些算法比较复杂、系统响应要求快速、通讯任务比较繁重的嵌入式应用中,这种运行方式会导致控制系统响应迟缓、通讯异常、I/O操作缓慢等问题。针对这些情况,提出一种新的解决方案,来提高DSP代码运行性能。

2019-08-07 08:12:00 2126

2126

srio_example_top_primary,它代表请求方的RapidIO设备;另一个例子设计顶层叫做srio_example_top_mirror,它代表响应方的RapidIO设备。

2022-12-19 10:33:51 1190

1190 RapidIO互连架构,与目前大多数流行的集成通信处理器、主机处理器和网络数字信号处理器兼容,是一种高性能、包交换的互连技术。它能够满足高性能嵌入式工业在系统内部互连中对可靠性、增加带宽,和更快的总线速度的需求。

2023-01-09 09:25:20 751

751 RapidIO 与传统嵌入互连方式的比较 随着高性能嵌入式系统的不断发展,芯片间及板间互连对带宽、成本、灵活性及可靠性的要求越来越高,传统的互连方式,如处理器总线、PCI总线和以太网,都难以

2023-02-02 14:15:05 356

356 Serial RapidIO Development Platform (SRDP2) 原理图

2023-05-15 19:19:49 0

0 Serial RapidIO Development Platform (SRDP2) 原理图

2023-07-11 20:31:35 0

0 RapidIO交换芯片是一种基于RapidIO协议的专用交换芯片,它能够实现高速、低延迟的数据传输和交换,广泛应用于嵌入式系统、数据中心、网络通信等领域。RapidIO协议本身是一种基于包交换的互连技术,具有高速、高效、可靠等特点,因此RapidIO交换芯片在数据传输和交换方面具有很高的性能优势。

2024-03-16 16:40:09 1532

1532

电子发烧友App

电子发烧友App

评论