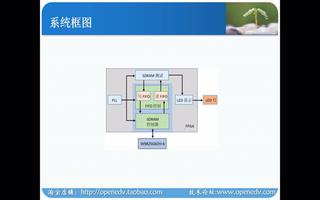

介绍了一种应用于通用微处理器系统中的SDRAM与双口RAM之间的数据转移接口控制电路,由VHDL语言设计,用Xilinx公司4000系列FPGA实现,目前该电路硬件实现和微处理器系统已经通过验证,证

2011-11-11 09:43:14 1415

1415

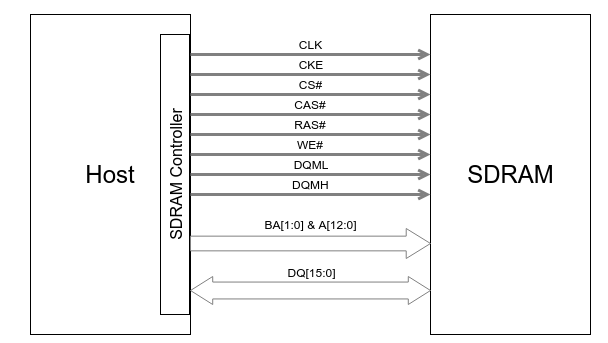

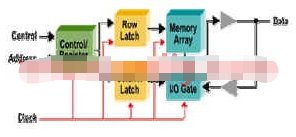

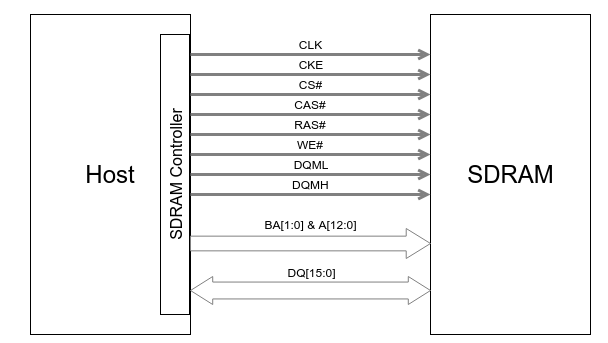

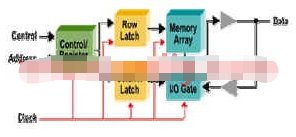

本文则以 SDR SDRAM 为例,描述 DRAM Device 与 Host 端的接口,以及其内部的其他模块,包括 Control Logic、IO、Row & Column Decoder 等。

2020-09-22 15:34:59 4192

4192

谁有SDRAM的基于modelism的读写仿真图,发给我一份,急用,在此多谢了,qq:847192168

2014-06-08 08:17:57

~133MHz,单片容量可以达到64Mbit或更高,因此在需要高速、大容量存储器的系统中得到广泛应用,如应用在目前的计算机内存中。但是SDRAM的控制比较复杂,其接口不能直接与目前广泛应用的普通微处理器如

2019-06-10 05:00:08

SDRAM的控制原理是什么?SDRAM有哪些控制命令呢?SDRAM的读写流程有哪些呢?

2021-10-22 08:31:37

SDRAM的基本工作原理是什么SDRAM的基本读写操作步骤是什么一种简单的通用SDRAM控制器的实现

2021-05-10 06:26:44

“STM32F429等系列的芯片增加了SDRAM接口,扩展的内存在做人机界面等应用时是非常有用的。”1.SDRAM硬件接口SDRAM(Synchronous Dynamic R...

2022-01-20 08:28:51

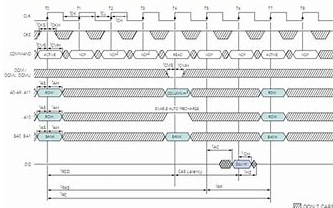

;如果上一次执行了写操作,则此次执行读操作。如果不是同时出现读写请求,则是什么请求就执行什么操作。2)采用全页模式的读写操作,该模式在读、写完成时,需要给出预充电命令才能结束。3)刷新请求始终优于读、写请求。DDR的时序与SDRAM是相似的,学好SDRAM后,理解DDR2和DDR3就非常容易了。

2017-11-23 11:02:27

请教大家,下图红圈处是我用的sdram。请问sdram的时钟可调吗?是不是只要不超过最大时钟频率就可以呢。我用100MHz的读写没问题。用125MHz或150Mhz就出现问题了。不知道是需要调整

2013-06-27 14:25:34

SDRAM的读写程序怎么写啊。求帮忙解决下,一下附上资料,

2013-07-02 15:58:54

的应用也越来越普遍。E1是我国电信传输网一次群使用的传输标准,速率是2.048 Mb/s。实现多路接口与E1协议的相互转换,将可以把多种设备同时连接至高速的E1线路。本文基于FPGA(Field

2019-06-10 05:00:04

摘要:介绍SDRAM的主要控制信号和基本命令时序,提出一种应用于解复用的支持多路读写的SDRAM接口设计,为需要大容量存储器的电路设计提供了新思路。关键词:SDRAM 解复用 接口 存储器

2018-12-03 15:20:48

该文档为基于FPGA的多路模拟数据采集接口设计讲解文档,介绍一种基于 8,RQ 的多路模拟数据采集接口的设计方案。该方案使用Max1281 作为模数转换芯片,在 APA150 FPGA 中设计和实现了相关的接口控制、配置和数据存储模块;给出了系统设计框图、FPGA开发要点和仿真波形。

2018-09-21 14:37:00

ADI TS201的RS422串口通信 和与SDRAM读写的程序交流

2018-10-30 09:18:47

本帖最后由 eehome 于 2013-1-5 10:06 编辑

FPGA读写SDRAM的实例

2012-08-15 16:38:04

,SDRAM 由于其性能价格比的优势,而被 DSP 开发者所青睐。DSP 与 SDRAM 直接接口是不可能的。FPGA(现场可编程门阵列)由于其具有使用灵活、执行速度快、开发工具丰富的特点而越来越多地出现在

2020-04-23 08:00:00

STM32H7系列,FMC接片外SDRAM,连续读写测试,每次读写间加一个延时不会报错,但去掉延时,连续读写就读写不一致了?

请教大神是哪里配置出了问题么?

另外还有个奇怪的现象。。。在循环的最后

2024-03-11 08:07:46

,TFT彩屏和SDRAM都是板载外设,两者相比SDRAM更实用,用途更广泛,对板子接口要求更多,因为高级的开发板才有SDRAM,而TFT彩屏的上述特点都与SDRAM相反,而研究耗费的时间却更多。 下面

2017-03-05 12:25:51

请问各位大虾 SDRAM是如何进行读写的,如何将文件数据存储到SDRAM中 网上没找到这方面的资料 求各位大虾帮忙

2013-04-14 10:09:13

基于FPGA的SDRAM控制器设计(三)读写作者:小周 本文为明德扬原创及录用文章,转载请注明出处! SDRAM控制器设计的主要功能是能对SDRAM进行读写操作,本工程实现了SDRAM的初始化、自动

2020-04-23 11:31:47

互动,大家可以给公众号的后台发送自己对于读写FIFO作用的理解。当然还是有很多网友给后台发送过自己的理解,正确率应该是60%左右。使用读/写FIFO的原因:1.写SDRAM, 串口发送4个字节的数据所需

2017-05-08 22:38:37

第1节 SDRAM读写控制器--作者:小黑同学本文为明德扬原创及录用文章,转载请注明出处!1.1 总体设计1.1.1 概述同步动态随机存取内存(synchronousdynamic

2020-10-15 15:16:02

如题,用的是xilinx的virtex 4的板子。现要向DDR SDRAM读写数据,DDR SDRAM的地址该怎么写?

2013-11-05 16:01:53

两片 MT48LC32M16的SDRAM 操作读写问题 ??? 描述如下:#define SDRAM_BASE_ADDR((uint32_t)0xC0000000)// CS01、按照 32位的读写

2019-02-19 07:00:08

用Altera_Cpld作了一个186(主CPU)控制sdram的控制接口, 发现问题:要使得sdram读写正确, 必须把186(主CPU)的clk送给sdram, 而不能把clk经cpld的延时

2019-09-18 05:02:19

课程介绍1. SDRAM文档的阅读和理解2. SDRAM的功能汇总3. SDRAM的实现架构4. SDRAM接口的模块划分5. SDRAM的时序分析和约束练习3说明视频,转码问题,上传不了。需要完整

2022-02-15 10:26:33

大虾们好,最近在使用 stm32f7x单片机对sdram 读写 ?? 出现如下情况:图片1,读写正常,单个字节读写,见图片描述一写一读正常,这说明硬件木有什么问题吧 ??下面的连续写或者连续读都不

2018-11-15 08:55:34

自己做的DSP开发板,在DSP对SDRAM进行写操作的时候,发现一个问题:当往SDRAM中写的地址数超过128个的时候,再寻址的时候第8根地址线会乱掉,导致地址错位,此时,数据线第8根电压也反向了

2014-04-23 20:14:39

的mcuFIFO中,(sdram读写频率为90MHZ),数据经过MCUfifo后输出DATAOUT(8位数据),得到的数据存在以下问题:

2014-09-10 19:49:20

分享一款不错的SDRAM接口的VHDL设计

2021-05-08 06:04:27

和刷新,同时控制FIFO的读、写操作;FIFO是DSP与SDRAM之间的数据通道,深度为256,其作用是充分利用SDRAM的突发读写功能,提高系统速度,同时简化DSP软件设计。 3.1 命令接口和刷新

2018-12-07 10:35:02

纯逻辑实现SDARM控制器工程说明本项目展示如何用“至简设计法”设计SDARM,具体功能要求如下:1)读写仲裁机制:当同时出现读写请求时,如果上次执行了读操作,则此次执行写操作;如果上一次执行了写

2017-08-02 17:43:35

上一期介绍了如何使用语音助手控制多路接口,这一期将为大家介绍如何使用官方提供的APP控制多路接口。1、APP的下载地址,以及使用方法可以参考此处,笔者为大家找了一个讲的很详细的网页。2、关于

2021-11-03 08:51:50

如何实现Reg istered SDRAM接口电路的设计?Reg istered SDRAM的工作原理是什么?Registered SDRAM接口电路的原理设计与布局布线规则是什么?

2021-04-12 07:10:21

只是读写检测,没有硬件sdram接口的f103可以测试吗

2023-09-21 06:38:25

这样的,我在跑100MHz读写sdram的时候,经常出现sdram工作失常的现象。我怀疑是sdram相移引起的。请问该如何调整呢?非常感谢!

2014-01-02 17:08:19

篇有关SDRAM接口读写时序的文章,希望能够帮助不了解的同学对SDRAM数据读写有更进一步的认识。 一、SDRAM初始化在SDRAM内部有一个逻辑控制单元,并且有一个模式寄存器为其提供控制参数。每次

2020-01-04 19:20:52

实验中,各端口信号的管脚分配如下表所示:表 33.3.1 SDRAM读写测试实验管脚分配程序设计在本次实验中,由于SDRAM的控制时序较为复杂,为方便用户调用,我们将SDRAM控制器封装成FIFO接口

2020-08-17 15:25:11

我在做一个FPGA的片外SDRAM读写功能的开发,参考了特权老师的verilog代码。背景:片外SDRAM采用的是HY57V561620FT-HI,模块当中利用100K时钟产生数据流,利用20M时钟

2018-04-24 10:38:29

如题.......最近移植特权的sdram,怎么调都不通,而且特区的例子带了fifo,看起来异常复杂也不好仿真,所以求一个能用的单独读写sdram特定地址的范例,急求谢谢

2015-08-11 08:54:04

的时钟双沿读写嘛,速度这不就一下翻番了。很对,但是再往深入去,你思考过吗?难道DDR内部寻址时数据也是双沿读写么?非也DDR SDRAM外部的数据总线接口位宽,一般是8位或者16位。而它左边那个红圈里

2014-12-30 15:22:49

最近在写ADC采集程序,将ADC采集的数据存储至SDRAM中去。我使用的ADC是20Msps的,所以每个数据是50ns的占留时间。SDRAM使用的是100MHZ,这个是SDRAM的操作时钟频率,但是不知道读写一个数据SDRAM要花多少个时钟呢??应该这个就是SDRAM的读写速率吧。

2019-04-23 23:38:22

用C5509A读写外部SDRAM,例程里面souraddr =(int *)0x40000;deminaddr = (int *)0x41000;我把目的地址改为0x50000,发现从0x40000

2018-07-31 06:23:46

分析了IDE接口硬盘控制寄存器模型;论述了IDE接口硬盘的读写几项技术;给出了设计硬盘克隆软件的思想和方法,方法针对硬盘物理扇区进行读写,与硬盘上安装的具体操作系统

2009-02-22 23:47:29 76

76 针对SDRAM 控制器读写数据块访问延时长、速度慢的问题,提出时间隐藏技术,将其应用于SDRAM 控制器的设计,采用FPGA实现。实验结果表明,时间隐藏技术有效缩短了数据块读写访问

2009-03-25 09:00:34 15

15 介绍基于现场可编程门阵列(FPGA),利用VHDL 语言设计实现MMC2107 与SDRAM 接口电路。文中包括MMC2107 组成结构、SDRAM 存储接口结构和SDRAM 控制状态机的设计。

2009-05-15 14:47:29 24

24 SPI接口读写串行EEPROM:93C46为采用3线串行同步总线SPI接口方式的EEPROM,其芯片引脚名称和功能描述如图1-1:

2009-09-19 11:39:27 89

89 SDRAM设计详细说明

完成SDRAM的上层驱动设计,对SDRAM读写、管理无误,与其他模块的接口正确。

口令:MMCTEAM

SDRAM的工作原理

2010-04-22 14:02:57 0

0 基于FPGA的高速SDRAM控制器的视频应用

0 引言 SDRAM(同步动态存储器)是一种应用广泛的存储器,具有容量大、数据读写速度快、价格低廉等优点,特别适

2009-11-04 09:56:20 847

847 为了降低DSP外部SDRAM存储系统的功耗,针对DSP访问片外SDRAM的功耗来源特点,提出了基于总线利用率动态监测的读写归并方案。该方案动态监测外部存储器接口(EMIF)总线的利用率,根据总线利用率的不同选择开放的页策略、封闭的页策略或休眠模式;设计了简化

2011-01-14 17:40:12 50

50 USB接口的彩电存储器读写器读写软件

2011-03-19 11:00:11 1613

1613 SDRAM 以其高速和大容量的优点获得了极大的应用,但是其接口与目前广泛应用的微处理器系统不兼容,介绍了用 VHDL 语言实现的SDRAM与RAM之间的接口控制电路,从而将SDRAM应用到微处理器

2011-06-01 15:29:15 57

57 介绍如何利用EM Microelect ronic 公司的射频卡读写基站芯片EM4094 和Arasan 公司的SDIO 接口芯片AC2200 来构建一种基于通用接口SDIO 的即插即用型的RFID 读写器,它可以在支持SDIO 接口的掌上电脑

2011-06-02 15:29:54 58

58 SDRAM存储芯片拥有快速读写的性能,可以应用以回波模拟系统作为数据高速缓存器。SDRAM芯片是由SDRAM控制器控制的, SDRAM控制器有严格的控制时序和工作状态,可以使用有限状态机理论

2011-10-24 15:08:05 0

0 虽然目前SDRAM内存条价格已经接底线,内存开始向DDR和Rambus内存过渡。但是由于DDR内存是在SDRAM基础上发展起来的,所以详细了解SDRAM内存的接口和主板设计方法对于设计基于DDR内存的主

2012-01-05 16:21:11 247

247 使用功能强大的FPGA来实现一种DDR2 SDRAM存储器的用户接口。该用户接口是基于XILINX公司出产的DDR2 SDRAM的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,

2013-01-08 18:15:50 237

237 基于Xilinx的DDR2 SDRAM存储控制器的用户接口设计与仿真,本设计通过采用多路高速率数据读写操作仿真验证,可知其完全可以满足时序要求,由综合结果可知其使用逻辑资源很少,运行速

2013-01-10 14:12:45 2990

2990 介绍在 Nios II 中利用 SDRAM 控制模块实现对 SDRAM 存储芯片——

K4M561633G 的读写,通过本章,你能学到

(1)SDRAM 控制模块的使用。

(2)在 Nios II 中读写 SDRAM 芯片。

2015-12-14 15:40:33 0

0 华清远见FPGA代码-SDRAM读写控制的实现与Modelsim仿真

2016-10-27 18:07:54 26

26 作者:Steve Leibson, 赛灵思战略营销与业务规划总监 Adrian Cosoroaba和Terry Magee在本月MemCon上给出了关于DDR4 SDRAM接口的详细展示,该演示

2017-02-08 14:03:01 608

608 控制器,在介绍控制器的逻辑结构的基础上,对FPGA与SDRAM间数据通信进行了时序分析,实现SDRAM 带有自动预充电突发读写和非自动预充电整页读写。

2017-11-18 12:42:03 2054

2054

在很多通信芯片及系统的开发中,常常需要用到存储容量大、读写速度快的存储器。在各种随机存储器件中,SDRAM的价格低、体积小、速度快、容量大,是比较理想的器件。但是,与SRAM相比较,SDRAM的控制

2017-11-28 19:51:26 5

5 -ST固件库版本:1.5.1 【 !】功能简介: 读写板载的 SDRAM 芯片。 学习目的:学习STM32的FMC驱动及SDRAM内存器。 【*】注意事项: 无 【 !】实验操作: 电脑端使用串口调试

2017-12-13 15:13:37 18

18 所以SDRAM需要在电容的电量放完之前进行刷新;随机是指数据不是线性依次存储,而是自由指定地址进行数据的读写。” 这只是对SDRAM的概念介绍,下面再简单的看一下SDRAM的内部结构。

2018-03-29 09:30:54 7542

7542

问:如何操作SDRAM的自刷新命令而不影响正常读写操作? 众所周知,SDRAM从开始工作伊始,一直伴随着64ms刷新一遍的最基本规定(假设该SDRAM有4096行,那么必须大约15us的时间就要发出

2018-06-20 10:41:32 10512

10512

操作,设计了DDR SDRAM 的数据与命令接口。用控制核来简化对DDR SDRAM 的操作,并采用自顶至下模块化的设计方法,将控制核嵌入到整个数据采集系统的控制模块中,完成了数据的高速采集、存储及上传

2019-08-14 08:00:00 3401

3401

本文档的主要内容详细介绍的是FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文主要包括了:FPGA读写SDRAM的实例,SDRAM控制器核心介绍,系列SDRAM数据手册

2018-12-25 08:00:00 56

56 对于mig与DDR3/DDR2 SDRAM的读写时序我们不需要了解太多,交给mig就可以了。

2019-03-03 11:11:53 5640

5640

SF-EPIC开发板上使用的是三星SDR SDRAM (K4S641632)。由于控制SDRAM的读写不同于之前的很多简单接口实验(它们对时序的要求都不高,即便不做时序约束也无关紧要),SDRAM

2019-03-06 14:01:51 2

2 同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM)是有一个同步接口的动态随机存取内存(DRAM)。通常DRAM是有一个异步接口

2019-03-07 15:12:46 3025

3025 的。 SDRAM,同步的DRAM,即数据的读写需要时钟来同步。 DRAM和SDRAM由于实现工艺问题,容量较SRAM大。但是读写速度不如SRAM,但是现在,SDRAM的速度也已经很快了,时钟好像已经有150兆的了。那么就是读写周期小于10ns了。SDRAM虽然工作频率高,但是实际吞吐率要打折扣。

2019-04-01 16:24:29 35283

35283 SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。时钟被用来驱动一个有限状态机,对进入的指令进行管线(Pipeline)操作。这使得SDRAM与没有同步接口的异步DRAM(asynchronous DRAM)相比,可以有一个更复杂的操作模式。

2019-09-12 07:04:00 1896

1896

SDRAM从发展到现在已经经历了五代,分别是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代,DDR4 SDRAM。

2019-09-12 07:02:00 2009

2009

DDR2 设备概述:DDR2 SDRAM接口是源同步、支持双速率传输。比如DDR SDRAM ,使用SSTL 1.8V/IO电气标准,该电气标准具有较低的功耗。与TSOP比起来,DDR2 SDRAM的FBGA封装尺寸小得多。

2019-06-22 10:05:01 1793

1793

采用单端(Single-Ended)时钟信号,第二代、第三代与第四代由于工作频率比较快,所以采用可降低干扰的差分时钟信号作为同步时钟。SDR SDRAM的时钟频率就是数据存储的频率,数据读写速率

2020-04-03 16:04:01 1489

1489 DDR SDRAM的原理及特点:DDR SDRAM不需要提高时钟频率就能加倍提高SDRAM的速度,因为它允许在时钟脉冲的上升沿和下降沿读写数据。至于地址和控制信号,还是跟传统的SDRAM一样,在时钟的上升沿进行传输。

2020-08-10 17:33:21 603

603

SDRAM 是一种 RAM 类型的易失性存储器件,因其具有较大的容量和相对较低的价格在嵌入式系统中应用广泛。

2020-09-01 10:40:23 7162

7162

平衡。这样必须有一套合理多通道复用仲裁方法,达到整个数据存储效率最大化,用最小的存储空间达成最大的平均吞吐。 外部高速缓存的基本读写流程描述 外部缓存SDRAM (DDR)由于读写共用一个物理接口,所以读写需要分时产生,读时不能写

2020-11-20 15:54:54 635

635 针对SDRAM 操作繁琐的问题,在对SDRAM 存储器和全页突发式操作进行研究的基础上,提出一种简易SDRAM 控制器的设计方法。该设计方法充分利用全页式高效率存取的优点,对SDRAM 进行配置、全页突发式读写时,操作方便。在实现sDRAM 的快速批量存储方面,具有良好的应用价值。

2020-12-18 16:13:18 6

6 本文档的主要内容详细介绍的是使用FPGA读写SDRAM存储器的实例工程文件和程序免费下载。

2020-12-18 16:13:13 10

10 目前,在很多通信芯片及系统的开发中,常常需要用到存储容量大、读写速度高的存储器。在各种随机存储器件中,SDRAM 的价格低、体积小、速度快、容量大,是比较理想的器件。但是,与SRAM相比较

2021-06-30 09:16:47 2346

2346

FPGA作为ARM的SDRAM使用的LPC3250与FPGA接口程序(华为嵌入式开发工程师拉勾网)-FPGA作为ARM的SDRAM使用的LPC3250与FPGA接口程序,适合感兴趣的学习者学习,可以提高自己的能力,大家可以多交流哈

2021-08-04 12:09:30 22

22 SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。时钟被用来驱动一个有限状态机,对进入的...

2022-01-26 19:40:35 1

1 Bank/Row active 在对SDRAM进行读写时,需要先激活对应的bank和行,该命令用于选择一个bank的一行进行激活,以便接下来进行读写访问。

2022-12-28 14:34:16 540

540 电子发烧友网站提供《如何扩展USB接口进行对U盘的读写.doc》资料免费下载

2023-10-25 10:15:18 0

0 。 SDRAM是一种集成电路存储器,可以通过同步钟信号进行数据读写。与传统的静态随机存储器(SRAM)相比,SDRAM具有更高的存储密度和更低的成本。扩展SDRAM接口使得微控制器能够使用外部

2024-01-04 14:09:23 343

343

电子发烧友App

电子发烧友App

评论